工欲善其事,必先利其器。EDA职业尽管只占半导体工业全体商场份额的2%左右,可是把EDA厂商比喻为撬动整个半导体职业的杠杆也不为过。

假如工艺开展的不够快,EDA厂商还能够做什么?

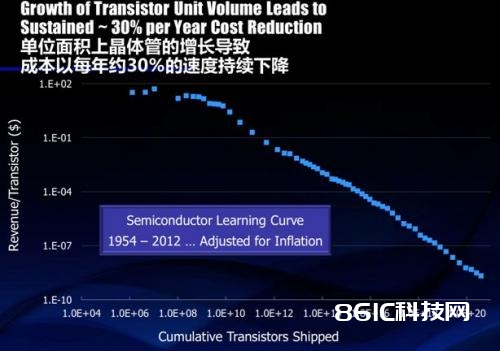

最能挑动业界神经的,仍是先进工艺节点的开展进展。进入深亚微米工艺今后,尤其是到现在的14、16nm制程,摩尔定律或许还有用,可是半导体的学习曲线或许现已遇到问题,单位面积上晶体管数量增加导致的本钱下降速度现已没有曩昔那么快。先进工艺关于IC规划企业的本钱压力也越来越大,EDA厂商是怎样应对先进工艺应战,又怎样协助客户来下降研制本钱的呢?

图一 半导体学习曲线

Mentor Graphics CEO Walden C. Rhines先生以为,先进节点工艺关于EDA厂商是机会也是应战,假如工艺停滞不前,则EDA东西厂商的收入也会受到影响。现在的先进工艺,例如 FinFET,关于成品率和测验的需求都要花费比以往多得多的人力物力来处理,Mentor针对先进工艺有完好的处理计划,例如Mentor的DFT东西关于FinFET测验验证支撑就适当有力。

而关于现在规划公司本钱上升的问题,Rhines先生指出,假如单指物理规划(physical design)并不存在这个问题,并且EDA中心规划软件的本钱是跟着整个半导体工艺演化成份额下降的。规划公司本钱上升是现在杂乱芯片规划需求许多资源投入到嵌入式软件与体系规划等方面,大规模芯片规划的本钱上升主要是由于体系集成需求越来越多的人力资源,而不是由于工艺演进需求更大更快的EDA东西所形成的。每一个新节点的研制本钱大约是旧节点研制本钱的三倍,咱们都知道半导体晶体管等级的本钱不断下降是趋势,可是下降本钱不只只要缩小特征尺度(feature size)这一种办法,有许多其他的办法能够下降晶体管的本钱,减小尺度仅仅其中之一。

图二 Mentor Graphics公司CEO Walden C. Rhines先生

Synopsys全球高档副总裁柯复华先生表明,EDA公司以往走在技能的最前沿,来驱动CMOS逻辑制程的演进,可是Synopsys很早就意识到晶圆厂在特别工艺制程上面所做的尽力。许多特别制程尽管不是选用最先进的节点,想要做到那个境地其实不简单。许多技能,例如高压(High Voltage)、CMOS图画传感器(CMOS Image Sensor)等,关于驱动、电流的要求都不是很简单完成的。这些技能的开展也十分重要,与摩尔定律的差异仅在于这些技能不是由工艺尺度减小而表现出来的。Synopsys针对这一趋势,在几年前现已开端调整,在优先保证关于最先进技能的需求做测验的一起,别的一方面也拉回来,关于曩昔比较老练的工艺节点,例如90、65nm,从纯逻辑转换到特别工艺制程也做了许多的支撑作业,保证这个技能对客户有协助。Synopsys在这方面也有很大的优势,便是其 IP部分,Synopsys许多研制工程师做的作业便是去满意客户关于特别制程的需求,客户的需求驱动了Synopsys的开展。

像Wally(Walden Rhines先生)所讲,本钱下降曲线是有问题的,实际上在20nm时咱们就说这个曲线存在问题。可是为什么还有人要做14、16nm呢,问题便是14、 16nm关于咱们来说是不值的,可是对需求14、16nm的极少数厂商来说是值得的。之所以有人乐意到14、16nm,是由于有某几颗IC有十分大的量,特别工艺制程赶不上这个量。可是能够抢到这个商场份额的厂家,在整个生态体系中的能量是极大的,他们需求投入十分多的资源,不光靠芯片规划罢了,许多的配套作业需求做,才干保持那么大的量。

“许多人或许会觉得EDA很无趣,EDA自身确实很无趣,可是假如从EDA串起来的整个职业视点来看,它是十分十分风趣的,尽力的空间也十分大。” Cadence全球副总裁亚太区总裁石丰瑜先生提到,“仅仅%&&&&&%职业不断的向前演进,EDA不跟着往前走,就没有未来。可是咱们要往前走了今后再往后看才风趣”。比方现在咱们都在往16、10、7nm走,谁也不知道接下来的脚步是越来越快仍是越来越慢,不知道资料的演进是否能够合作工艺的开展速度,假定走得没有那么快的时分,那么咱们就没有活干了吗?不见得,真的回头看或许会发现许多作业其时没有做好,现在能够把它做好,尽力去做今后却发现,在旧的工艺节点,还能够再挤出20%的功用出来,还能够把功耗再下降一点,闷着头做了今后会发现客户在等着你。EDA接下交游先进节点走,有必要要和客户深度结合。

“深度结合便是说,咱们卖一套那么贵的软件给客户,怎样协助客户赶快娴熟的运用起来。假如你花半年人家花三个月,那么你完了;软件有那么多的功用,还有许多能够调试的当地,你假如没有去调,闷着头按个钮出来今后就去流片,你倒运了。所以咱们怎样来帮你,你怎样来推进咱们,逼着咱们跟你一起生长,这是最重要的一点。”另一点便是关于老的节点,将来是否有力气再回过头去,把它精进与优化一下,让持续运用Cadence东西的人在老的节点上关于特定的运用也有更好的发挥。

快中求快、省而又省、精雕细镂 EDA厂商给IC规划企业的主张

“现在手机电脑等设备的生计周期越来越短,基本上每18个月用户就会换一部手机。”谈到IC规划公司的时刻压力时, Synopsys我国区总经理/武汉研制中心董事总经理葛群先生这样说。他表明假如%&&&&&%规划公司从规划芯片到流片成功需求花一年时刻,再花半年到一年时刻去进行软件的开发与优化,那么产品的上市时刻底子满意不了商场的需求。所以现在的办法学是在芯片规划开端之前,现已着手进行软件开发作业。 Synopsys供给的Virtualizer东西能够虚拟化硬件来提前进行软件开发与优化,芯片回来后软件开发作业现已差不多完毕了。经过这种新的规划办法能够把产品提前6~9个月上市。最好的一个事例是联发科,他们是全球最早研究出来用4个A7来完成四核计划的厂商,之前的四核计划至少是4个A9。联发科在运用Synopsys的这套体系今后发现运用A7乘四核来完成能够到达差不多的功用、更低的本钱与更小的功耗,一起软件能够跑得更快。