通用异步接纳/发送器(UART)是一种通用串行数据总线,用于异步通讯,能够完结全双工通讯。UART IP核是用在外部设备和Atera FPGA芯片上的SOPC间进行串行通讯的一种完结方法。它能够代替RS-232完结芯片与外设的输入/输出(I/O)操作。

GPS RTK(Real Time KinemaTIc)能够即时供给厘米级的定位解。在进行动态定位时,基准站将准确已知的GPS坐标和观测数据实时用微波链路传给流动站,在流动站实时进行差分处理,得到基准站和流动站坐标差;坐标差加上基准站坐标得到流动站每个点坐标。基准站向终端用户接纳机供给的信息包含对GPS卫星钟、星历数据、用户丈量伪距和载波相位等参数的批改。

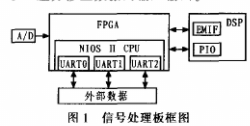

本文所用的信号处理板能够作为GPS RTK基站运用,能够与其他基站组网接纳差分批改数据定位或许自身的高精度单点定位输出定位成果和差分批改数据。作为基准站,不只要实时输出准确定位信息,并且需求与外界进行差分数据交流。因为同一时刻需求很多继续差分数据的输入与输出和用户操控指令的输入,规划选用了3个串口。

1 硬件结构

信号处理板为FPGA+DSP结构,具有多路A/D、D/A转化器材。中频信号经A/D采样后进入FPGA完结去载波,PRN码相关运算,IQ改换等操作后由DSP芯片进行定位解算。经过串口输入的用户操控指令恣意挑选串口对GPS定位成果的输出和GPS差分批改数据的输入输出。

FPGA芯片上装备了3个串口,别离为UART0、UART1、UART2,由SOPC Builder分配相对应的存储映射空间和中止恳求。每个模块均运用默许的基地址,并别离设定UART0、UART1、UART2的数据输入中止恳求号为IRQ1,IRQ2,IRQ3。别的,DSP芯片可能在恣意时刻经过3个串口发送不同数据。

假如DSP对每个串口发送数据时均向NIOS II CPU宣布中止恳求,则需求3根PIO管脚,占用太多针脚资源。本完结计划经过添加个串口操控寄存器,仅占用1根PIO管脚。

一起,对和DSP芯片进行交互操控的PIO信号分配中止恳求号为IRQ0。

每个UART口都有输入、输出两块RAM作为缓存,数据位宽为16bits。其间,串口输入缓存命名为ReadFromMemInterface,串口输出缓存命名为WriteToMemIntedace(见图2)。需求留意的是实践传输数据时,外部设备的串口参数的数据位长度设置为8 bits,因而需求在串口的软件处理进行字与字节的转化。

图3是NIOS II CPU在Quatus中的连线示意图,即坐落中心的inST6模块。该CPU首要管脚界说如表1所示。

值得阐明的是,ts_clk输入时钟20.46 MHz即为NIOS IICPU的时钟频率,串口波特率为115 200 bps,可由该时钟分频得到。DSP6713的EMIF为输入输出双向32位,在本规划中串口部分仅运用低16位,运用三态门来操控数据流向。三态门输入输出的使能信号是dsp给出的ce空间使能信号ce_6713。

串口输入数据先由NIOS II CPU写入每个串口的输入缓存,当满意条件时由out_pio管脚向dsp宣布中止,用以奉告其能够读取相应串口的数据了,缓存的数据由dspread0传递至三态门tri_16.dsp读取时三态门为dsp输入方向,dsp的EMIF数据线evm_D随即呈现数据,合作EMIF地址线evm_A即可完结串口输入数据向dsp传递;当dsp有数据要经串口输出时,数据由dsp的EMIF数据线evm_D输入,dsp经过in_pio向NIOS II CPU宣布中止信号,恳求发送数据。具体的发送接纳流程见下文。

2 软件规划

NIOS II CPU的操控代码部分分为主函数和各种中止呼应函数。在主函数里完结寄存器初始化、各串口数据输出的使命。串口的中止呼应函数则首要完结数据的输入使命。

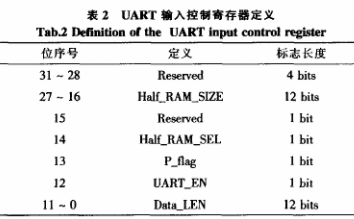

为了便于FPGA和DSP之间的操控信息交流,每个串口设有地址固定的长度各为32位(4字节)的输入和输出两个操控寄存器。经过对各标志位的读写操作即可完结体系对各串口的操控。串口的输入操控寄存器界说见表2,输出操控寄存器与之相似。

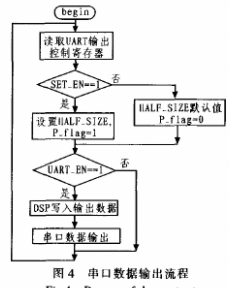

因为用户操控指令(包含信号处理板装备参数、输出数据类型操控等)与差分批改数据的数据长度和数据继续性有很大差异,在惯例数据传输方法之外对每个串口增设数据块传输形式。数据块传输形式可用于继续性很多数据的输入,选用每个串口对两块RAM进行乒乓读写操作的来计划完结。是否选用数据块传输形式由串口的操控寄存器中的第14位(P_flag)决议。关于非数据块输入形式中缓存巨细需求依据惯例数据最大长度来设定,过小会导致部分数据丢掉。当有数据需求输出时,由DSP向NIOS II CPU的RAM写入各UART输出操控寄存器的设定值,并经过GPIO向其宣布中止信号。可在NIOS II CPU的main函数中设置一个循环检测是否有由DSP输入的中止信号,若有再检测各UART的输出操控寄存器。输出流程图如图4所示。

图4中SET_EN用于设置个串口的输入形式(是否乒乓输入及乒乓输入时缓存的巨细)和串口使能等操作,输入操控寄存器的默许值在体系初始化时由DSP写入。

当数据输入时,NIOS II CPU检测到来自串口的中止恳求,进入对应的中止呼应程序。首要对数据传输形式进行判别,P_flag默许值为0,标明非数据块输入形式。该形式下输入的数据有特定的完毕标志符组合,一旦检测到完毕标志则发送已缓存的数据并完结状况清零以便下次接纳;P_flag为1则为接连数据块输入,当Half_BAM0或Half_RAM1其间一块写满时即向DSP宣布中止信号,DSP即进入中止服务程序读取数据。程序流程图如图5所示。

3 完毕语

选用Altera FPGA芯片上的NIOS II CPU操控串口的长处是充沛运用硬件资源,能够减轻DSP芯片的核算量。测验标明,NIOS II CPU作业频率为20.46 MHz,串口波特率设置为115 200,数据位为8 bit,各串口能够一起正常输入输出。多串口能够一起输入输出数据,由指令能够灵敏装备传输形式,以习惯不同数据传输类型的需求。

本文处理了单串口传输不能满意GPS高精度接纳机对多种数据一起输入输出的要求,完结了GPS定位成果、RTK差分数据与外界的实时交流以及用户操控指令的输入。本计划的长处是经过添加各串口的输入/输出操控寄存器,使DSP芯片能够仅以两个GPIO资源完结本来需求3个串口输入/输出功用相对应的6个中止操作;选用NIOS II CPU进行多串口操控能够削减硬件调试时刻,节省FPGA片内资源。不足之处是未完结串口波特率、数据位等实时装备。

责任编辑:gt