1、导言

步进电机是一种离散运动的设备,步进电机驱动器经过外加操控脉冲,并按环形分配器决议的分配办法,操控步进电机各相绕组的导通或截止,然后使电机发生步进运动。在单片机呈现曾经步进电机操控彻底由硬件完结,不同类型电机和不同作业办法需求不同的环形分配器。假如替换电机类型或改动作业形式,则整个硬件电路就要从头规划。跟着单片机的呈现和遍及,选用软件完结环形分配器取得广泛的运用。此类环形分配器只需改动软件即可习惯各种电机,具有极大的灵活性。但也存在以下缺陷:因为核算机是一种非并行履行的器材,各信号的同步将受到影响。选用单片机的操控电路,可靠性不高,抗干扰才能不强。假如呈现问题,程序自身尽管能够经过软件圈套等办法复位单片机使它回到正常作业状况,可是关于驱动器则意味着无法纠正的时序过错,这将导致失步的发生。本文提出了一种依据FPGA的新式集成式步进电机驱动体系完结计划,该计划选用含糊自组织PID调理办法完结对步进电机驱动体系的闭环操控,极大地进步了体系的自习惯才能,一起运用FPGA上嵌入的微处理器PicoBlaze将步进电机驱动体系的操控器和驱动器集成在一片FPGA芯片上,完结了可编程片上体系规划,极大地进步了操控功用。这种新式的操控器体积小,结构简略,本钱低,抗干扰才能强,一旦投入运用必将扩展步进电机的运用规模,下降体系的本钱。

2 、步进电机的细分驱动原理

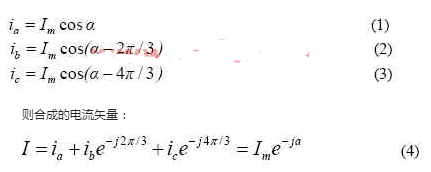

步进电机细分驱动本质上是对电机励磁绕组中的电流进行操控,使电机内部的组成磁场为均匀圆形旋转磁场,然后完结对步进电机步距角细分。组成磁场矢量的幅值决议了步进电机旋转力矩的巨细,相邻两组成磁场矢量的夹角巨细决议了该步距角的巨细。关于三相混合式步进电机而言,向A、B、C三相绕组别离通以相位相差2/3π而幅值相同的正弦波电流,则组成的电流矢量在空间做幅值安稳的旋转运动,其对应的组成磁场矢量也作相应的旋转。

在细分驱动办法下,因为步距角小,步进电机的分辨率得到大幅度进步,一起这种驱动办法又可有用按捺单步运转中所发生的噪声和振动现象。

3 、含糊自组织PID调理操控算法

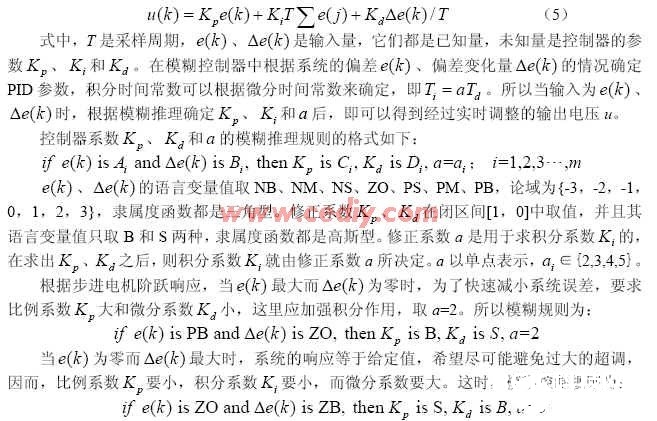

因为步进电机调速体系具有非线性等特色,参数改动规模较大,因而要取得杰出的功用,就需求对PID的份额增益、积分和微分时刻常数按某种优化办法作在线调整,因而在规划中选用一种含糊自组织PID操控器对传统PID调理办法进行优化。

一般PID调理器的离散表达式如下:

顺次类推可得含糊

推理规矩如表1所示。

4、 驱动体系硬件规划

本体系选用交-直-交电压型电路,分为功率驱动电路和操控电路两大块。功率驱动电路主要有整流桥、滤波电容及IPM功率模块组成;操控电路以Xilinx公司的FPGA芯片为中心,包含电流检测电路、驱动电路及维护电路。驱动体系框图如图1所示。

图1 驱动体系框图

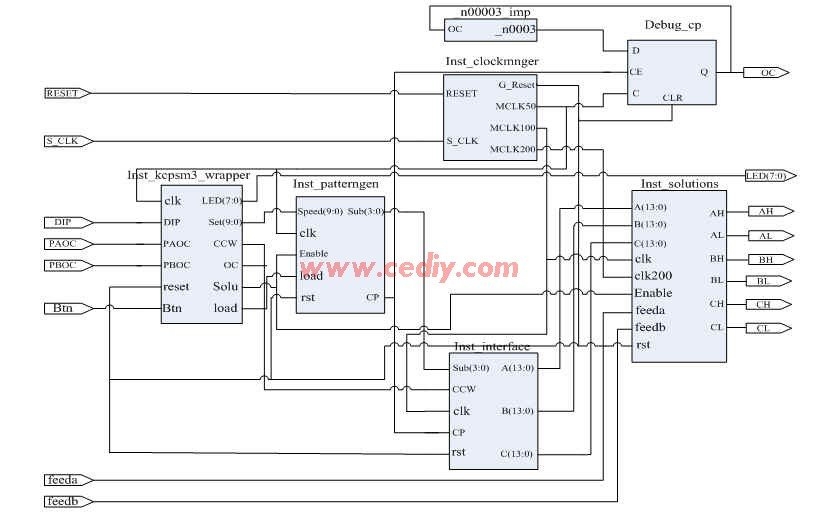

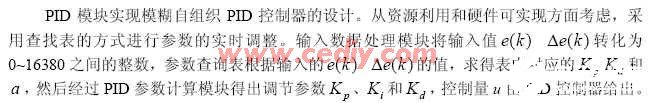

驱动体系的中心是FPGA操控芯片的规划,选用层次化开发办法,顶层模块由多个子模块组合而成,选用自底向上的办法进行开发,FPGA内部硬件原理图如图2所示。用户输入在PicoBlaze微处理器中进行处理,将操控信号送入CP脉冲发生器,发生CP脉冲和细分等级数,同转向信号CCW一起送入正弦表数据接口模块中,经过内部逻辑发生三相相电流给定数据,与电流反应模块测验的反应电流,经过PID调理,发生操控信号送入PWM发生器中,PWM模块将输出六路PWM操控信号,操控IGBT通断,以完结对电机操控。

图2 FPGA内部硬件原理图

(1) ClockMnger模块将输入的晶振时钟进行倍频,输出CLK50,CLK100,CLK200三个时钟信号。DCM确认信号后,三个时钟信号均经过BUFGMUX切换到安稳后的时钟源上去。本模块输出一个G_Reset信号,在一切时钟都彻底安稳后才置G_Reset为无效。为了消除异步Reset导致部分DFF的树立时刻不行的现象,模块运用一个DFF在时钟的上升沿同步Reset信号,供给满足的时刻裕量。

(2) Interface模块例化了一个单端口只读存储器寄存一个周期的正弦数据表。输入CP和CCW信号后,经过次序给出三相绕组对应的地址数据,即可查得三相电流的给定数据,并一起更新三个给定数据寄存器,送入下一个环节。转向交流也在本模块完结。输入的CCW信号将操控一个多路选择器,操控是否进行换相。本模块经过输入的细分信号和CP脉冲信

号一起决议三相绕组的地址数据的每次增量巨细,当细分层次最高时,地址计数器每次递加1;当处于非最高细分精度时,地址计数器每次递加2的N次幂,N由当时的细分精度确认。

(3) kcpsm3_wrapper模块选用FPGA上嵌入的Picoblaze 8位微处理器作为规划的主操控器,承受用户输入,和谐内部模块的作业。PSM代码程序界说了多个I/O地址,经过端口例化,完结处理器模块与外部模块的数据交流,当用户经过按键进行速度设置后,处理器进入中止,输出各种操控指令到接口模块和CP脉冲发生模块,操控电机状况,其间DIP用于拨码按钮的输入,LED用于发光二级管的输出,Btn用于按钮的输入,Set用于设定CP Pattern模块的速度输入寄存器,PAOC、PBOC来自外部过流信号的输入。Picoblaze模块中包含了一个内部复位操控电路,确保Picoblaze在器材装备和大局复位后的正确发动。

(4) PatternGenerator模块完结转速与CP脉冲对应的功用,给定一个转速信号后,经过查表得到对应的计数溢出数据。内部的计数器计数溢出时即发生一个CP脉冲。查找表输出的数据分为两部分,低位是CP计数器的计数数据,高位是对应转速的最佳细分等级,这两个信号都将输出给Interface模块,决议三相地址数据的改动。

(5) Solutions模块完结PWM操控、电流反应测验和PID调理,经过状况机和谐一切模块的作业开始和完结:检测A/D的转化标志位,当标志位为低时标明转化完结,别离发动两个电流模块进行反应电流丈量;等候两相电流丈量都完结后一起发动三个PID模块进行PID调理;等候调理完结后将核算得到的操控值/死区数据一起更新到三相PWM模块的PWM寄存器以及死区寄存器中。

PWM模块选用三角波作为PWM载波,为削减计数器的进位链长度,选用Prescaled计数器,拆分为3位计数器和11位计数器,削减组合逻辑推迟。死区维护发生器模块依据给定的死区长度数据,将输入的PX信号输出为PH和PL信号,别离对应IGBT的上下桥臂,并在PH和PL数据的变沿刺进死区维护。刺进的死区维护是经过上升计数器和下降计数器来完结的,确保上下桥臂不会一起导通。时序等于比较器内部存在一级DFF,比较成果需求推迟一个时钟周期才能够输出,削减了组合逻辑推迟。

5、 功用仿真

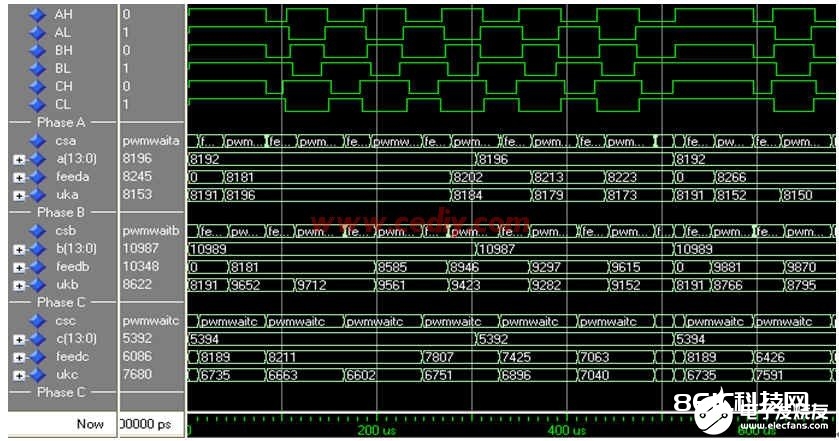

图3 驱动体系功用仿真

驱动体系功用仿真如图3所示。其间feeda和feedb信号是经过PLI接口调用链接库模仿生成的,全面模仿实际情况。图中包含了6个IGBT操控脚的输出波形,以及三相独立的状况机、给定、反应、操控数据。经核算,功用仿真数据彻底符合预期规划。

6、 定论

本文所规划的依据FPGA的新式集成式步进电机驱动体系,选用含糊自组织PID调理办法完结对步进电机驱动体系的闭环操控,进步了体系的自习惯才能。本文作者立异点是运用FPGA上嵌入的微处理器PicoBlaze将步进电机驱动体系的操控器和驱动器集成在一片FPGA芯片上,充分发挥了FPGA的高速并行和微处理器软件可编程的优势,完结了可编程片上体系规划,达到了对步进电机驱动体系的数字化操控,极大地进步了体系可靠性,增强了抗干扰才能,下降了规划本钱。

责任编辑:gt