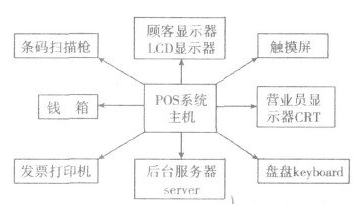

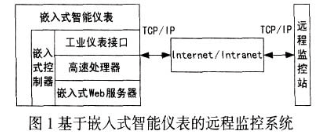

采用UML-RT和思想平台实现嵌入式控制器的设计-在仪器仪表迅速发展的同时,计算机和网络技术也在迅速发展,PC机已经从高速增长进入到平稳发展时期,嵌入式系统的出现和广泛应用,使计算机和网络进入了后PC时代,基于嵌入式智能仪表远程监控系统作为工业控制网络重要发展方向之一。而嵌入式控制器是能够实现智能仪表远程监控的关键设备,是工业控制仪表与Internet连接的桥梁。

基于WEB技术与嵌入式技术实现对设备的控制与诊断-基于以太网的单片机设备的控制与诊断结合先进的WEB技术与嵌入式技术,实现了PC与设备的直接跨平台的信息交互,这样PC就可以共享设备运行的信息,有效的实现对设备的控制与诊断。

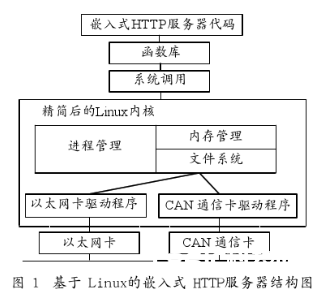

基于以太网和现场总线控制系统实现嵌入式HTTP服务器的设计-为了实现设计目标,嵌入式HTTP服务器一般应采用功能较强的能用PC、工业PC、或高档MPU作为硬件平台,嵌入式实时操作系统作为软件平台进行平发。硬件平台应具备以太网口和一个或多个通信模块,比如RS232、RS485、CAN通信卡等。嵌入式实时操作系统实现了TCP/IP等网络协议,并提供实时任务、进程管理、内存管理、文件系统、API等功能。

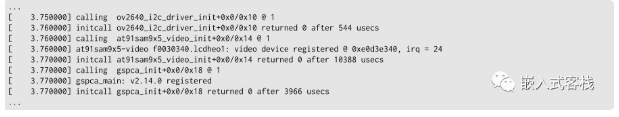

嵌入式Linux启动时间优化的秘密之三-内核-本文主要讲述嵌入式Linux启动时间优化的秘密之三-内核,我们继续上篇没有讲完的嵌入式Linux启动时间优化方法,本文主要会讲内核系统。想看上一篇的请查看本文结尾的链接。 内核 1.有用的调试手段 1. 1 内核初始化度量函数 要找出最长执行时间的内核初始化函数,请在内核命令行中添加initcall_debug。将内核日志中得到如下日志: 如使用initcall_debug可能需要在内核配置中使用CONFIG_LOG_BUF_SHIFT增加日志缓冲区的大小。还可能需要使能CONFIG_PRINTK_TIME和CONFIG_

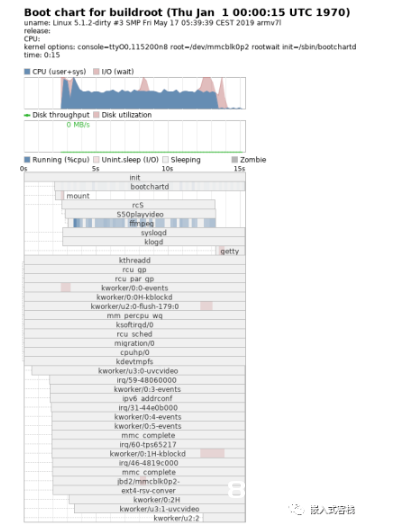

嵌入式Linux启动时间优化的秘密之四-启动脚本-本文主要讲述嵌入式Linux启动时间优化的秘密,我们继续上篇没有讲完的嵌入式Linux启动时间优化方法,本文主要会讲启动脚本。想看上一篇的请查看本文结尾的链接。 启动脚本 1.优化初始化脚本和系统启动 有多种方法可以减少启动应用程序之前执行启动脚本中花费的时间: 仅在启动必要的依赖项之后,尽快启动应用程序。 简化shell脚本 可以尝试执行启动脚本之前启动应用程序 1.1.bootchart 如果想更详细地了解用户区的引导顺序,则可以使用使用grabser

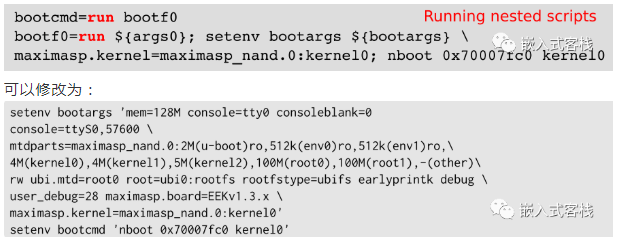

嵌入式Linux启动时间优化的秘密之五-Bootloader-本文主要讲述嵌入式Linux启动时间优化的秘密,我们继续上篇没有讲完的嵌入式Linux启动时间优化方法,本文主要会讲Bootloader。想看上一篇的请查看本文结尾的链接。 Bootloader 1. 裁剪 删除不必要的功能。 通常引导加载程序包括许多仅用于开发所需的功能。用较少的功能编译您的bootloader。 优化所需的功能。调整引导加载程序以获得最快的性能。 U-Boot是事实上的嵌入式bootloader标准,对于U-Boot而言,以下一些功能在产品中可能不需要: 在include / configs / 《

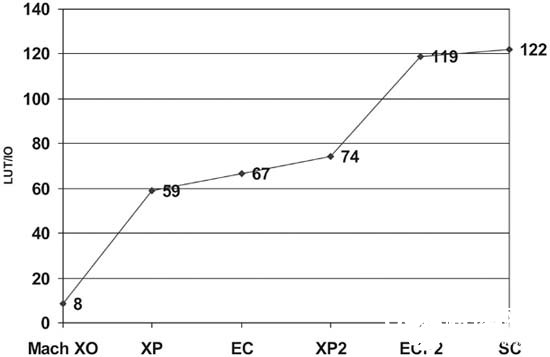

在FPGA中实现嵌入式逻辑分析仪的系统开发与调试应用-嵌入式逻辑分析仪Signal Tap II在对系统硬件模块进行监测时,是将测得的样本数据暂存于目标器件的RAM中,然后通过器件的JTAG端口和Byte Blaster II下载线一起将样本数据信息传出并送入计算机进行数据分析。Signal Tap II允许对设计中所有层次模块的信号进行监测,可以使用多时钟驱动,还能通过设置用以确定前后触发信号信息的比例。其使用方法步骤如下: