STM32程序之MAX6675热电偶温度读取-用HAL很简单,CS拉低以后,一个SPI读两个字节进来,然后就是凑成12位,换算。

MAX6675文档强调是在时钟下降沿读取数据,因此将SPI2配置为:[cpp] view plain copyhspi2.Init.CLKPolarity = SPI_POLARITY_LOW.

微流控芯片的发展及制造工艺介绍-微全分析系统的概念是在1990年首欠由瑞士Ciba2Geigy公司的Manz与Widmer提出的,当时主要强调了分析系统的微与全,及微管道网络的MEMS加工方法,而并未明确其外型特征。次年Manz等即在平板微芯片上实现了毛细管电泳与流动。

PIC单片机开发的经验、技巧总结分享-具体做法是在闲置的一个I/O脚(如RB1)和OSC1管脚之间跨接一电阻(R1),如图1所示。低速状态置RB1=0。需进行快速运算时先置RB1= 1,由于充电时,电容电压上升得快,工作频率增高,运算时间减少,运算结束又置RB1=0,进入低速、低功耗状态。工作频率的变化量依R1的阻值而定(注意R1不能选得太小,以防振荡电路不起振,一般选取大于5kΩ)。

ARM Cortex-M3 MCU的I2C和DMA操作被中断打断的解决方法-在项目开发的过程中,发现程序总是死在判断DMA一次传输是否完成这个标志位上。进一步回退分析,发现是在I2C读的过程中,有使用到DMA去取外部I2C设备的data。

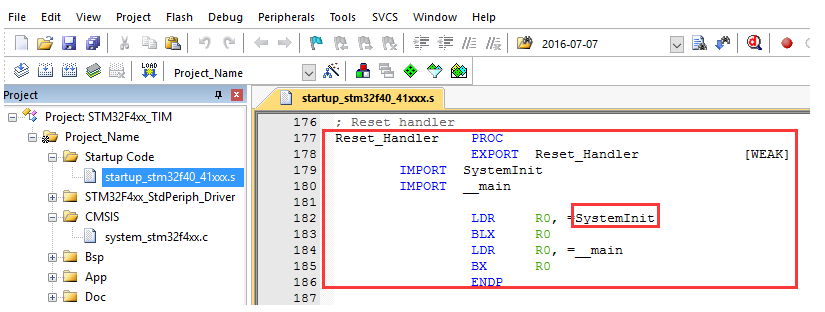

STM32时钟配置设计中的常见问题解析-在线调试的朋友应该知道,你点一下复位按钮,软件会跳转到下图的位置,其实可以看到复位之后第一个执行的函数就是【SystemInit】。说到这里,应该明白为什么我们在main函数开始没有看见时钟配置相关的函数了吧,程序是在复位后立马配置的时钟。

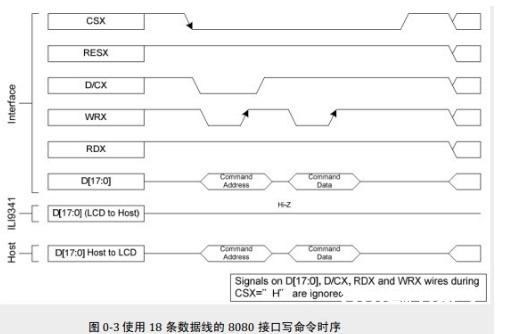

STM32单片机的FSMC对TFT的驱动-开始只是谈到别人对FSMC的理解,注意这里只讨论FSMC控制TFT,也就是在FSMC的NOR\PSRAM模式控制LCD,所以我们以下的分析都是基于这种模式的。

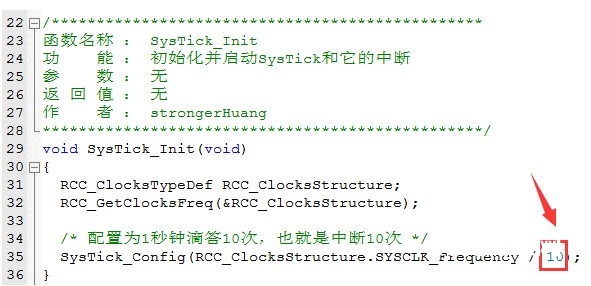

STM32单片机SysTick系统滴答功能解析-其实,SysTick能实现的功能,都可以由TIM来实现。SysTick无非就是定时中断的功能,它完全可以由TIM定时器来完成。之所以SysTick独立出来就是因为它属于内核一部分,方便用户移植,而且简单方便。学过uCOS的人都知道,以前在51,或者430上面是由定时器完成的时钟滴答,到后面ARM公司就用到了一个好的办法,就是在内核中标配一个SysTick,这样下来移植系统不用那么麻烦了。

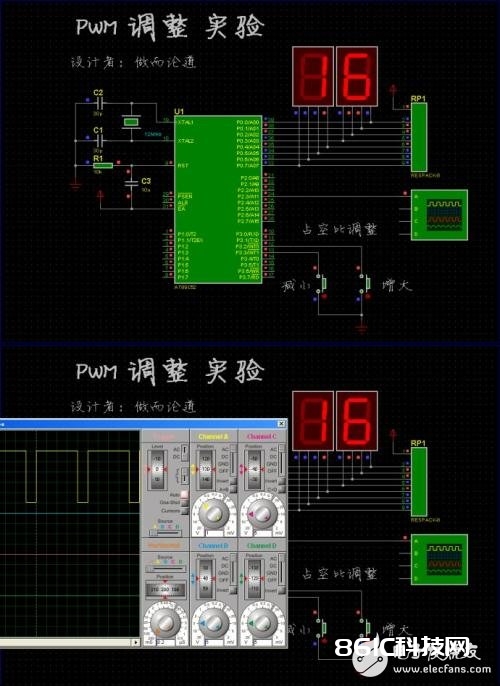

AT89C52单片机输出可调PWM波的方法设计-PWM实际上是在单片机的某个引脚输出一系列的矩形波,其周期一般是固定的;而其高电平、低电平所占用的时间,是可以受控调整的。 高电平、低电平所占用的时间之比,称为占空比,其值为0~1之间。 PWM的应用很广,简单的说,它可以控制灯光的亮度、可以控制直流电机的转速,甚至还可以输出语音信号。

如何消除单片机数码管的鬼影现象-“鬼影”的出现,主要是在数码管位选和段选产生的瞬态造成的。举个简单例子,我们在数码管动态显示的那部分程序中,实际上每一个数码管点亮的持续时间是 1ms 的时间,1ms后进行下个数码管的切换。在进行数码管切换的时候,比如我们从 case 5 要切换到 case 0 的时候,case 5 的位选用的是 ADDR0=1; ADDR1=0; ADDR2=1;假如此刻 case 5 也就是最高位数码管对应的值是 0,我们要切换成的 case 0 的数码管位选是 ADDR0=0; ADDR1=0; ADDR2=0;而对应的数码管的值假如是 1。