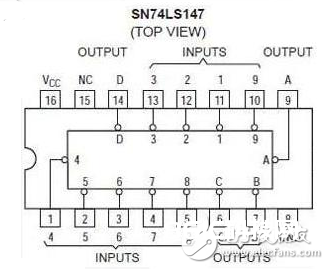

本站为您提供的74ls147中文资料汇总(74ls147引脚图及功能表_工作原理及逻辑图),本文主要介绍了74ls147中文资料汇总(74ls147引脚图及功能表_工作原理及逻辑图)。74LS147优先编码器的输入端和输出端都是低电平有效,即当某一个输入端低电平0时,4个输出端就以低电平0的输出其对应的8421BCD编码。当9个输入全为1时,4个输入出也全为1,代表输入十进制数0的8421BCD编码输出。采用16脚封装,是一个10线-4线8421BCD码优先编码器。

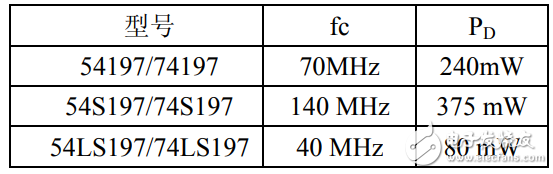

本站为您提供的74ls197中文资料汇总(74ls197引脚图及功能_逻辑功能及特性),本文主要介绍了74ls197中文资料汇总(74ls197引脚图及功能_逻辑功能及特性)。74ls197为可预置的二-八-十六进制计数器,异步清除端(CR)为低电平时,不管时钟端(CP0、CP1)状态如何,即可完成清除功能。计数/置入控制(CT/LD)为低电平时,不管时钟端(CP0、CP1)状态如何,即可完成预置功能。197还可作4位锁存器,此时CT/LD作为选通端。当CT/LD为低电平时,Q0~Q3随D0~D3而变化;当CT/LD为高电平时,只要时钟不作用,Q0~Q3将保持不变。

本站为您提供的74ls249中文资料汇总(74ls249引脚图及功能_逻辑功能及特性),本文主要介绍了74ls249中文资料汇总(74ls249引脚图及功能_逻辑功能及特性)。输出端(a~g)为低电平有效,可直接驱动指示灯或共阴极LED。当BI为低电平,不管其它输入端状态如何,a~g均为低电平。当/RBI和地址端(A~D)均为低电平,并且灯测试(/LT)为高电平时,a~g均为低电平,脉冲消隐输出(/RBO)为低电平。

本站为您提供的微动开关的电路工作原理,上电后R_S触发器的R端为低电平。S端为高电平,R—s触发器处于“O”状态,IC1③和圈11脚都为低。电平,两级单稳均处于静止状态。IC3③脚输出低电平,无计数脉冲送入JD-5计数器,开机清零后显示全0。