MSP430F5438A中断系统实现- MSP430F5438A 有三个定时器: TA0、TA1 和 TB0。 2、CCR0单独用一个中断向量,且优先级最高。其他CCR1–CCR5用公用一个中断向量。3 3、中断向量: #defineTIMER1_A1_VECTOR(48*2u)/*0xFFE0Timer1_A3CCR1-2,TA1*/ #defineTIMER1_A0_VECTOR(49*2u)/*0xFFE2Timer1_A3CCR0*/ #defineTIMER0_A1_VECTOR(53*2u)/*0xFFEATimer0_A5CCR1-4,TA0*/ #defineTIMER0_A0_VECTOR(54*2u)/*0xFFECTimer0_A5CCR0*/ #defineTIMER0_B1_VECTOR(59*2u)。

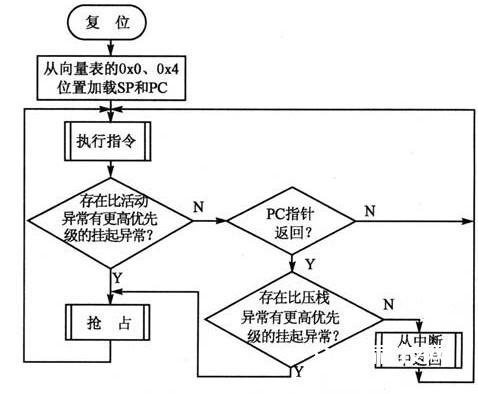

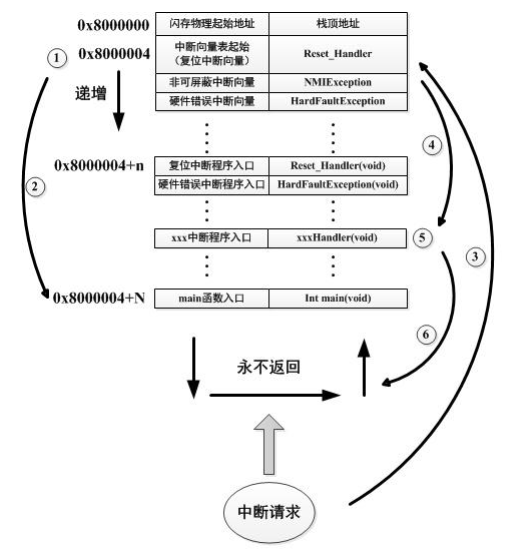

基于单片机2440test中断向量处理方案-这里不用中断(interrupt)而用异常(exception),毕竟中断只是异常的一种情况,呵呵

下面主要分析的是“中断异常”说白了,就是我们平时单片机里面用的中断!!!所有有器件

引起的中断,例如TIMER中断,UART中断,外部中断等等,都有一个统一的入口,那就是中断

异常 IRQ ! 然后从IRQ的服务函数里面分辨出,当前究竟是什么中断,再跳转到相应的中断

服务程序。

STM32的Cortex-M3中断异常处理-在STM32处理器中有43个可屏蔽中断通道(不包含 16个 Cortex?-M3的中断线)。共设置了16个可编程的优先等级(使用了 4位中断优先级);它的嵌套向量中断控制器(NVIC)和处理器核的接口紧密相连,可以实现低延迟的中断处理和有效处理地处理晚到的中断。嵌套向量中断控制器管理着包括核异常等中断。

STM32单片机的IAP向量问题解决方案-// 1:复制用户代码中的中断向量表到SRAM首地址

// 2: 开启SRAM的重映射功能,将SRAM的地址映射到0x00000000

// 3: MDK设置RAM运行地址时,要跳过前48个地址(地址为32位,共192字节),中断向量表

// 不能被操作,否则程序运行将出错。

// 中断向量表起始位置位于编译好的用户代码的首地址,共48个地址。

如何采用STM32单片机中断向量控制器NVIC来分配优先级的数量-先占优先级的概念等同于51单片机中的中断。假设有两中断先后触发,已经在执行的中断先占优先级如果没有后触发的中断 先占优先级更高,就会先处理先占优先级高的中断。也就是说又有较高的先占优先级的中断可以打断先占优先级较低的中断。这是实现中断嵌套的基础。

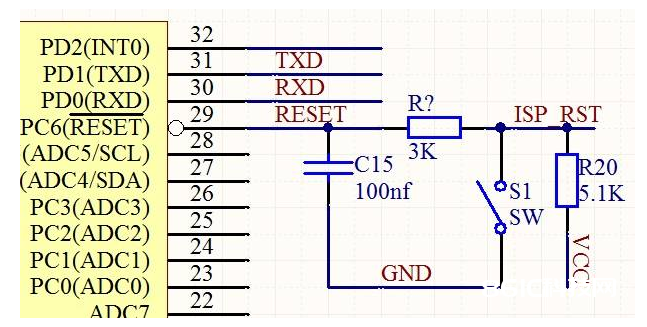

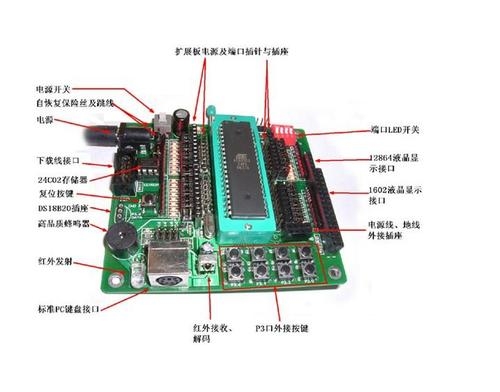

AVR单片机外部中断实例及下载烧录的方法-若中断向量位于Boot Loader 区,那么执行应用区代码时中断是禁止的。401不允许运行于Boot Loader 区的LPM 指令从应用区读取数据。若中断向量位于Boot Loader 区,那么执行应用区代码时中断是禁止的。BLB1模式BLB12BLB11111允许SPM/LPM 指令访问Boot Loader 区210不允许SPM 指令对Boot Loader 区进行写操作300不允许SPM 指令对Boot Loader 区进行写操作,也不允许运行于应用区的LPM 指令从Boot Loader 区读取数据。