Xilinx FPGA底层资源架构与设计规范-这一次给大家分享的内容主要涉及Xilinx FPGA内的CLBs,SelectIO和Clocking资源,适合对FPGA设计有时序要求,却还没有足够了解的朋友。

初学者必知的系统架构开发设计原则-很多开发者在面对设计/架构时,常常有想学但无从下手,学了又不会用的困扰。学习设计并不是只学习设计模式,在进行设计时,我们需要底层思想来支持,这里的底层思想其实就是设计原则,而设计原则则是面向对象编程基于现实背景衍生出来的一套规则,用来解决开发中的痛点。

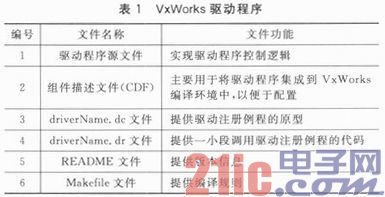

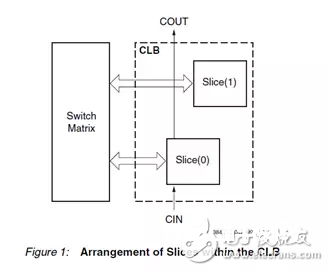

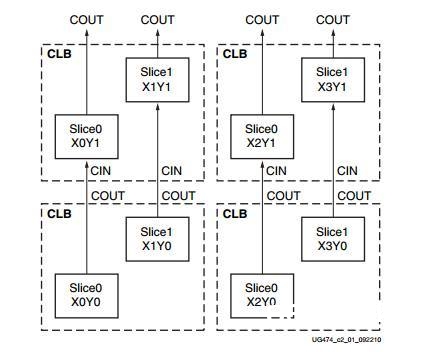

Xilinx FPGA内部体系结构-Xilinx的FPGA的基本结构是一样的,主要由6部分组成,分别为可编程输入/输出单元、基本可编程逻辑单元、嵌入式块RAM、丰富的布线资源、底层嵌入功能单元和内嵌专用硬核等。

示波器数字示波器一直是工程师设计、调试产品的好帮手。但随着计算机、半导体和通信技术的发展,电路系统的信号时钟速度越来越快,信号上升时间也越来越短,导致因底层模拟信号完整性问题引发的数字错误日益突出。针