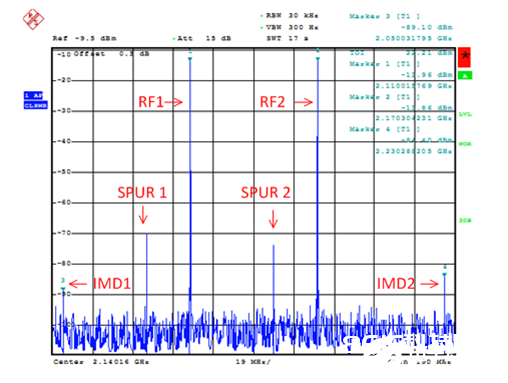

调制器输出端的寄生信号的产生原因和如何消除-最近评估了 TRF3720 全面集成型 IQ 调制器和 PLL/VCO 线性性能。在测量 OIP3 性能时,观察到了出乎预料的寄生信号,如图 1 所示。经与同事讨论,我们得出的结论是数模转换器 (DAC) 基带 (BB) 影像与 TRF3720 电压控制振荡器 (VCO) 及本地振荡器 (LO) 的混合产生了这些寄生信号。整合 BB 滤波器可最大限度地消除这些寄生信号。

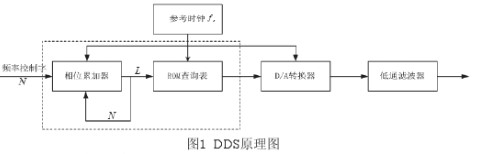

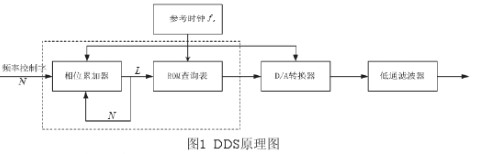

在FPGA硬件平台通过采用DDS技术实现跳频系统的设计-DDS的原理如图1所示,包含相位累加器、波形存储器(ROM)、数模转换器(DAC)和低通滤波器4个部分。在参考时钟的驱动下,相位累加器对频率控制字N位进行累加,得到的相位码L作为ROM的地址,根据地址ROM输出相应幅度的波形码,然后经过DAC生成阶梯波形,经低通滤波器后得到所需要的连续波形。

在FPGA硬件平台通过采用DDS技术实现跳频系统的设计-DDS的原理如图1所示,包含相位累加器、波形存储器(ROM)、数模转换器(DAC)和低通滤波器4个部分。在参考时钟的驱动下,相位累加器对频率控制字N位进行累加,得到的相位码L作为ROM的地址,根据地址ROM输出相应幅度的波形码,然后经过DAC生成阶梯波形,经低通滤波器后得到所需要的连续波形。