在FPGA中实现嵌入式逻辑分析仪的系统开发与调试应用-嵌入式逻辑分析仪Signal Tap II在对系统硬件模块进行监测时,是将测得的样本数据暂存于目标器件的RAM中,然后通过器件的JTAG端口和Byte Blaster II下载线一起将样本数据信息传出并送入计算机进行数据分析。Signal Tap II允许对设计中所有层次模块的信号进行监测,可以使用多时钟驱动,还能通过设置用以确定前后触发信号信息的比例。其使用方法步骤如下:

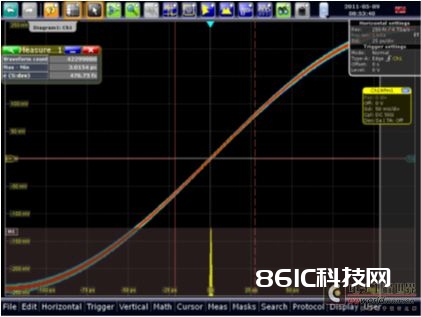

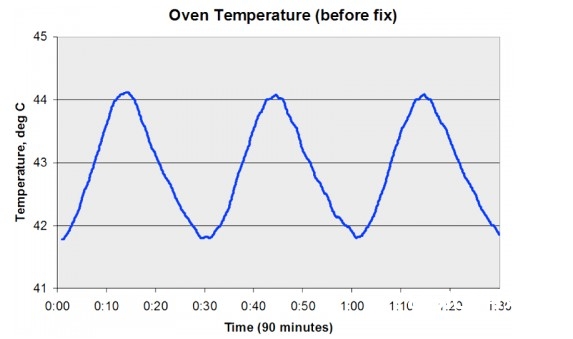

一颗螺丝引发出奇怪的正弦波干扰-在这里我应该要告诉你更多关于这台仪器的信息,它是用来量测液态样本的四种物理特性;待测样本透过独立的帮浦,以高压(700PSI)、恒定流速(每分钟1.0 ml)供应。仪器内的一个烤箱配置了关键的传感器、毛细管、过滤器以及相关的管路,由比例-积分-微分控制器(PID)将温度控制在摄氏37度。

基于电能测量与控制一体化集成管理的目的,设计了以钜泉ATT7037AU SOC芯片为核心的电能参数检测及用电管理终端核心电路。阐述了自适应负载识别的原理,并通过空调实例提出并说明了一种负载样本数据库和

在血液分析仪、体外诊断系统和其他很多化学分析应用中,液体必须从一个容器中转移到另一个,以便将样本从试管中、或者将试剂从瓶中吸取出来。这些实验室系统经常需要处理大量样本,因此尽可能缩短处理时间很重要。为