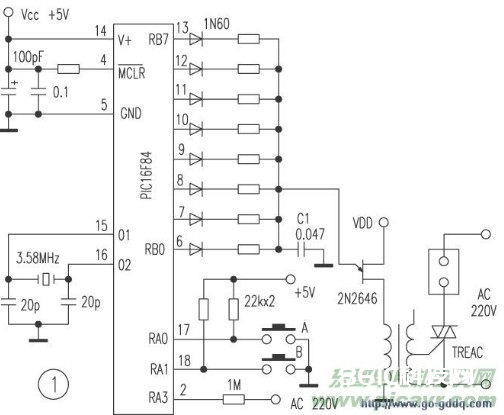

PIC单片机对电风扇送出仿自然风的设计-Rx接于PIC16F84 单片机 的RB0~RB7口;RA0口为启动信号输入口,当A键按下时,自然风发生器开始工作;RA1口为停止信号输入口,当B键按下时,自然风发生器停止运行;RA3口为交流电相位检测口。用于确定交流电的起始相位。

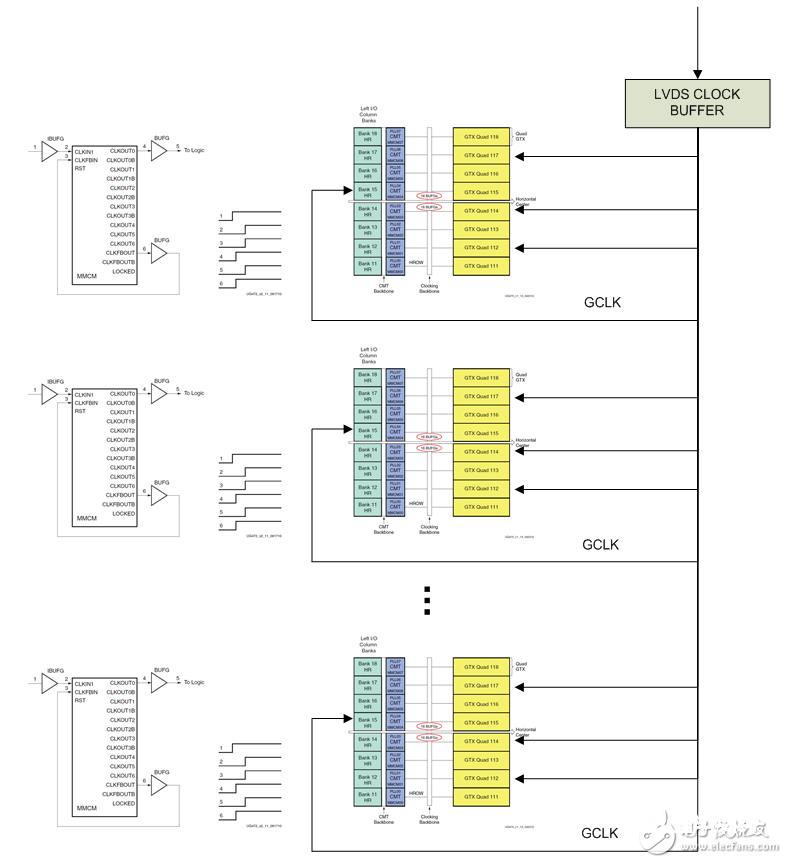

利用MMCM实现多芯片相位对齐的串行收发器纠偏方法-在一些特定的应用场景下,需要支持单板内多芯片串行收发器纠偏。要求各接收/发送机输入/出的数据相位差很小,比如250pS。为了达到该技术指标要求,必须使用多通道相位对齐技术、输入输出FIFO旁路技术。通常的相位对齐技术由于引入了Delay_Aligner,会带来2~4nS的相位不确定,不能满足系统指标要求。 这里介绍一种利用MMCM实现多芯片相位对齐的串行收发器纠偏方法: 1) 利用图1所示电路实现多芯片间的全局时钟相位对齐。

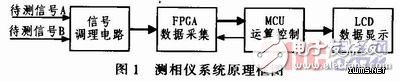

利用FPGA来实现李沙育图形数据的运算与存储系统设计-示波器测量频率和相位的方法很多, “李沙育图形法”就是其中用得最多的一种。“李沙育图形法”又称波形合成法,就是将被测频率的信号和频率已知的标准信号分别加至示波器的Y轴输入端和x轴输入端,在示波器显示屏上将出现一个合成图形,这个图形就是李沙育图形。李沙育图形随两个输入信号的频率、相位、幅度不同,所呈现的波形也不同。

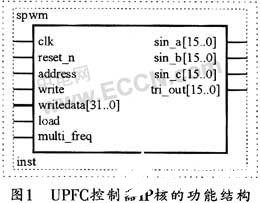

使用Altera CycloneIIEP2C35评估板实现UPFC控制器IP核的设计-UPFC控制器的IP主要用来输出3路相位分别相差2π/3的正弦波形数据和3路相位分别相差2π/3的三角载波波形数据。由于UPFC控制系统采用SPWM调制技术,所以要求UPFC控制器IP输出的正弦波频率应跟电网频率保持一致,输出的正弦波幅值和相位可以根据需要进行调节;而输出的三角载波频率、幅值和相位则保持不变。

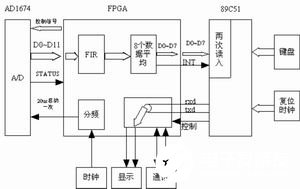

基于FPGA实现FIR数字滤波电路的设计及应用-这样就可以把FIR滤波器设计成具有线性相位。利用这一情况,可以得到的乘法结构,需要(N+1)/2次乘法,仅是级联或并联结构所需次数的一半,因此,实际应用中多采用此方法。

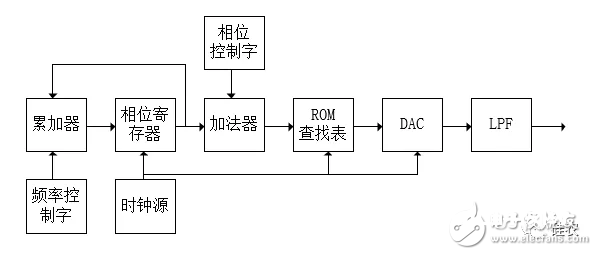

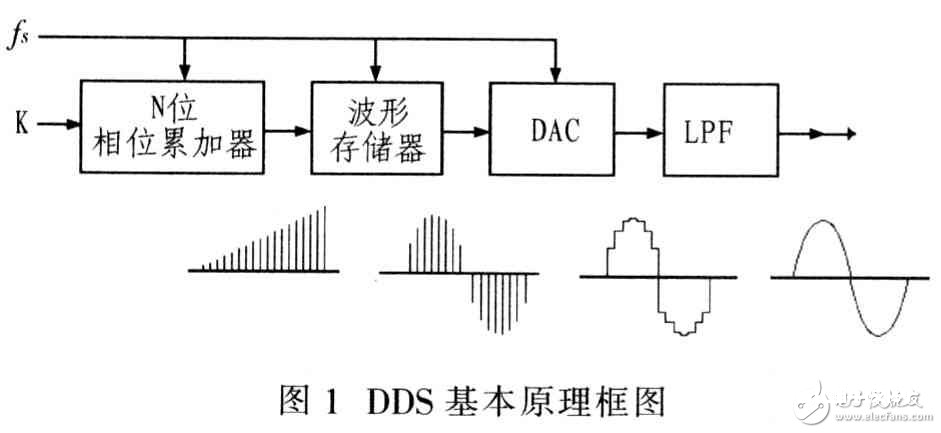

采用FPGA实现DDS任意波形发生器设计-在系统时钟脉冲的作用下,相位累加器不停累加,即不停查表,把波形数据送到D/A转换器转换成模拟量输出,从而合成波形。滤波器则进一步平滑D/A转换器输出的近似正弦波的锯齿阶梯波,同时衰减不必要的杂散信号。

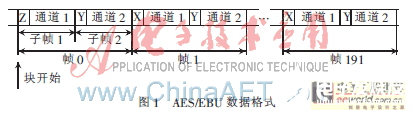

一种基于FPGA内部存储器的适合音频解嵌的高效异步FIFO设计-异步FIFO存储器是一种在数据交互系统中得到广泛应用的先进先出逻辑器件,具有容纳异步信号的频率(或相位差异)的特点。使用异步FIFO可以在两个不同时钟系统之间快速而方便地传输实时数据。因此,异步FIFO被广泛应用于实时数据传输、网络接口、图像处理等方面。

关于分段多项式近似的DDFS研究及FPGA实现的设计过程浅析-感应式磁力仪基于法拉第电磁感应原理,用于探测近地空间的低频交变磁场 ,它通常自带标准信号源,用于在轨定标。高质量的定标检测信号,是保证感应式磁力仪探测到的变化磁场波形和频谱信息科学性的前提。直接数字频率合成技术 (Direct Digital Frequency Synthesis,DDFS)于1971年被J.Tierney首次提出。DDFS采用数字技术,以相位为出发点进行频率的合成,具有高稳定性,高分辨率和较小的相位噪声,DDFS的性能指标远超传统频率合成技术,因此广泛应用于数字通信和精密仪器中。利用直接数字频率合成技术能为感应式磁力仪提供高精度的标准定标信号源。