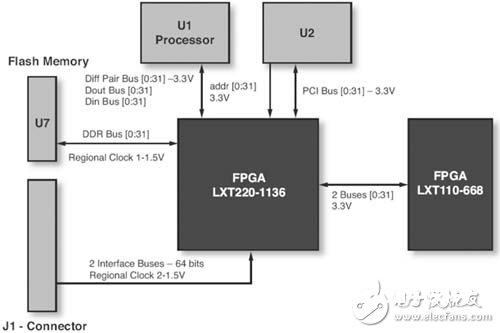

介绍了Xilinx FPGA的配置原理和FPGA模块化设计流程以及划分重构模 块的原则。通过一个实例介绍了采用模块化设计方法实现Virtex-E FPGA动态部分重构的过程,能使重构模块在系统运行时改

能够应用和生产,继而成为一个正式的有效的产品才是PCB layout最终目的,layout的工作才算告一个段落。那么在layout的时候,应该注意哪些常规的要点,才能使自己画的文件有效符合一般PCB加

PLL锁相环的特性、应用与其基本工作过程-PLL(Phase Locked Loop),也称为锁相环路(PLL)或锁相环,它能使受控振荡器的频率和相位均与输入参考信号保持同步,称为相位锁定,简称锁相。

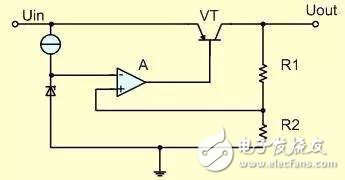

ldo与dcdc区别、原理及应用详解-LDO低压差线性稳压器,故名思意,为线性的稳压器,仅能使用在降压应用中。也就是输出电压必需小于输入电压。C/DC:直流电压转直流电压。严格来讲,LDO也是DC/D