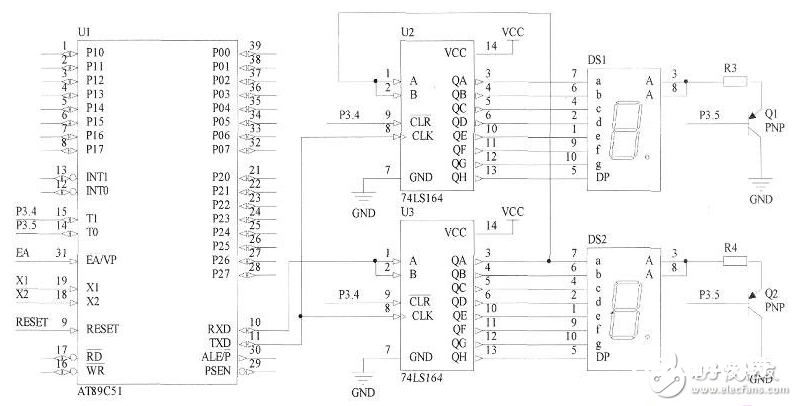

74ls164单片机编程汇总(跑马灯/驱动数码管)-本文主要介绍了74ls164单片机编程汇总(跑马灯/驱动数码管)。用单片机驱动LED数码管有很多方法,按显示方式分,有静态显示和动态(扫描)显示,按译码方式可分硬件译码和软件译码之分。使用数码管时,要注意区分这两种不同的接法:共阴极和共阳极。共阴极时,为1则亮;共阳极时,为0则亮。比如共阴极的方式接数码管,显示“1”,则编码为0x3f,即00111111(dp g f e d c b a )。

STC89C51单片机对AD模数转换学习板的控制原理解析-ADC0809是采样频率为8位的、以逐次逼近原理进行模一数转换的器件。其内部有一个8通道多路开关,它可以根据地址码锁存译码后的信号,只选通8个模拟输入信号中的一个进行A/D转换。

AT89S52单片机对LED点阵显示屏的控制设计-LED 点阵显示屏是由20 个8*8 的LED 点阵块组成,形成16*80 矩形点阵,以Atmel 公司的AT89S52单片机为控制核心。显示屏的其他主要硬件有:①带锁存输出的8位移位寄存器74HC595,作为LED的列线驱动输入;②三八译码器74LS138,作为LED行线的译码选择;③三极管C9012,连接两个三八译码器的十六个输出端,作为开关使用,驱动LED的行线。

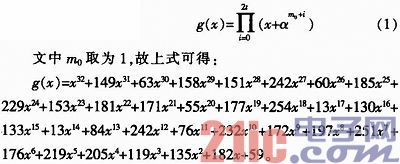

通过利用FPGA器件和EP1s25F672I7芯片实现LDPC码编码器的设计-低密度奇偶校验(Low Density Parity Check Code,LDPC)码是一类具有稀疏校验矩阵的线性分组码,不仅有逼近Shannon限的良好性能,而且译码复杂度较低, 结构灵活,是近年信道编码领域的研究热点,目前已广泛应用于深空通信、光纤通信、卫星数字视频和音频广播等领域。LDPC码已成为第四代通信系统(4G)强有力的竞争者,而基于LDPC码的编码方案已经被下一代卫星数字视频广播标准DVB-S2采纳。

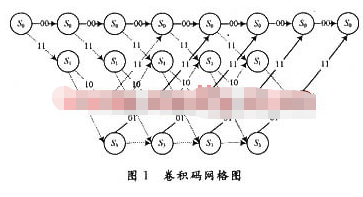

采用可编程逻辑器件的译码器优化实现方案-由于卷积码优良的性能,被广泛应用于深空通信、卫星通信和2G、3G移动通信中。卷积码有三种译码方法:门限译码、概率译码和Viterbi算法,其中Viterbi算法是一种基于网格图的最大似然译码算法,是卷积码的最佳译码方式,具有效率高、速度快等优点。从工程应用角度看,对Viterbi译码器的性能评价指标主要有译码速度、处理时延和资源占用等。本文通过对Viterbi译码算法及卷积码编码网格图特点的分析,提出一种在FPGA设计中,采用全并行结构、判决信息比特与路径信息向量同步存储以及路径度量最小量化的译码器优化实现方案。测试和试验结果表明,该方案与传统的译码算法相比,具有更高的速度、更低的时延和更简单的结构。

摘要:介绍了符合CCSDS标准的RS(255,223)码译码器的硬件实现结构。译码器采用8位并行时域译码算法,主要包括了修正后的无逆BM迭代译码算法,钱搜索算法和Forney算法。采用了三级流水线结构

差错控制编码技术对改善误码率、提高通信的可靠性具重要作用。RS码既可以纠正随机错误,又可以纠正突发错误,具有很强的纠错能力,在通信系统中应用广泛。由于RS码的译码复杂度高,数字运算量大,常见的硬件及软