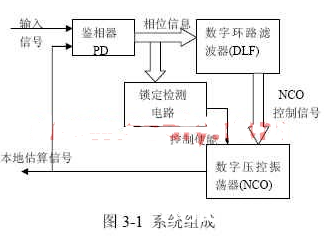

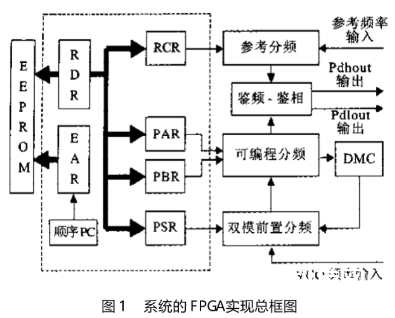

基于FPGA器件和CPU控制实现数字锁相环频率合成系统的设计-数字锁相环频率合成器已经广泛的运用在军事和民用无线通信领域,而用CPU控制的可编程大规模数字锁相环频率合成器则是其中的关键技术。当前,可编程逻辑电路在数字系统设计中飞速发展,很多中规模,甚至大规模的数字系统已经可以通过可编程逻辑电路来实现单片集成,即用一个芯片完成整个数字系统的设计。因此将CPU控制的数字锁相环频率合成系统集成在一块可编程逻辑芯片中实现已经成为可能。本系统由多个可编程的数字分频器、数字鉴频-鉴相器以及协调控制工作的CPU组成。