剖析了CAN操控器SJA1000的特色及CAN协议通讯格局。规划了操控器SJA1000的IP软核,能为运用供给一个功用优秀的、易于移植的操控器SJA1000,完结了对步进电机的操控。

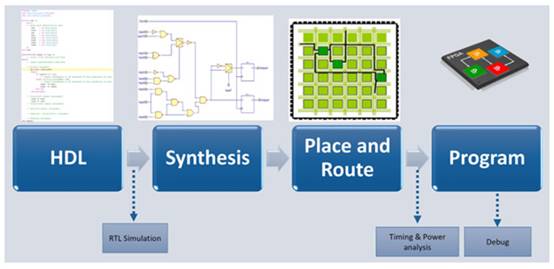

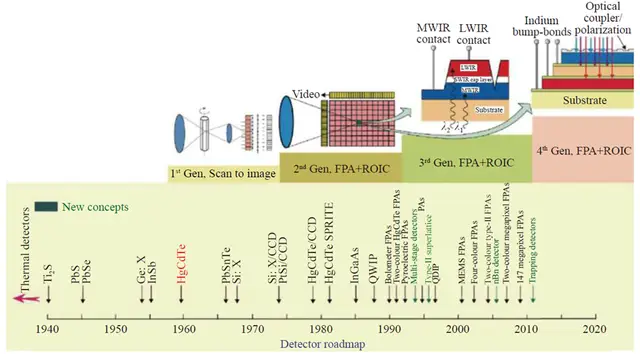

操控局域网(CAN)归于现场总线的范畴,它是一种有用支撑分布式操控或实时操控的串行通讯网络。与一般的通讯总线比较,CAN总线的数据通讯可靠性、实时性和灵活性好,运用范畴十分广泛,一般根据ARM或51单片机,完结与CAN操控器的通讯联络。FPGA/SOPC技能是完结嵌入式体系的最高方法,根据IP软核的规划与运用也必将成为代替硬核的一种发展趋势。凭仗QuartuslI和NiosII东西,根据FPGA的VHDL(或Verilog)言语规划的IP核能够供给灵活性和功用更好的操控器。

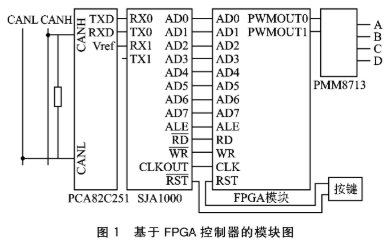

图1为一个根据FPGA的操控器的CAN总线节点。其间PCA82C251是CAN总线接纳器,SJA1000是CAN总线通讯操控器,PMM8713是驱动步进电机的脉冲分配器,FPGA模块在节点模型中对SJA1000进行操控,并将接纳到的帧信息进行处理,发送给脉冲分配器,以驱动步进电机。

在规划中选用自顶向下的规划办法。经过剖析SJA1000常用的操控芯片51单片机的功用,将其分为首要的4个模块:初始化模块、位查询模块、数据处理模块和缓冲区开释模块。

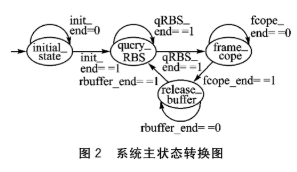

对SJA1000完结操控功用的进程用状况图描绘如图2所示,这也是体系的主状况机。4个状况对应上述的4个功用模块,首先在initial_st-ate完结对sJA1000的初始化,在由init_end信号给出初始化完结标志后,进入查询状况,即query_RBS状况,由位查询模块完结此刻对SJA100 0的状况查询。假如查询到SJA1000缓冲区有帧信息,将qRBS_end置“1”,进入下一个状况frame_cope,即帧处理状况,此刻由数据处理模块完结对缓冲区的数据读取,并作处理。在读取完一帧数据后,需求开释缓冲区,为下一帧信息的接纳做准备。此刻状况转入了release_buff-er,对应功用模块中的缓冲区开释模块,此状况完毕后又转入位查询状况,为下一帧信息接纳做准备。

初始化模块首要在体系上电或重启后,先对SJA1000进行初始化;位查询模块是在初始化完结后,对SJA1000状况寄存器的接纳缓冲区标志位不断进行查询,假如在缓冲区收到一帧信息后,则转入数据处理模块,不然继续进行查询;数据处理模块则是在查询到接纳缓冲区有数据后,读入帧数据,并对帧数据进行处理;缓冲区开释模块是在一帧信息处理完毕后,开释缓冲区空间。

除了上述4个功用模块之外,还需求读写模块、双端口模块、模块接口操控逻辑等。

1 、读写模块

由SJA1000的数据手册可知,SJA1000供给的微处理器接口信号有地址数据复用总线AD0~AD7、地址锁存信号ALE、片选信号、读写使能信号和、以及复位信号。

SJA1000的数据信号和地址信号是时分复用的,而FPGA中不存在地址的概念,关于FPGA来说,输出的只要数据。因而规划的要害便是把S-JA1000中的寄存器地址当成数据写入到SJA1000中,合作地址锁存信号ALE和写答应信号完结对SJA1000特定寄存器的指令字写入。读写使能信号是、以及复位信号。规划的要害便是把SJA1000中的寄存器地址当成数据写入到SJA1000中,合作地址锁存信号ALE和写答应信号完结对SJA1000特定寄存器的指令字写入。与写操作类似,只需严厉依照时序,将ALE、、、引脚的电平互相合作置高或置低,即可完结读操作。读写周期时序图如图3和图4所示。

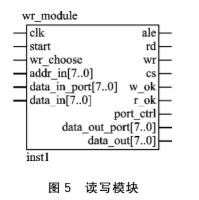

设计时选用状况机的方法,由读写时序图能够看到,与SJA1000读写相关的操控信号有ALE、、、。不管读写,都有必要先输出地址,由接口操控逻辑模块输入地址。AD[7..0]是数据双向流转的,由双端口模块组成,读写模块与之相接口,输入、输出规划分隔。读写模块在与接口操控逻辑接口模块相衔接时,输出的数据与输入的数据也规划分隔。相同读写模块的敞开信号与读/写挑选信号也由接口操控逻辑给出。由QuartuslI生成的读写模块如图5所示。

在IDLE状况等候,当4个功用模块中需求运用读写功用时,由接口操控模块操控使该功用模块与读写模块衔接,相应的功用模块输出地址到读写模块,接口操控模块合作给出读写挑选信号,然后进入address状况,输出地址到SJA1000,判别读写挑选信号后,进入读状况或许写状况。在读写子状况只需依照时序图输出ale、cs、wr、rd的值即可,标志信号w_ok标明一次读/写完结。

在SJA1000的读写进程中,对各个信号的持续时刻有着严厉的要求。以读操作为例,信号的有用持续时刻有必要最大为50 ns,因而在规划中,信号坚持低电平的时刻能够比这个时刻长。

2、 接口操控逻辑模块

接口操控逻辑是本体系的中心模块,它与4个功用模块、读写模块相衔接,由一个状况机组成,即体系的主状况机。在状况机的不同状况中,操控读写状况机与对应的功用模块相衔接,3个模块互相合作完结一项功用。QuartuslI生成的模块图如6所示。

每一个功用模块都有对应的接口信号,而data_in_infer、addr_out_infer、data_in_infer、w_ok_in、r_ok_in是读写模块的信号接口。

需求留意的是,本体系中运用了主从状况机,即状况机的嵌套。在主状况进入初始化状况机后,当即给出一个enable信号,发动从状况机,并设置一个从状况机的完结信号finish(高电平有用),且初始值为低,然后在主状况机不断的检测finish信号,假如finish为高,则进入下一个状况,查询状况。而在从状况机中,则不断地检测enable信号,假如为高,则开端作业,当完结从状况机后,将finish信号置高。如此就完结了主从状况机的互动。接口操控逻辑模块中的start、end信号即为体系主从状况机互动信号。

3 、初始化模块

初始化模块的功用是完结SJA1000的初始化。CAN2.0B标准答应SJA1000作业在两种形式,即BasicCAN形式和PeliCAN形式,上电默以为BasicCAN形式。在两种形式下都需求对SJA1000的形式寄存器CR、检验码寄存器ACR、检验屏蔽寄存器AMR、总线守时寄存器BTR0、BTR1和输出操控寄存器OCR写入操控指令。

在本规划中,借用ROM的思维,将需求读写的寄存器地址和数据一致编码,固化存储起来,对SJA1000进行读写时,只需求依照必定的次序读出数据和地址,输出到即可。

4 、位查询模块

位查询模块首要功用是在SJA1000转入作业形式后能够读取存在承受缓冲区RXFIFO的帧信息,在本规划中读取帧信息选用了查询方法,即不断地查询SJA1000状况寄存器SR的RBS位,假如查询到RBS位为“1”,即标明接纳缓冲区满,RXFIFO中有可用信息,此刻将转入数据处理模块,由数据处理模块进行数据读入,并进行处理。在查询进程中,对SJA1000的状况寄存器进行了读操作。

5、 数据处理模块

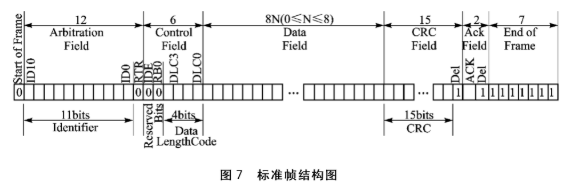

数据处理模块功用是从SJA1000的缓冲区读入数据,并作处理。在读入数据时,只需将输出的地址定位到SJA1000接纳缓冲区的数据场顺次将数据从缓冲区读入即可。在CAN总线的通讯中,发送的为帧信息,其数据帧结构如图7所示。

在对数据进行处理时,前16位为ID,有用的数据是在帧中的数据场(Data Field)中,因而只需略过前16位,对后边最多8个字节的数据进行处理,分配到步进电机的引脚上即可。

6、 缓冲区开释模块与双端口模块

在缓冲区的数据被读入后,需求对缓冲区的数据清零,为后续的数据读入做准备。本质上仍是对SJA1000的指令寄存器(CMR)写操作。在状况寄存器与接纳缓冲区相关的位为RRB,置1即可开释缓冲区,这样就会导致接纳缓冲区内的另一条信息当即有用,然后进入下一帧数据的数据查询、处理进程。

在本规划中,输出的数据引脚为双向引脚,规划成三态输出,这是由于双向端口在完结输入功用时,有必要使端口处于高阻态,不然外部数据不能正确读入。

其规划要害在于,实体部分有必要对端口特点进行声明,端口特点有必要为inout类型,在结构体对输出信号进行有条件的高阻操控。

结语

CAN总线接口操控器由VHDL言语描绘,易于修正和移植,能够将几个软核集成到一个FPGA芯片上去,具有单片机所没有的优势,在轿车范畴具有杰出的运用远景。

责任编辑:gt