1 导言

在数字中频接纳机中,把A/D转化提前到中频部分,为确保A/D转化的动态规模和体系带宽,要求低噪声扩大器和主动增益操控AGC(Automatic Gain Control)电路能够供给大动态规模的主动增益操控。AGC体系由可变增益扩大器和反应回路组成。反应回路从可变增益扩大器的输出中提取起伏主动调理可变增益扩大器的增益,当输入可变增益扩大器的信号起伏增大时,反应回路操控其增益按必定联系减小;减小时,其增益则按必定联系增大。这样不管输入信号的强弱,经AGC扩大后都能得到电平根本安稳的输出信号,然后确保体系的动态规模。数字AGC的反应部分由数字处理完结,与模仿AGC比较,下降调试难度并且增强了安稳性、收敛性和准确性。

2 数字AGC的原理与规划

选用ADI公司的可变增益扩大器、数字可控增益扩大器和FPGA完结大动态规模的主动增益操控,这两个增益扩大器均选用ADI公司的先进工艺技术,且能供给准确的线性扩大,受温度影响很小。

图1为数字AGC体系原理框图,包含可变增益扩大器AD603、数字可控增益扩大器AD8320、A/D转化器AD9220、D/A转化器AD7801,而FPGA用于完结串行转并行以及依据AD9220的ORT指示引脚进行大动态规模的主动增益操控。

图1中,AD603是电压可控增益扩大器,增益由GPOS和GNEG引脚电压差确认。当GNEG=0.5V,GPOS在0~1 V改变时,AD603增益为-lO~30 dB,增益线性改变率为25 mV/dB。AD7801是8 bit D/A转化器,其8 bit操控寄存器由FPGA操控CS和WR信号写入,为AD603的GPOS端口供给增益操控电压,输出电压为0~2.5 V。通过电阻网络后输出电压变为0~1 V,完结AD603的增益可控。AD8320是数字可控增益扩大器,具有一个8 bit串行输入操控端口,可完结256个可编程增益设置,增益与8 bit串行操控字Code的联系为:

Gain(dB)=20log10(0.077×Code+0.316) (1)

式中,Code的规模为0~255。

该操控接口支撑SPI输入操控规范,包含串行输入字,时钟和使能信号,增益改变为-10~26 dB,可到达36 dB的输出增益规模,8 bit串行输入字随8个CLK上升沿送入移位寄存器(高位在前),在这8个时钟周期内,使能信号为低时,不更新本来的操控字。通过8个时钟周期整个新的操控字悉数送入移位寄存器后,使能信号变为高,此刻,数据锁存,操控字更新,内部时钟屏蔽,制止新的操控字输入。

因为AD603的操控字为电压,而AD8320的操控字为8bit操控字,为运用同一个操控字一起操控两个增益的改变,以到达增大AGC动态规模的意图。因而,将FPGA发生的8bit串行操控字:一方面经串行转并行运算送入8 bit D/A转化器AD7801完结数模转化,然后由电压操控字操控AD603的增益改变;另一方面则选用8 bit串行操控字操控AD8320的增益改变,这样由AD603和AD8320一起操控信号的AGC,当操控字从0~255改变时,理论增益从- 20~56 dB,因而,到达76 dB的动态规模。

AD9220是12 bit高速A/D转化器,其输出规模指示OTR信号和最高位指示MSB位的真值表和逻辑联系如表1所列。

当模仿输入信号在A/D转化规模内时,OTR引脚发生低电平指示;当模仿输入信号电平溢出时,OTR引脚发生高电平指示;假如此刻MSB位为低,则表明模仿输入信号电平下溢出,此刻应该增大AGC;MSB位为高,则表明模仿输入信号电平上溢出。FPGA依据OTR信号和MSB位对AGC进行设置和调整。 OTR引脚将坚持高电平,直到模仿输入被调整在A/D转化规模内且完结新的A/D转化。

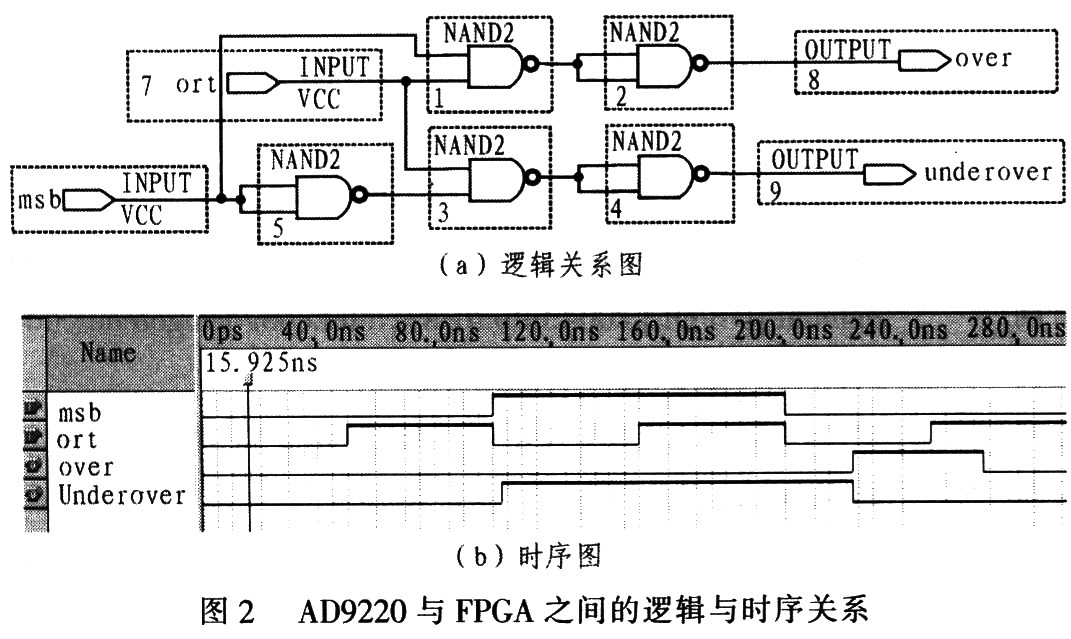

依据真值表得到AD9220的输出OTR信号和MSB位与FPGA输入信号OVER和UNDEROVER具有图2所示的逻辑和时序联系,其间,逻辑联系图 2a也反映了AD9220的输出OTR信号和MSB位与FPGA的输入信号OVER和UN-DEROVER之间的衔接联系。

3 试验及仿真成果

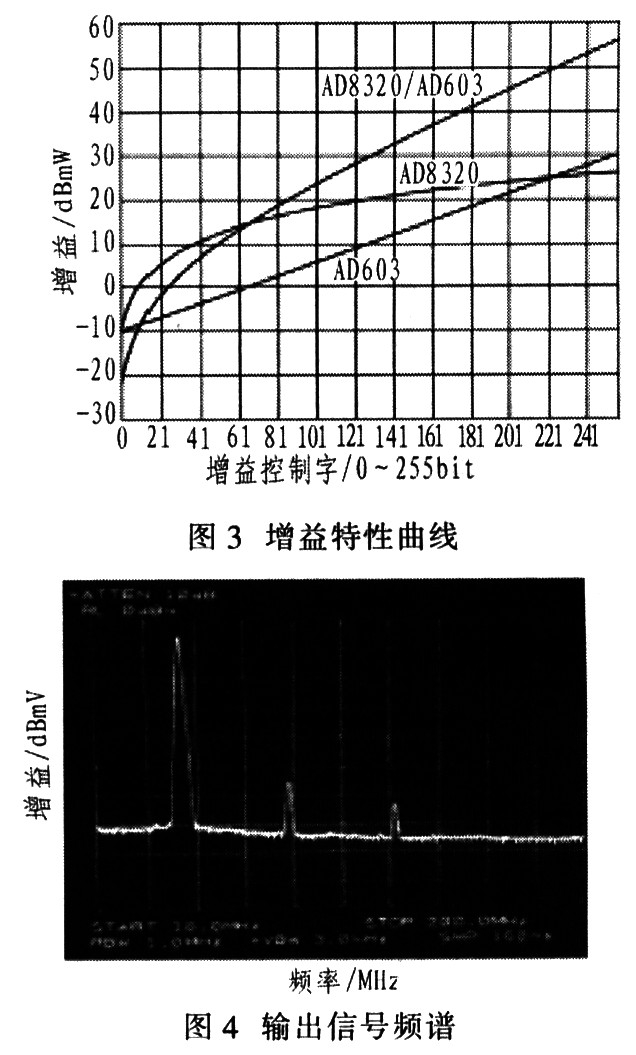

AD603动态规模为40 dB且增益由GPOS和GNEG引脚的电压差确认,并非由数字操控,而AD8320增益由数字操控,但动态规模只要36 dB。体系规划特色在于用同一个操控字一起更新可变增益扩大器AD603和数字可控增益扩大器AD8320,这样,当操控字从0~255改变时,理论上增益为-一20~56 dB,到达76 dB的大动态规模且增益由数字操控字决议。图3为独自的AD8320、AD603以及由同一操控字一起更新AD8320和AD603时操控字与增益的改变联系,能够看出该体系在信号很小时并不非常有用,所以实践AGC的动态规模达不到76 dB,图4为输出信号频谱图,在频率为42 MHz时,最大增益可达61 dB。

数字AGC的功用主要由FPGA程序规划完结,该体系中送入两个扩大器操控字SDATA,由FPGA依据AD9220的输出规模指示端OTR信号和最高位指示端MSB位给出,仿真成果如图5所示。

可见,当A/D转化器的输入上溢出时,FPGA输出8 bit操控字到反应回路,操控增益字从255逐步减小,直到A/D转化器的输入下降到其动态规模之内,上溢出标志OVER为0,此刻操控字为247,如图 5a所示;当A/D转化器的输入下溢出时,FPGA输出8 bit操控字到反应回路,操控增益从前次锁存的操控字247逐步增大,直到A/D转化器的输入增大到其动态规模之内,下溢出标志UNDER-OVER为 0,此刻操控字为255,如图5b所示。这样使不在A/D转化器动态规模之内的输入信号在经数字AGC后,在A/D转化器的输入端都能得到电平根本安稳的信号,然后确保体系的动态作业规模。

4 结束语

该体系规划的立异之处在于选用可变增益扩大器AD603、数字可控增益扩大器AD8320和FPGA完结大动态范同的主动增益操控,充分使用AD9220的两个指示输入信号规模的输出端口,使用FPGA编程,一起操控可变增益扩大器和数字可控增益扩大器,即用同一个操控字一起操控两个增益改变,到达增大AGC动态规模的意图,机理简略,易于完结。该体系规划在必定程度上克服了传统AGC存在的缺点,因为操控回路选用FPGA完结,所以响应和收敛速度更快,功能更安稳,然后简化电子设备的调试,进步电子设备接纳才能和接纳机的作业功能。