导言

数字信号在传输进程中或许遭到各种搅扰及信道传输特性不抱负的影响而使信号产生过错, 然后接收到过错的信息。为了完结数字体系在传输进程中的可靠性, 简直一切的现代通讯体系都把纠错编码作为一个根本组成部分。Reed-So lomon (RS)码是现在最有用、使用最广的过失操控编码之一,是一类具有很强纠错才能的多进制BCH 码, 它既能够纠正突发过错, 也能够纠正随机过错。RS 码首要使用于实时性较高的移动通讯体系、深空通讯、数字卫星电视、磁记录体系等方面。

现在对RS 编码器的规划首要限制于单一码长和固定纠错才能的RS 码编码器规划。本文提出的这种码长可变、纠错才能可调的RS 编码器是把常用的RS (7, 3) 码、RS (15, 11) 码、RS (15, 9) 码在一个编码电路中完结, 把它做成IP 核, 这样既能够大大地减少了芯片的面积并且给用户供给了便利,又有很大的挑选空间。该编码电路选用根据多项式乘法理论GF (2m ) 上的m 位快速有限域乘法的办法, 使电路的编码速度有了很大的进步。本文规划的编码器的最高作业频率可到达100MHz, 彻底满意无线通讯中,语音通讯和数据通讯的数据传输速率为几百kbp s 的要求。

编码算法选取

一般来说, RS 码能够用(n, k , t) 三个参数来表明, 其间n 表明码字长度, k 表明信息位长度, t 为纠错才能, 满意联系: t= (n- k )/2。RS 码的一切元素都是界说在GF (2m ) 上, 其间有:m = log2n。关于不同的m 对应着一个来源多项式, 从来源多项式就能够得到有限域各元素。

RS (7, 3) 码的有限域见表1。

RS 编码的生成多项式界说为:“

所以能够得到各码的生成多项式:

RS (7, 3) 码:

g (x ) = x 4 + a3x 3 + x 2 + ax + a3

RS (15, 11) 码:

g (x ) = x 4 + a13x 3 + a6x 2 + a3x + a10

RS (15, 9) 码:

g (x ) = x 6 + a10x 5 + a14x 4 + a4x 3 +a6x 2 + a9x + a6

用m (x ) 表明信息码字多项式, c (x ) 表明编码后的码字多项式, 则RS 码的编码进程能够用下面编码多项式来表明:

c (x ) = m (x ) x n- k + [m (x ) x n- k ]modg (x )

上式中, [m (x ) x n- k ]modg (x ) 是求余运算, 得到是校验位。

RS 编码器的硬件完结进程, 便是运用电路来完结上述编码多项式中信息位多项式k (x ) 与x n- k的乘法运算及k (x ) x n- kmodg (x ) 的求余运算的进程。下面将具体评论编码电路的构成及作业原理。

编码电路的完结

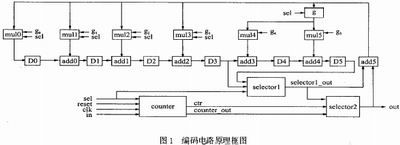

RS编码电路的求余运算能够用n- k 级的移位寄存器来完结, 因而能够选取6 级的移位寄存器; 信息位的输入个数用计数器来操控, 能够加一挑选端来操控计数器是对哪一种码字进行编码计数; 信息位与校验位的输出能够用挑选器来切换。因而咱们能够得到编码电路的原理框图如图1。

在图1 的电路中, 一切的信息数据传输均选用4 位比特宽的传输。Reset 是体系复位信号。电路的作业原理描绘如下:

(1) 当sel 置为01 时, 编码电路处于RS (7, 3)码的编码状况。因为RS (7, 3) 码的信息用3 位的二进制表明, 所以数据线的最高位为零, 只要低3 位起作用。

A 编码前首先给电路一个reset 复位信号,使计数器和移位寄存器中的触发器处于零状况, 复位选用异步复位。

B 输入信息(m 2, …,m 0 ) , 计数器开端计数,每输入一个信息位, 计数器计一次数, 然后输出。此刻, selecto r2 的输出与计数器的输出端相接, 因而信息位一方面从编码电路的输出端输出, 另一方面送入移位寄存器电路进行求余运算。

C 当3 位信息位输入完后, 计数器输出一个操控信号ct r, 它是操控信息位与校验位的输出, 此刻selcto r2 的输出与selecto r1 的输出端相接,add5 的两个输入端均为selecto r1 的输出端, 因为有限域加法不考虑各位之间的进位, 因而add5 的输出为0, 然后各乘法器m u l 的输出为0, 所以移位寄存器中的校验位会一次输出。所以校验位(D 3,…,D 0) 一次输出。校验位输出后寄存器和计数器回到零状况。因而得到编码后的码字为(m 2, .,m 0,D 3, …,D 0)。

D 因为RS (7, 3) 码编码电路的求余运算只需要4 级的移位寄存器来完结, 因而开关K 断开,后边两级移位寄存器不作业, 这样就降低了电路的功耗。A dd5 的输入端接D3 的输出端。

(2) 当sel 置为10 时, 编码电路处于RS (15,11) 码的编码状况, 在编码前要给电路一个复位信号。进程与上面相同, 编码后得到码字为(m 10, …,m 0, D 3, …,D 0)。相同RS (15, 11) 码编码电路的求余运算只需要4 级的移位寄存器来完结, 因而K断开, add5 的输入端接D3 的输出端。

(3) 当sel 置为11 时编码电路处于RS (15, 9)码的编码状况, 编码前, 给电路一个复位信号。编码后便可得到码字为(m 8, …, m 0, D 3, …, D 0 )。RS(15, 9) 码编码电路的求余运算要6 级的移位寄存器来完结。因而K 注册, add5 的输入端接D5 的输出端。

在编码电路中乘法器选用了根据多项式乘法理论GF (2m ) 上的m 位有限域乘法的办法, 大大地进步了电路的运算速度。

快速有限域乘法器完结:

快速有限域乘法的完结思路如下, 以RS (7, 3)码为例:

因而就能够完结快速有限域乘法器, 这样对电路的运算速度将会有很大的进步。因为RS (15,11) 码和RS (15, 9) 码根据同一个有限域GF (24 ) ,因而它们的乘法器相同。当sel 置为01 时, 乘法器作业在GF (23 ) 的乘法状况, 当sel 置为10 或11时, 乘法器作业在GF (24) 的乘法状况。只不过作业在GF (23 ) 状况时乘法器输入输出端的第4 位为0。

电路仿真及测验

编码电路模块能够表明为:

sel 是编码电路的挑选端, clk 是时钟输入端,reset 是体系复位端, in 是信息输入端, ou t 是码字输出端。

用V erilog HDL 言语编写电路的代码后, 再用Cadence 公司的NC V erilog HDL 仿真东西进行仿真, 得到各种编码的仿真成果。

A ) 给reset 一个复位信号, 使电路处于零状况, sel 置为01 时, 输入信息电路开端编码。输入信息位为(0, 1, 2) , 编码后得到校验位(2, 3, 1, 3) , 因而输出端输出码字为(0, 1, 2, 2, 3, 1, 3)。然后再输入信息位, 循环进行编码。输出波形如图3 所示。

B) 给reset 一个复位信号, sel 置为10 时, 输入信息电路开端编码。输入信息为(0, 1, 2, 3, 4, 5, 6,7, 8, 9,A ) , 编码后得到校验位(C, E, 8, 3) , 所以输出端输出码字为(0, 1, 2, 3, 4, 5, 6, 7, 8, 9,A , C, E,8, 3)。输入端再次输入信息, 循环进行编码。输出波形如图4 所示。

C) 给reset 一个复位信号, sel 置为11 时, 输入信息电路开端编码。输入信息为(0, 1, 2, 3, 4, 5,6, 7, 8) , 编码后得到校验位(B, C, 0, 5, 7, 8) , 所以输出端输出码字为(0, 1, 2, 3, 4, 5, 6, 7, 8,B, C, 0,5, 7, 8)。输入端再次输入信息, 循环进行编码。

仿真完结后, 选用Xilinx 的FPGA 板, 主芯片为SPARTAN II XC2SPQ 208 进行验证, 输入信息与仿真输入的信息共同, 然后用逻辑分析仪观测输出成果。

A ) 给reset 一个复位信号后, 使电路作业在RS (7, 3) 码的编码状况。用逻辑分析仪观测输入与输出的成果如下图6 所示, 虚线圈起来的(0, 1, 2,2, 3, 1, 3) 表明一个完好的输出码字。

B) 先使电路复位, 然后让电路作业在RS (15,11) 码的编码状况, 用逻辑分析仪观测输入与输出成果如下图7 所示, 虚线圈起来的(0, 1, 2, 3, 4, 5,6, 7, 8, 9,A , C, E, 8, 3) 表明一个完好的输出码字。

C) 电路复位后, 使它作业在RS (15, 9) 码的编码状况, 用逻辑分析仪观测成果如下图8 所示, 虚线圈起来的(0, 1, 2, 3, 4, 5, 6, 7, 8,B, C, 0, 5, 7, 8)表明一个完好的输出码字。

从上面的仿真波形和测验成果能够看到他们的输出成果共同, 验证了规划的正确性。

电路参数

用Xilinx 公司的Pro ject Navigator 归纳东西对电路代码进行归纳后, 得到电路的等效门单元数1339; 测得电路的静态功耗为12.50 mW , 最高作频率为100MHz。

定论

提出了一种码长可变、纠错才能可调的RS 码编码器, 它处理了以往RS 编码器只能对单一码长和固定纠错才能编码的限制, 一起选用快速有限域乘法的办法进步了电路的运算速度。规划后经过在FPGA 上测验, 验证了规划的正确性。