ARM存储体系有十分灵敏的体系结构,能够习惯不同的嵌入式运用体系的需求。ARM存储器体系能够运用简略的平板式地址映射机制(就像一些简略的单片机相同,地址空间的分配办法是固定的,体系中各部分都运用物理地址),也能够运用其他技能供给功用更为强壮的存储体系。比方:

· 体系或许供给多种类型的存储器材,如FLASH、ROM、SRAM等;

· Caches技能;

· 虚拟内存和I/O地址映射技能。

大多数的体系经过下面的办法之一完结对杂乱存储体系的办理。

· 运用内存映射技能完结虚拟空间到物理空间的映射。这种映射机制对嵌入式体系十分重要。一般嵌入式

· 引进存储维护机制,增强体系的安全性。

· 引进一些机制确保将I/O操作映射成内存操作后,各种I/O操作能够得到正确的成果。在简略存储体系中,

在ARM体系中,要完结对存储体系的办理一般是运用协处理器CP15,它一般也被称为体系操控协处理器(System Control Coprocessor)。

ARM的存储器体系是由多级构成的,每级都有特定的容量和速度。图1显现了存储器的层次结构。

① 寄存器。处理器寄存器组可看作是存储器层次的顶层。这些寄存器被集成在处理器内核中,在体系中供给最快的存储器拜访。典型的ARM处理器有多个32位寄存器,其拜访时刻为ns量级。

图1 存储器的层次结构

② 紧耦合存储器TCM。为补偿Cache拜访的不确认性增加的存储器。TCM是一种快速SDRAM,它紧挨内核,而且确保取指和数据操作的时钟周期数,这一点对一些要求确认行为的实时算法是很重要的。TCM坐落存储器地址映射中,可作为快速存储器来拜访。

③ 片上Cache存储器的容量在8KB~32KB之间,拜访时刻大约为10ns。

④ 高功用的ARM结构中,或许存在第二级片外Cache,容量为几百KB,拜访时刻为几十ns。

⑤ DRAM。主存储器或许是几MB到几十MB的动态存储器,拜访时刻大约为100ns。

⑥ 后援存储器,一般是硬盘,或许从几百MB到几个GB,拜访时刻为几十ms。

留意TCM和SRAM在技能上相同,但在结构排列上不同;TCM在片上,而SRAM在板上。

协处理器CP15

ARM处理器支撑16个协处理器。在程序碑文过程中,每个协处理器疏忽归于ARM处理器和其他协处理器的指令。当一个协处理器硬件不能碑文归于它的协处理器指令时,将发生一个未界说指令反常间断,在该反常间断处理程序中,能够经过软件模仿该硬件操作。比方,假如体系不包含向量浮点运算器,则能够挑选浮点运算软件模仿包来支撑向量浮点运算。

在一些没有规范存储办理的体系中,CP15是不存在的。在这种状况下,针对协处理器CP15的操作指令将被视为未界说指令,指令的碑文成果不行预知。

CP15包含16个32位寄存器,其编号为0~15。实际上关于某些编号的寄存器或许对应多个物理寄存器,在指令中指定特定的标志位来委任这些物理寄存器。这种机制有些类似于ARM中的寄存器,当处于不同的处理器形式时,某些相同编号的寄存器对应于不同的物理寄存器。

· 寄存器的拜访类型(只读/只写/可读可写)。

· 不同的拜访引发的不同功用。

· 相同编号的寄存器是否对应不同的物理寄存器。

· 寄存器的详细效果。

CP15寄存器拜访指令

一般对协处理器CP15的拜访运用以下两种指令。

MCR:将ARM寄存器的值写入CP15寄存器中;

MRC:将CP15寄存器的值写入ARM寄存器中。

留意经过协处理器拜访指令CDP、LDC和STC指令对协处理器CP15进行拜访将发生不行预知的成果。

其间,CDP为协处理器数据操作指令,这个指令初始化一些与协处理器相关的操作;

LDC为一个或多个字的协处理器数据读取指令,此指令从存储器读取数据到指定的协处理器中;

STC为一个或多个32位字的协处理器数据写入指令,此指令初始化一个协处理器的写操作,从给定的协处理器把数据传送到存储器中。

指令MCR和MRC指令拜访CP15寄存器运用通用语法。

语法格局为:

MCR{《cond》} p15,《opcode1=0》,《Rd》,《CRn》,《CRm》{,《opcode2》}

MRC{《cond》} p15,《opcode1=0》,《Rd》,《CRn》,《CRm》{,《opcode2》}

其间:

《cond》为指令的碑文条件。当《cond》条件域为空时,指令无条件碑文;

《opcode1》在规范的MRC指令中,为协处理器的《opcode1》,即操作数1。关于CP15来说,此操作数恒为0,即0b000。当针对CP15的MRC指令中《opcode1》不为0时,指令的操作成果不行预知;

《Rd》为ARM寄存器,在ARM和协处理器交流数据时运用。在MRC指令中作为意图寄存器,在MCR中作为源寄存器。

留意r15不能作为ARM寄存器呈现在MRC或MCR指令中,假如r15作为《Rd》呈现在这里,那么指令的碑文成果不行预知。

《CRn》是CP15协处理器指令中用到的首要寄存器。在MRC指令中为源寄存器,在MCR中为意图寄存器。CP15协处理器的寄存器c0、c1、…、c15均可呈现在这里。

《CRm》是附加的协处理器寄存器,用于委任同一个编号的不同物理寄存器和拜访类型。当指令中不需求供给附加信息时,将《CRm》指定为C0,不然指令的操作成果不行预知。

《opcode2》供给附加信息,用于委任同一个编号的不同物理寄存器,当指令中没有指定附加信息时,省掉《opcode2》或许将其指定为0,不然指令的操作成果不行预知。

MCR和MRC指令只能操作在特权形式下,假如处理器运转在用户形式,指令的碑文成果不行预知。

留意在用户形式下,假如要拜访体系操控协处理器,一般的做法是由操作体系供给SWI软间断调用来完结体系形式的切换。我们不同类型的ARM处理器对此办理不同很大,所以主张用户在运用时将SWI作为一个独立的模块来办理并向上供给通用接口,以屏蔽不同类型处理器之间的差异。

例1给出了一个典型的运用SWI进行形式切换的比如。

【例1】

典型的在SWI中进行形式切换的比如。运用此例,调用SWI 0来完结体系形式切换。

EHT_SWI

LDR sp,=EHT_Exception_Stack ;更新SWI仓库指针

ADD sp,sp,#EXCEPTION_SIZE ;得到栈顶指针

STMDB sp!,{r0-r2,lr} ;保存程序中用到的寄存器

MRS r0,SPSR ;得到SPSR

STMDB sp!,{r0} ;坚持SPSR

LDR r0,[lr,#-4] ;核算SWI指令地址

BIC r0,r0,#0xFF000000 ;提取间断向量号

CMP r0,#MAX_SWI ;检测间断向量规模

LDRLS pc,[pc,r0,LSL #2] ;假如在规模内,跳转到软间断向量表

B EHT_SWI_Exit ;为界说的SWI指令出口

EHT_Jump_Table

DCD EHT_SU_Switch

DCD EHT_Disable_Interrupts

;用户可在此增加更多的自界说软间断,在此SWI0作为体系保存的软间断,调用例程EHT_SU_Switch,来进行形式切换

;*********************************************************************************

EHT_SU_Switch

MMU_DISABLE ;转化前禁用MMU

LDMIA sp!,{r0} ;从仓库中取出SPSR

B%&&&&&% r0,r0,#MODE_MASK ;铲除形式位

ORR r0,r0,#SYS_MODE ;设置程序状况字的supper形式位

STMDB sp!,{r0} ;重新将SPSR放入仓库

B EHT_SWI_Exit

EHT_Disable_Interrupts

LDMIA sp!,{r0} ;从仓库中读出SPSR

ORR r0,r0,#LOCKOUT ;制止间断

STMDB sp!,{r0} ;存储SPSR到间断

; B EHT_SWI_Exit

EHT_SWI_Exit

LDMIA sp!,{r0} ;从仓库中读出SPSR

MSR SPSR_cf,r0 ;将SPSR放入SPSR_cf

LDMIA sp!,{r0-r2,pc}^ ;寄存器出栈并回来

END

1.2 CP15中的寄存器

表1给出了CP15首要寄存器的功用和效果。

表1 CP15寄存器

|

寄存器编号 |

根本效果 |

在MMU中的效果 |

在PU中的效果 |

|

0 |

ID编码(只读) |

ID编码和cache类型 |

|

|

1 |

操控位(可读写) |

各种操控位 |

|

|

2 |

存储维护和操控 |

地址转化表基地址 |

Cachability的操控位 |

|

3 |

存储维护和操控 |

域拜访操控位 |

Bufferablity操控位 |

|

4 |

存储维护和操控 |

保存 |

保存 |

|

5 |

存储维护和操控 |

内存失效状况 |

拜访权限操控位 |

|

6 |

存储维护和操控 |

内存失效地址 |

维护区域操控 |

|

7 |

高速缓存和写缓存 |

高速缓存和写缓存操控 |

|

|

8 |

存储维护和操控 |

TLB操控 |

保存 |

|

9 |

高速缓存和写缓存 |

高速缓存确认 |

|

|

10 |

存储维护和操控 |

TLB确认 |

保存 |

|

11 |

保存 |

|

|

|

12 |

保存 |

|

|

|

13 |

进程标识符 |

进程标识符 |

|

|

14 |

保存 |

|

|

|

15 |

因不同规划而异 |

因不同规划而异 |

因不同规划而异 |

|

opcode_2编码 |

对应的标识符号寄存器 |

|

0b000 |

主标识符寄存器 |

|

0b001 |

cache类型标识符寄存器 |

|

其他 |

保存 |

(1)主标识符寄存器

当协处理器指令对CP15进行操作,而且操作码opcode=2时,处理器的主标识符将被读出。从主标识符中,能够确认ARM体系结构的版别类型。一起也能够参阅由芯片出产厂商界说的其他标识符,来取得更详细的信息。

在主标识信息中,bit[15:12]委任了不同的处理器版别:

· 假如bit[15:12]为0x0,阐明处理器是ARM7之前的处理器;

· 假如bit[15:12]为0x7,阐明处理器为ARM7处理器;

· 假如bit[15:12]为其他值,阐明处理器为ARM7之后的处理器。

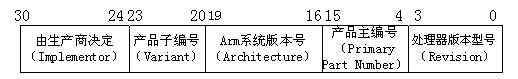

关于ARM7之后的处理器,其标识符的编码格局如图2所示。

其间各部分的编码意义阐明如下。

bit[3:0]:包含出产厂商界说的处理器版别类型。

bit[15:4]:出产厂商界说的产品主编号,或许的取值为0x0~0x7。

bit[19:16]:ARM体系的版别号,或许的取值如表3(其他值由ARM公司保存将来运用)所示。

图2 ARM7之后处理器标识符编码

表3 bit[19:16]与ARM版别号

或许的取值

0x1

0x2

0x3

0x4

0x5

bit[23:20]:出产厂商界说的产品子编号。当产品主编号相一起,运用子编号委任不同的产品子类,如产品中不同的cache的巨细。

bit[31:24]:出产厂商的编号现已界说的如表4所示。其他的值ARM公司保存将来运用。

表4 bit[31:24]值与ARM出产厂商

或许的取值

0x41

0x44

0x69

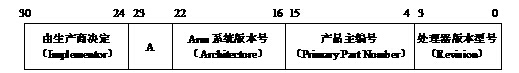

关于ARM7体系的处理器,其主标识符的编码如图3所示。

图3 ARM7处理器标识符编码

其间各部分的意义阐明如下。

bit[3:0]:包含出产厂商界说的处理器版别类型。

bit[15:4]:出产厂商界说的产品主编号,其最高4位的值为0x7。

bit[22:16]:出产商界说的产品子编号。当产品的主编号相一起,运用子编号委任不同的产品子类,如产品中不同的产品子类、不同产品中高速缓存的巨细。

bit[23]:ARM7处理器支撑下面两种ARM体系的版别号。0x0代表ARM体系版别3;0x1代表ARM体系版别4T。

bit[31:24]:出产厂商的编号已界说的如表5所示,其他的值ARM公司保存将来运用。

表5 bit[31:24]值与ARM出产厂商

或许的取值ARM芯片出产厂商

0x41(A)ARM公司

0x44(D)Digital Equipment

0x69(i)Intel公司

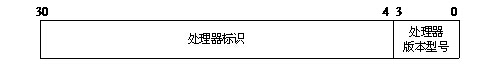

关于ARM7体系的处理器,其主标识符的编码如图4所示。

图4 ARM7之前处理器标识符编码

其间各部分的意义阐明如下。

bit[3:0]:包含出产厂商界说的处理器版别类型。

bit[31:4]:处理器标识符及其意义如表6所示。

表6 ARM之后处理器标识符与意义

处理器标识符含 义

0x4156030ARM3(体系版别2)

0x4156060ARM600(ARM体系版别3)

0x4156061ARM610(ARM体系版别3)

0x4156062ARM620(ARM体系版别3)

(2)Cache类型标识符寄存器

如前所述,关于指令MRC来说,当协处理器寄存器为r0,而第二操作数opcode2为0b001时,指令读取值为Cache类型,即能够用下面的指令将处理器的Cache类型标识符寄存器的内容读取到寄存器r0中。

MRC P15,0,r0,c0,c0,1

Cache类型标识符界说了关于Cache的信息,详细内容如下所述。

· 体系中的数据Cache和指令Cache是分隔的仍是一致的。

· Cache的容量、块巨细以及相联特性。

· Cache类型是直(write-through)写仍是回写(write-back)。

· 关于回写(write-back)类型的Cache怎么有用铲除Cache内容。

· Cache是否支撑内容确认。

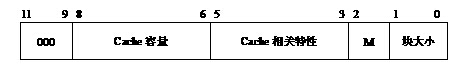

Cache类型标识符寄存器各操控字段的意义编码格局如图5所示。

图5 Cache特点寄存器标识符编码格局

其间各操控字段的意义阐明如下。

特点字段(ctype):指定没有在S位、数据Cache相关特点位、指令Cache相关特点类中指定的特点,其详细编码参见表7。

表7 Cache类型标识符寄存器特点字段意义

编 码

0b0000

0b0001

0b0010

0b0110

0b0111

S位:界说体系中的数据Cache和指令Cache是分隔的仍是一致的。假如S=0,阐明指令Cache和数据Cache是一致的,假如S=1,则阐明数据Cache和指令Cache是别离的。

数据Cache相关特点:界说了数据Cache容量、行巨细和相联(associativity)特性(假如S≠0)。

指令Cache相关特点:界说了指令Cache容量、行巨细和相联(associativity)特性(假如S≠0)。

数据Cache相关特点和指令Cache相关特点别离占用操控字段[23:12]和[11:0],它们的结构相同,图6以指令Cache为例,显现了编码结构。

图6 指令Cache编码结构

其间,各部分的意义阐明如下。

bit[11:9]:保存用于将来运用。

bit[8:6]:界说Cache的容量,其编码格局及意义如表8所示。

表8 类型标识符寄存器操控字段bit[8:6]意义

编 码

0b000

0b00

0b010

0b011

0b100

0b101

0b110

0b111

bit[1:0]:界说Cache的块巨细,其编码格局及意义如表9所示。

表9 类型标识符寄存器操控字段bit[1:0]意义

编 码

0b00

0b01

0b10

0b11

bit[5:3]:界说了Cache的相联特点,其编码格局及意义如表10所示。

表10 类型标识符寄存器操控字段bit[5:3]意义

0b001

0b010

0b011

0b1001

0b101

0b110

0b111

1.4 寄存器c1

CP15中的寄存器c1包含以下操控功用:

· 制止/使能MMU以及其他与存储体系有关的功用;

· 装备存储体系以及ARM处理器中相关的作业。

留意在寄存器c1中包含了一些没有运用的位,这些位在将来或许被扩展其他功用时运用。因而为了编写代码在将来更高版别的ARM处理器中仍能够运用,在修正寄存器c1中的位时应该运用“读取-修正特定位-写入”的操作序列。

例2用MRC/MCR指令将协处理器寄存器c1的值进行读取和写入。

【例2】

MRC P15,0,r0,c1,0,0 ;将寄存器c1的值读取到ARM寄存器r0中

MCR P15,0,r0,c1,0,0 ;将ARM寄存器r0的值写入寄存器c1

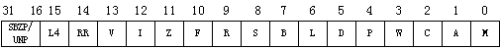

图7显现了寄存器c1的编码格局。

图7 寄存器c1编码格局

寄存器c1各操控字段的意义如表11所示。

表11 寄存器c1中各操控位字段的意义

C1中的操控位含 义

M(bit[0])制止/使能MMU或许MPU

0:制止MMU或许MPU

1:使能MMU或许MPU

假如体系中没有MMU或许MPU,读取时该位回来0,写入时疏忽

A(bit[1])关于能够挑选是否支撑内存拜访时地址对齐查看的体系,本位制止/使能地址对齐查看功用

0:制止地址对齐查看功用

1:使能地址对齐查看功用

对寄存器进行写操作时,疏忽该位

C(bit[2])当数据Cache和指令Cache分隔时,本操控位制止/使能数据Cache。

当数据Cache和指令Cache一致时,该操控位制止/使能整个Cache

0:制止Cache

1:使能Cache

假如体系中不含Cache,读取时该位回来0,写入时疏忽

当体系中Cache不能制止时,读取回来1,写入时疏忽

W(bit[3])制止/使能写缓存

0:制止写缓存

1:使能写缓存

假如体系中不含写缓存,读取时该位回来0,写入时疏忽

当体系中的写缓存不能制止时,读取时该位回来0,写入时疏忽

P(bit[4])关于向前兼容26位ARM处理器,本操控位操控PRGC32操控信号

0:反常间断处理程序进入32位地址形式

1:反常间断处理程序进入26位地址形式

假如体系不支撑向前兼容26位地址,读取该位时回来1,写入时被疏忽

D(bit[5])关于向前兼容26位ARM处理器,本操控位操控DATA32操控信号

0:制止26位地址反常查看

1:使能26位地址反常检测

假如体系不支撑向前兼容26位地址,读取该位时回来1,写入时被疏忽

L(bit[6])关于ARMv3及曾经版别,本操控位能够操控处理器的间断形式

0:挑选前期间断形式

1:挑选后期间断形式

关于今后的处理器读取该位时回来1,写入时疏忽

B(bit[7])关于存储体系一起支撑大/小端(big-endian/little-endian)的ARM处理器,该操控位装备体系运用哪种内存形式

0:运用小端(little-endian)

1:运用大端(big-endian)

关于只支撑小端(little-endian)的体系,读取时该位回来0,写入时疏忽

关于只支撑大端(big-endian)的体系,读取时该位回来1,写入时疏忽

S(bit[8])支撑MMU的存储体系中,本操控位用作体系维护

R(bit[9])支撑MMU的存储体系中,本操控位用作ROM维护

F(bit[10])本操控位由出产厂商界说

Z(bit[11])关于支撑跳转猜测的ARM体系,本操控位制止/使能跳转猜测功用

0:制止跳转猜测功用

1:使能跳转猜测功用

关于不支撑跳转猜测的ARM体系,读取时该位回来0,写入时疏忽

I(bit[12])当数据Cache和指令Cache是分隔的,本操控位制止/使能指令Cache

0:制止指令Cache

1:使能指令Cache

假如体系中运用一致的指令Cache和数据Cache或许体系中不含Cache,读取该位时回来0,写入时疏忽该位

当体系中的指令Cache不能制止时,读取该位回来1,写入时疏忽该位

V(bit[13])支撑高端反常向量表的体系中,本操控位操控向量表的方位

0:挑选0x00000000~0x0000001c

1:挑选0Xffff0000~0xffff001c

关于不支撑高端间断向量表的体系,读取时回来0,写入时疏忽

RR(bit[14])假如体系中Cache的筛选算法能够挑选的话,本操控位挑选筛选算法

0:挑选惯例的筛选算法,如随机筛选算法

1:挑选猜测性的筛选算法,如轮转(round-robin)筛选算法

假如体系中筛选算法不行挑选,写入该位时被疏忽,读取该位时,依据其筛选算法是否能够比较简略地猜测最坏状况回来1或许0

L4(bit[15])ARM版别5及以上的版别中,本操控位能够供给兼容曾经的ARM版别的功用

0:坚持当时ARM版别的正常功用

1:关于一些依据跳转地址的bit[0]进行状况切换的指令,疏忽bit[0],不进行状况切换,坚持和曾经ARM版别兼容

此操控位能够影响以下指令:LDM、LDR和POP

关于ARM版别5曾经的处理器,该位没有运用,应作为UNP/SBZP

关于ARM版别5今后的处理器,假如不支撑向前兼容的特点,读取时该位回来0,写入时疏忽

Bit(bit[31:16])这些位保存将来运用,应为UNP/SBZP