时钟拉伸(Clock stretching)

clock stretching经过将SCL线拉低来暂停一个传输.直到开释SCL线为高电平,传输才继续进行.clock stretching是可选的,实际上大多数从设备不包括SCL驱动,所以它们不能stretch时钟.

从字节级来看,一个设备或许在快速形式下承受数据,可是需求更多的时刻来存储接纳到的字节或许预备即将传输的另一个字节.从机能够以一种握手的处理方式在承受和应对字节后将SCL线拉低来强制使得主机进入wait状况知道从机预备好下一个字节的传输.

从位级来看,I2C总线上的设备能够经过添加每一个时钟的低周期来下降总线时钟.所以每个主机能够习惯这个设备的内部操作速率.

在Hs形式,握手处理只能用在字节等级.

从机地址和R/W bit

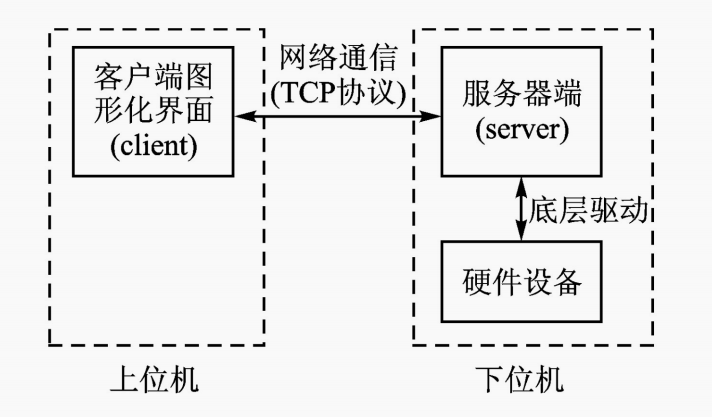

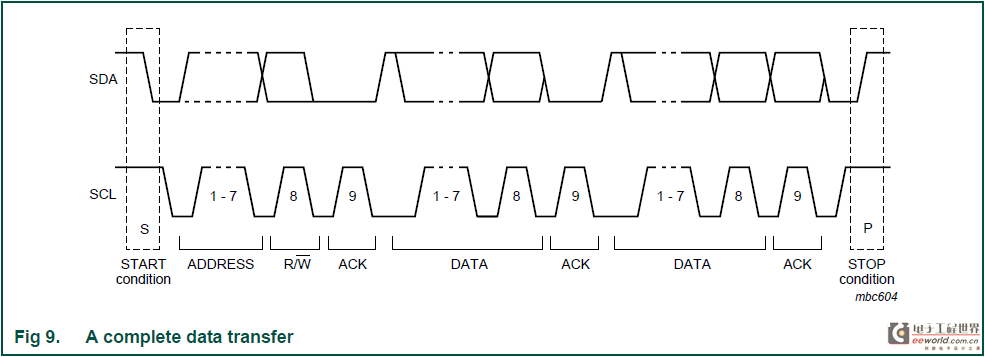

下图是数据传输的格局:

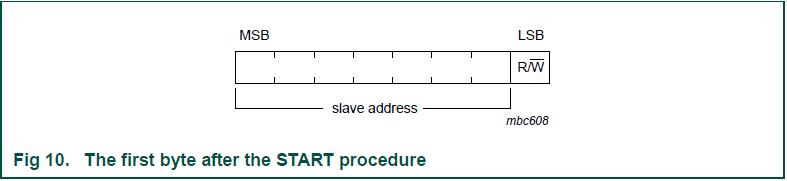

在开端条件(S)后,发送从机地址.地址是7bit,后边的第8bit是数据的读写bit,0表明写,1表明读.详细的看下图:

数据传输被主机发生的停止条件(P)停止.但是,主机也能够无需先发生停止条件,发生一个重复的开端条件(Sr)和寻址另一个从机,

或许的数据传输格局如下:

主-发送器传到从-接纳器.传输方向不变.从-接纳器应对每一个字节.如下:

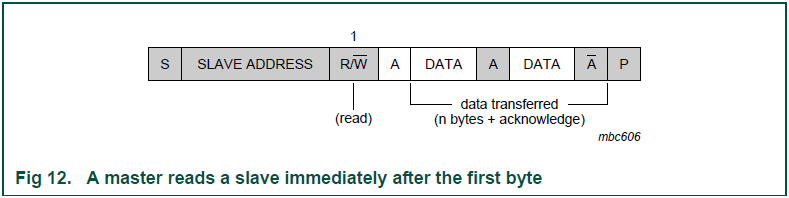

在榜首个字节后主机从从机读数据.榜首个应对后,主-发送器变为主-接纳器而从-接纳器变为从-发送器.榜首个应对仍然是由从机发生的.主机发生余下的应对.主机在发生停止条件之前要发送一个NA.如下:

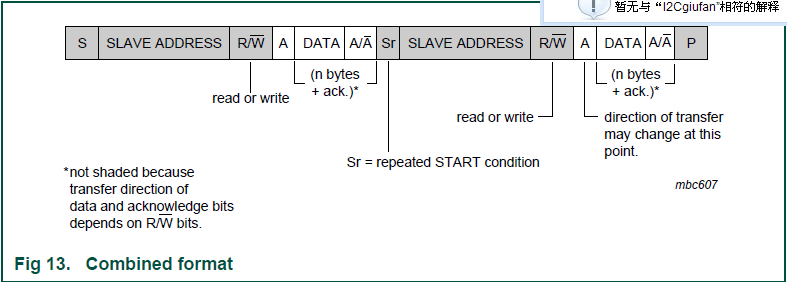

复合形式.在传输过程中改变方向,开端条件和从机地址都要重复,而读写bit要取反.假如主-接纳器发送一个重复的开端条件,那么它在这之前要发送一个NA.

留意:

1.复合形式能够在比方操控串行内存器时用到.在榜首个数据字节时必定要写内存器内部的地址.开开端条件和从地址重复后,数据就开端传输了.

2.主动添加或削减之前拜访的内存方位都由设备的设计者决议.

3.每一个字节后边都跟着一个应对位,在图顶用A或非A来表明.

4.兼容I2C总线的设备在接纳到开端条件或重复开端条件时都必定要重启它们的总线逻辑,即便开端条件都不是正确的格局,它们都希望发送从机地址.

5.开端条件后立马跟着一个停止条件是不合法的格局.许多设备在设计时考虑了这一点,能够处理.

6.连接到总线上的每个设备都由仅有的地址来确认.通常是简略的主从关系,但或许存在多个相同的从机能够一起接纳和呼应,比方说组播.这儿是以NXP的PCA9546A作为比如阐明.(PCA9546A是NXP半导体出产的一款根据I2C总线操控的4通道双向多路复用器和开关。运用PCA9546A能够将一路SCL/SDA输入扩展为4路SCL/SDA输出,在对内部操控寄存器进行相应装备后,可一起挑选一路或多路下行I2C总线与上行I2C总线通讯。)