The realization of digital watermarking based on FPGA

程前 1 ,董长旭 1 ,廖媛媛 2

(1.电子科学与工程学院,四川 成都 610000;

2.电子科技大学,通讯抗干扰技能国家级要点实验室,四川 成都 610000)

摘要:数字水印技能在信息安全、知识产权维护和认证等范畴有着重要的功用和方位。本文依据现场可编程门阵列(FPGA),通过流水线规划,乒乓缓冲和分布式算法,完结8×8矩阵的二维DCT改换,充分运用FPGA的查找表(LUT)和块RAM(BRAM)资源,完结载体图画的快速DCT域改换。原始水印图画通过Arnold改换进行置乱,并与Logistic映射的混沌序列挑选适宜的水印信息嵌入点。终究通过不同的水印进犯来验证本体系的

隐蔽性和鲁棒性。

关键词:水印图画;二维DCT;分布式算法;Arnold置乱;混沌序列

0 导言

跟着通讯技能的飞速发展,数字媒体通讯在信息沟通中得到了广泛的运用。网络信息交流之间的安全和加密等问题引起了高度重视[1],确保信息不被不合法运用和损坏也变得越来越重要。图画数据可承载比文字更多的内容,成为信息传递的重要途径。传统的加密办法首要针对数据传输进程进行维护,而不能彻底处理接纳解密后的安全性问题,而运用信息躲藏技能通过在揭露的载体信息中刺进躲藏的秘要信息后进行数据传输,完结了信息的安全隐秘传输[2]。

数字水印技能能够广泛用于信息安全、知识产权维护和认证等范畴,其通过某一种水印算法,完结将包含秘要信息的水印图画躲藏在传输的载体图画中,而数据接纳方则通过专用解密办法提取水印信息,完结图画数据安全提取和传输[3]。

1 图画水印完结体系全体计划

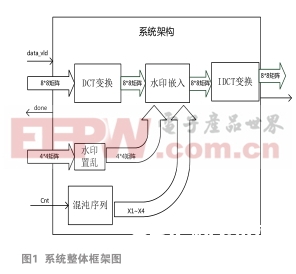

本体系分为水印嵌入和水印提取两个模块,完结将水印图画嵌入载体图画后提取加密水印,全体结构图如图1所示。

2 水印嵌入模块

水印嵌入模块挑选在空间域或改换域进行水印图画嵌入载体图画。首要将200×200的二值水印图画进行置乱处理后,运用混沌序列在800×800载体图画中挑选适宜的水印嵌入方位,在拟定的嵌入规矩指导下进行水印的嵌入。本体系的水印嵌入模块首要包含DCT改换模块、Arnold置乱模块、混沌序列模块等。

2.1.1 二维DCT改换模块

开始的数字水印算法是依据空间域完结,是在嵌入规矩下直接完结水印图画嵌入。尽管空间域嵌入可完结高速改换并下降体系复杂度,可是难以完结较好的鲁棒性和不行感知性。改换域是指通过某一算法,常见的包含离散余弦改换(DCT),离散傅里叶改换(DFT),离散小波改换(DWT)等,将载体图画改换到频域进行水印图画的嵌入,这样可完结高鲁棒性,高安全性的水印不行感知嵌入体系。因为DCT改变是图片JPEG紧缩规范,所以本体系挑选在DCT域进行水印嵌入,完结高抗JPEG紧缩进犯性[4]。

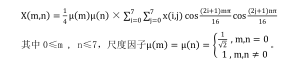

本 系 统 选 择 对 8 0 0 × 8 0 0 的 载 体 图 像 进 行8 × 8 矩 阵 分 块 后 , 形 成 x(i,j) 0 ≤ i < 8, 0 ≤ j < 8的矩阵数据,然后再通过二维DCT得到改换成果X(m,n) 0 ≤ m < 8, 0 ≤ n < 8 ,二维DCT的公式如下:

其间0≤m , n≤7,标准因子。

二维DCT运算算法十分复杂,若用组合逻辑完结将大大影响体系的时序功用,本体系运用其可分化性质,对8×8矩阵每行首要进行一维DCT改变,然后对改换成果每列进行一维DCT即可得到二维DCT改换成果,具体操作进程如下:一维DCT改换公式能够表明为矩阵方式:关于二维DCT改换,其公式能够用矩阵表明为:更进一步,能够将二维DCT改换分化:为了得到更快的作业频率,本体系挑选通过流水线规划改进其时序功用,进步核算功率。缓存时参加乒乓操作改进输入速度和输出速度距离过大的问题,奇妙规划时序添加资源运用率。因为dct模块和转置ram只例化一次,完结最小资源消耗。一维DCT算法根本操作即为8×8矩阵相乘,需求许多的乘累加运算,占用FPGA的专用乘法器资源,所以为了完结资源优化,本体系通过分布式算法,将一维DCT的系数矩阵C 8×8 与输入数据或许的运算成果事前存储在FPGA的BRAM资源中,运用真实的输入行/列数据发生地址进行读操作即可正确完结一维DCT运算。终究本体系完结100个周期内完结一次完好的两个8×8矩阵的DCT改换(IDCT同理)。

2.1.2 Arnold置乱模块

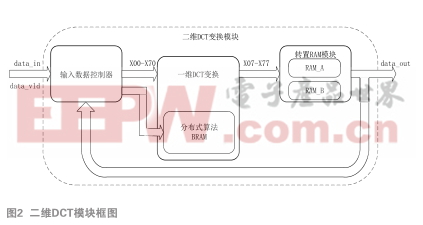

水印图画的置乱操作,简略来说便是将一切像素依照必定规矩完结从头排序,使得图画成为凌乱的不行辨认图画,然后躲藏水印信息,本质上便是对水印图画的加密 [5] 。置乱后的水印图画能够下降噪声或许进犯的影响,进步水印信息的鲁棒性和抗进犯性。本体系选用Arnold置乱对水印图画进行处理,通过FPGA将32位200×200的原始水印图画进行置乱。模块将水印信息原存储地址通过置乱后,得到Arnold存储器地址后将水印信息从头存入。

地址改换是将水印图画原地址(x,y)处的像素点移动至改换后的方位(x’,y’),其间方位改换公式为:x’ = (x + y) / 200,y’ = (x + 2y) / 200。

一起Arnold置乱具有周期性,通过仿真发现图画的置乱周期为150,即通过150次置乱后得到原图画,所以在水印嵌入模块进行N Arnold 次置乱后,在水印提取模块进行150-N Arnold 次置乱即可康复水印图画。

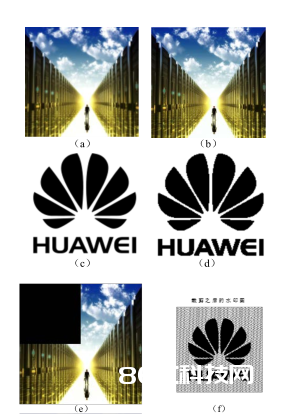

本体系的Arnold置乱模块运用上述公式,对水印图片的行/列地址进行置乱。首要将输入的水印图画信息按行的次序串行输入并进行N Arnold 次Arnold置乱,运用递减循环操作进行置乱地址的200减法求余运算,终究得到完结Arnold置乱的水印图画,图3的原始水印图画通过90次Arnold置乱后得到图4所示的置乱水印图画。

2.1.2 混沌序列模块

混沌现象非周期,不收敛,有界且对初值灵敏,对错线性动态体系中呈现的确认的相似随机进程,能够容易地生成许多非相关、类随机的确认再生信号。

映射是广泛运用于混沌体系中的一个非线性方程 [6] ,公式如下:其 中 x, μ 是 分 支 系 数 , 且3.5699456≤μ≤4时,Logistic映射作业于混沌状况,本体系挑选μ=3.875,初始值x 0 =0.621,在依据FPGA规划体系时,应尽或许防止小数操作,所以将μ右移3位得到U=31,初始值x 0 右移8位得到x 0 =159。输入初值进行Logistic映射时,依照x i+1 =U×X i (1-X i )运算,得到的值x i+1 左移11位即可得到0~1之间的混沌序列。

(1)嵌入规矩

本体系规划为盲水印算法,即在水印检测进程中时,只需求密钥而不需求原始数据的参加。在水印嵌入进程中,引进了混沌序列作为水印嵌入点挑选的条件。

因为混沌序列自身具有初值灵敏性特性(即初值不同发生的序列彻底不同),因而,引进混沌序列作为密钥将进一步进步算法的隐蔽性。

DCT 域8×8矩阵中的频域系数进行编号得到次序排列表,且表从左上角到右下角代表着从图画的低频部分到高频部分,如下表1所示。

依据 Waston 模型的频率灵敏度特性,一起考虑图画进行JPEG紧缩后图画质量不呈现显着下降,本体系挑选在中频系数挑选适宜的像素点,依据加法水印嵌入规矩将200×200的水印图画嵌入800×800的载体图画,即可划分为将4个水印图画信息嵌入8×8载体图画矩阵中,一起依据嵌入规矩在可选4个像素点中挑选嵌入1个水印信息,嵌入比为1/16,因而为了嵌入一切水印信息,需求在8×8的载体图画矩阵中挑选4组16个像素点。归纳考虑,本文挑选Zigzag 表中编号为19、20和 8、10 ,9、11和12、14 , 13、15和17、21 , 16、18和22、23这4组像素点进行水印图画嵌入。终究依据上述置乱后的水印信息W,混沌序列值为X,每组像素点的系数别离为F1,F2,F3,F4,终究挑选一个适宜的a值完结加法嵌入规矩得到终究的像素点F0:

假如 X = 1,W = 1:若 F4 < F3,则F0 = F3+a,不然F0 = F4+a;

假如 X = 1,W = 0:若 F4 > F3,则F0 = F3- a,不然F0 = F4 -a;

假如 X = 0,W = 1:若 F2 < F1,则F0 = F1+a,不然F0 = F2+a;

假如 X = 0,W = 0:若 F2 > F1,则F0 = F1- a,不然F0 = F2-a。

(2)体系运转成果

将800×800载体图画和200×200的水印图画转化成二值数据传入本体系,仿真成果如图5(a)(b)

(c)(d)所示,能够发现嵌入水印后的图画与载体图画并没有视觉上的失真,具有杰出的水印不行见性,一起在未受进犯时,水印图画具有很好的隐蔽性。

对嵌入水印后的载体图画别离进行1/4裁剪进犯,方差 0.01的高斯加噪进犯和马赛克进犯后提取水印信息来验证本体系的鲁棒性,进犯办法如图4(e)(g)(i)所示,成果如图4(f)(h)(j)

所示,能够发现通过三种水印进犯后,本体系依旧能够提取水印信息,且通过仿真知,反抗取舍进犯后的相关系数NC=0.7464,反抗高斯噪声后的相关系数NC=0.9998,反抗马赛克进犯后的相关系数。

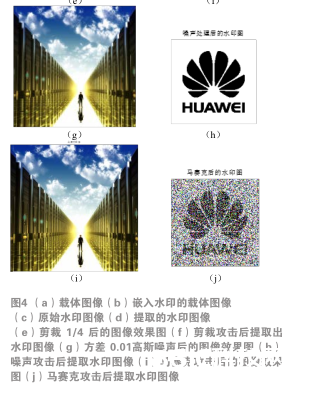

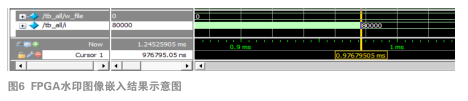

3.2 硬件速度与资源运用情况

通过仿真图5(a)能够发现,本体系在通过时序优化后,完结一次图片处理小于1 ms,可在频率下正常作业,并完结100 ms内完结100个水印图画嵌入操作。FPGA硬件运用资源如图5(b)所示,除IO接口外运用的资源缺乏FPGA开发板资源的1%。

4 定论

本体系在全国大学生集成电路立异创业大赛中,适用于参赛标题“华为云杯-图片水印完结”,终究取得西南分赛区一等奖,全国总决赛三等奖。本体系将持续在架构上对二维DCT改换模块进行优化,在确保功用的一起,下降FPGA的IO接口资源运用率。

参考文献:

[1] 李赵红, 侯建军. 依据Logistic混沌映射的DCT域软弱数字水印算法[J]. 电子学报, 2006,34(12):2134-2137.

[2] 于平平. 依据VLSI完结的数字图画水印技能研究[D]. 天津大学, 2010.

[3] 常晔. 依据DCT域的图画数字盲水印算法规划及硬件完结[D]. 天津大学,2010.

[4] 张钉铭. 依据FPGA的数字水印算法完结[D]. 南京航空航天大学, 2012.

[5] 倪蓉蓉, 阮秋琦. 运用Arnold对称性改换的图画信息躲藏算法[J]. 北京交通大学学报, 2002, 26(2):25-28.

[6] 刘昕浩, 郭腾, 谢德辉,等. 依据Logistic混沌映射的图画加密通讯体系研究[J].湖南理工学院学报(自科版), 2015, 28(4):27-31.

本文来源于科技期刊《电子产品世界》2019年第4期第76页,欢迎您写论文时引证,并注明出处