0 导言

边际检测是图画剖析进程中十分根底和重要的研讨范畴,边际提取的好坏将直接影响到后续处理的准确性和难易程度。用于边际检测的办法有Roberts,Sobel,Laplace,Canny,PreWitt等很多算法。在这些算法傍边,因为具有杰出的边际检测才能而使得Canny算法在数字图画处理中得到了广泛的运用。可是因为核算量的巨大,处理的时刻又比较长,往往很难满意体系的要求。因为FPGA对数据的并行处理,能抵达体系的实时性要求,且开发的周期短,选用电子规划的EDA技能使得开发、调试和验证更为直接和简略可行。

本文在FPGA根底上研讨Canny算法的边际检测,并对它进行了加快改善,且在数据处理进程中运用了流水线规划,更深化地发掘了FPGA在数据处理速度中的优势。仿真试验证明了该办法的可行性,而且完结了杰出的实时性。

1 Canny算子的边际检测

边际是指在其周围像素灰度有明显变化的那些像素的组合,它是具有幅值和方向的矢量,在图画中表现为灰度的骤变。早在1986年Canny就提出了边际检测应该满意的三个最优原则:

(1)重要的边际不能丢掉,没有虚伪的边际,而且差错检测率是最小的。

(2)实践边际与检测到的边际方位之间的变差最小。

(3)对单一边际应具有专一的呼应。

Canny算子首要运用高斯滤波器来滑润图画,再核算图画梯度的强度和方向,接着对梯度图画进行非极大值按捺,终究选用双阈值办法从候选边际点中检测和衔接边际。

1.1 Canny算子原理

Canny算子是把边际检测问题转换为函数极大值的问题加以处理。提取边际首要要进行高斯滤波,其意图是对原始图画进行滑润处理,以削弱或除掉图画中的噪声。其高斯滤波的根本思想是将一个对称的二维高斯函数与原始的图画做卷积运算,再沿其梯度方向做微分,这样就构成了一个简略且有用的方向算子。

f(x,y)为原始图画,G(x,y)是二维高斯函数,则滑润滤波后的图画I(x,y)为:

I(x,y)=G(x,y)*_f(x,y) (1)

界说方向n为边际方向的法向方向,则n可由下式得出:

式(3)阐明了怎么寻觅部分最大值,在非极大值按捺之后,还要经过阈值化处理来寻觅极大值。先设定一低阈值Th1,然后选取高阈值Th2≈2*Th1,将极大值按捺后的图画按Th1,Th2进行两次阈值化处理,得到图画T1和T2。因为图画T2是经过高阈值得到的,噪声和伪边际很少,但也造成了一些实在边际信息的丢掉;而图画T1保存的边际信息相对全面,可是存在一些虚伪的边际信息。所以以图画T2为根底,图画T1为弥补能够获得相对全面的边际图画。

1.2 算法的模板

本文算法中的高斯滤波器和梯度强度核算时都选用3×3的方形移动窗口,一起梯度强度核算选用Sobel算子。在对图画进行滑润处理时,需求运用高斯模板与原图画中的像素点值做矩阵的卷积运算。本文选取高斯模板的模板系数为0.062 5,且σ=1。模板如下所示:

式中:h为水平方向上的模板;v为笔直方向上的模板。h与图画做卷积得到水平方向上的梯度强度Ex;v与图画做卷积得到笔直方向上的梯度强度Ev。然后经过式(4)核算梯度强度Gr为:

Gr=|Ex|+|Ey| (4)

在FPGA中,卷积的运算是经过移位和加法来完结的。关于8位的图画来说,在移位和加法的运算中,因为存在正负号的运算,像素值的巨细会被调整为11位,在终究做完绝对值的加法运算后要把11位缩回8位并得到终究的像素导数值。

2 加快功用规划

本文对图画的快速处理选用了流水线技能。所谓流水线技能是把规划较大、层次较多的组合逻辑电路分为几个级,在每一级刺进寄存器组并暂存中心数据。关于每个进程只依赖于前面进程的运算成果的次序处理来说,流水线技能能大大地进步体系的功用。在本文的算法中,可将处理进程分为以下几个使命:图画滑润、梯度核算、非极大值按捺和图画边际断定检测。使命与使命之间都是次序履行的,即便是说下一使命的履行需求上级使命的成果输出数据,因而总的时刻花销为各个使命所需时刻的总和。要使体系运用的处理时刻最小,也便是使每个使命所花费的时刻最短。

2.1 加快器规划完结

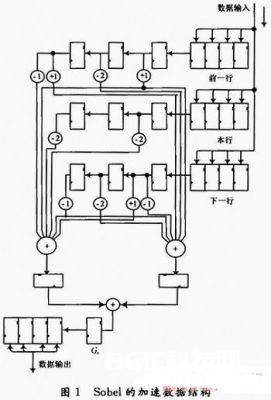

本文运用了一种能运用于高斯滑润滤波和梯度核算的加快器的数据途径结构。因为这两种核算进程均选用相同巨细的方形移动窗口,故其加快规划具有极大的类似性。对此,这儿选取3×3的Sobel模块来解说阐明。

Sobel的加快数据结构如图1所示。它是一个具有以下功用的流水线:先从原始的图画中读取像素值存入图中右方的3组12寄存器中,数据流过中心的3×3的乘法器阵列,即像素值与模板值做乘法运算;然后向下流过加法器,在加法器中完结和运算,至此完结了像素值与模板的卷积运算,之后抵达Ex和Ey寄存器,经过绝对值电路和加法器(完结式(4))抵达寄存器,终究流入最下面的寄存器。图中负号表明取反,数值1和2表明右移的位数。

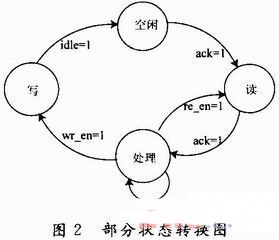

为使得加快器能够有序地依照确认的进程进行,本文运用了有限状况机。如图2所示为加快器的简略状况转换图。在加快器的履行进程中,当检测到3组寄存器中的数据为空时,读信号使能re_en置1,主动读入新的3组数据;且在下方寄存器存储满时,写信号使能wr_en置1,数据被提取进行写操作。

在加快器的履行进程中,像素每4个为一组进行读写,这样在高速处理进程中大大缩减了对相同像素点的屡次重复读取而糟蹋的时刻;一起,在处理进程中不需求在处理每个像素点时都对其邻域的8个像素点更新,这样节省了很多的读取时刻;而且因为FPGA的并行特性,像素的读、移位及写操作和乘法器的运算是一起进行的,使得处理速度有必定的进步。

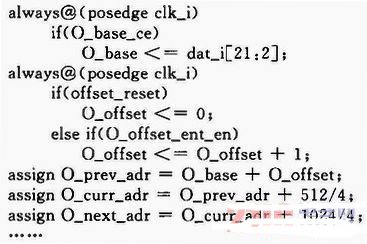

2.2 加快器的地址发生

在体系的接连处理进程傍边,加快器没有专门的等待时刻用来对数据进行读取和存储,这两类运算都是并行进行的。因而加快器需求具有主动选通的读/写地址电路。关于一幅512×512图画来说,从偏移值0开端计数,一次加1,以便于从内存中读一组4个像素值,把偏移地址和基地址加起来构成前一行的像素地址,把它加上512/4就构成当时行的读地址,再加上1 024/4就构成了下一行的读地址。关于写地址来说,从偏移值512/4开端计数,一次加1构成每次的写地址。地址发生器的部分代码如下:

3 Canny算法加快规划

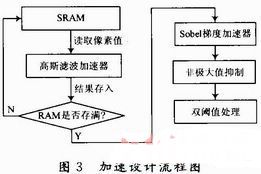

为了使得整个算法的核算速度得到进步,使算法既满意高速要求也不会消耗很多的硬件资源,本文对高斯滤波和梯度强度核算两个使命模块做了加快规划组合,流程图如图3所示。

高斯滤波器选用与Sobel加快器类似的规划原理,具有流水线的加快功用。图中RAM是FPGA中自带的Block RAM块,其巨细装备为仅存储当时被处理图画的三行像素值,关于512×512的8位图画来说RAM应装备为512×3×8 b。因为高斯滤波的存储和Sobel加快器在读取的时分都是每4个像素点即32 b数据来进行,所以装备为32位宽的一起读写操作的双口RAM。

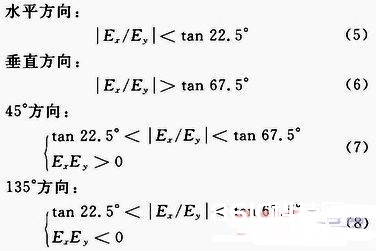

梯度运算之后,进行非极大值的按捺,在非极大值按捺之前需求核算梯度的方向。梯度方向的核算分为四个方向:水平、笔直、45°方向及135°方向,且每个方向上都包括两个45°的规模。经过Ex和Ey的比值及正负能够确认梯度方向落在上面规则的四个方向之一。判别四个方向的详细如下:

在FPGA中,直接做除法运算是很杂乱的进程;为了削减资源的开支,把式(5)~式(8)中的除法变换成乘法,再做比较来判别梯度的方向。关于tan 22.5°和tan 67.5°做如下处理:

非极大值的按捺在体系中经过挑选器和比较器来完结。依据输入的梯度值和梯度方向,用非极大值按捺条件(式(5)~(8))和凹凸阈值条件对输出的数据进行比较挑选,强边际点输出为255,弱边际点输出为0。因为硬件流水线的特色,鸿沟像素的核算成果是无效的,所以将鸿沟上的队伍都置为0。重复以上进程,直到整幅图画扫描完结,终究得出边际图画。

4 体系验证和成果剖析

为了能清楚直观地验证加快的加快效果,本文在体系渠道上对相同的图画分别用加快/未加快的体系做处理,记载相应时刻并比较。

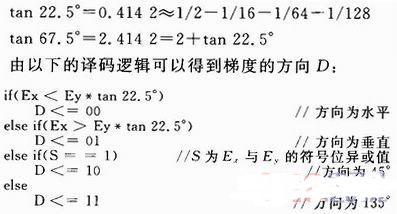

本文选用的验证体系渠道以Altera公司CycloneⅡ系列中的EP2C20F484C8芯片为中心建立而成,如图4所示。在验证体系规划中完结一个串口用来和PC机中的上位机通讯,把处理完后的数据经过串口传输给上位机。数据在串口的传输进程中的延迟时刻是固定的,故从上位机接收到第一个数据到终究一个数据的时刻差即为一帧图画处理所花费的时刻。

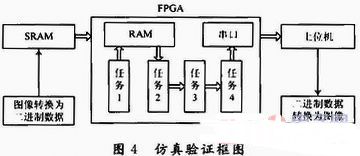

本文选取了不同巨细的3幅图片做试验验证,体系时钟频率为100 MHz。其处理时刻成果如表1所示,体系1为有加快功用的体系,体系2为未经加快的体系。

由表1可见,经过加快改善后的体系在处理时刻上得到了很大的节省,随图画尺度变大,总的节省时刻显然是添加的;且经核算知:当尺度变4倍(表1第2列256图与第3列512图),节省时刻大约添加3.9倍;640×480图比512×512图尺度大1.17倍,节省时刻是1.23倍,实践成果与理论核算相吻合。跟着图画尺度的添加,节省时刻亦按份额添加,因而该加快功用在处理大容量高速的图画时具有更大的优势和宽广的运用远景。

图5为一幅在FPGA中经过加快器体系处理后运用Matlab出现的边际图画。该算法处理的图画成果根本得到一切的边际信息,完全能满意运用需求。

5 定论

本文提出并完结了一种根据FPGA的加快Canny算法边际检测体系。该体系充分发挥和使用FPGA的优秀并行处理才能及流水线技能,然后完结功用加快。

在加快进程中经过状况机的操控效果能使模板的运算处理和数据的读/写操作得以一起进行,必定程度上节省了因很多的读/写数据操作而占用的时刻。此体系充分使用了FPGA中的硬件资源,大大进步了体系算法的运算功率,且规划结构较为灵敏。终究经过边际检测试验,验证了规划的正确性。