摘要:根据NI公司的智能FPGA板卡以及图形化编程软件LabVIEW规划并完结了一种通用数据收集体系。该体系与传统的数据收集体系比较结构简略、开发周期短、牢靠性高、实时性好,并且关于不同运用场合,在FPGA逻辑单元满意多的情况下能够很简洁地根据实际情况对其做相应调整,具有较强的通用性。

0 导言

数据收集是信号剖析和处理的重要环节,在导弹半什物仿真进程中快速牢靠的试验数据为进步仿真精度发挥着重要的效果。传统的数据收集体系各种数字、模仿信号相互交织,相应的外围电路巨大,接口杂乱,要占用较大的电路板空间,无法满意体系的小型化要求,一起硬件本钱也很高。当体系功用指标发生改动时,相应的功用电路和与之对应的阻隔、滤波等电路以及相关程序都要改动。这种牵一发而动全身的结构导致体系的可扩展性比较低,体系的通用性比较差。另一方面,前期数据收集体系多是根据杂乱可编程逻辑器材(CPLD)规划的,数据的采样速度和精度都不是很高。

跟着集成电路技能的开展,NI公司的FPGA板卡以其IO引脚多、片内资源丰厚、结构灵敏、具有嵌入式操控器的特色获得了越来越多的运用,其纳秒级的速度能够较大地进步数据采样的速度和精度。因此,根据NI公司FPGA板卡的数据收集体系和传统的数据收集体系比较更能实时、快速地监测信号量的改动。并且该体系结构简略、开发周期短、牢靠性高、实时性好,能够完结导弹半什物仿真的数据收集使命,具有较强的通用性。

1 体系计划规划

规划该数据收集体系的首要意图是在导弹半什物仿真体系中收集导弹的舵信号,将其传给上位机进行运算和仿真。该体系的可扩展性比较好,能够灵敏地习惯不同的运用场合,具有较强的通用性。

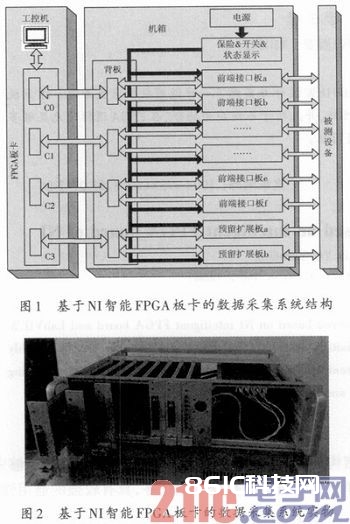

体系结构图如图1所示,体系什物图如图2所示,将具有数据收集功用和数据通讯功用的前端接口电路板卡集成在一个机箱里边,衔接在同一块背板上由独立电源共同供电。背板上的四个接口通过NI公司专用数据线和安装在工控机里边的FPGA板卡相衔接。通过FPGA板卡与LabV IEW图形化编程开发渠道,完结工控机与半什物硬件体系之间的数据收集和操控信号的传输。NI公司FPGA板卡的I/O端口从C0~C3共分为四个接口,每个接口40个端口。通过LabVIEW渠道进行设置能够便利地自由支配、界说任何一个端口的read/write功用,很好地处理了高速数据收集体系的操控问题。也能够由FPGA板卡向前端接口电路供给共同的时钟信号和指令字,使不同功用的电路板卡同步进行数据操作。

由码盘、旋转变压器/自整角机等传感器测量到的舵偏角信息输入体系之后,依照相应的功用需求接入不同的前端接口板卡进行光耦阻隔或许通过滤波、扩大等处理,经由机箱背板电路抵达FPGA端口。通过FPGA剖析和处理的信号之后再被传入上位机中进行存储、剖析、核算、显现等处理。

在FPGA的逻辑单元满意的情况下,关于不同的运用场合能够很简洁地通过增删不同功用的前端接口电路板完结相应的运用要求,然后不会对体系的其他部分发生影响。因此,该体系的可扩展性比较好,能够灵敏地习惯不同的运用场合,具有较强的通用性。

2 硬件规划

曾经端接口板a的完结为例,其首要构成为16位的D/A转化器DAC7731模块、14位A/D转化器TLC3574模块及其他辅佐电路。

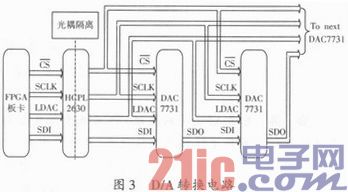

2.1 D/A转化电路

DAC7731为16位的数字模仿转化芯片,其内部供给+10 V的参阅电压。将其模仿量输出通过引脚设置为-10~+10 V的电压规模。DAC7731具有带双缓冲的规范三线SPI串行接口,答应模仿输出的异步更新。如图3所示,它还有一个串行数据输出线以完结多片DAC7731的链接。体系作业时由LabVIEW图形化编程开发渠道通过FPGA生成和发送DAC7731芯片的SPI接口和时序操控信号,通过SDI信号顺次将需求转化的数据以从最终一片到榜首片的次序发送给每片DAC7731,之后通过

和LADC信号完结多片DAC7731的同步转化输出。

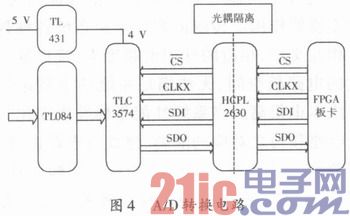

2.2 A/D转化电路

归纳考虑体系的分辨率、通道数、采样率、采样规模和接口等要求,体系的ADC选用TI公司的14位8通道高功用逐次迫临型模数转化器TLC3574。该器材作业频率高达25 MHz,选用伪差分的模仿输入电路,将采样信号的动态规模扩展为±10V,其内含的采样和坚持功用使得外围电路大为简化。在输出接口上,该器材选用SPI/DSP兼容的串行接口方法,然后极大地减少了接口的连线数量。A/D转化电路原理如图4所示,由FPGA生成TLC3574的SPI接口和时序信号,操控其将外部的模仿信号转化后输入到FPGA,进行相应的核算和处理。由于TLC3574片内没有电压基准,可选用TI公司的三端可凋分流基准源TL431组成外围电路为其供给一个高精度的4 V电压基准。

考虑到信号的阻抗匹配需求,ADC的输入前端需求有一个缓冲运放,其功用有必要与ADC的功用相匹配,不然会影响和约束ADC的功用。在数据收集进程中假如信号的改动起伏比较大,则需求根据信号的改动相应调整扩大器的增益。不然,单一的增益扩大会使得扩大后的信号幅值很有或许超越ADC的转化量程。这儿所收集的信号其改动起伏不是很大,选用TI公司高转化率的输入端运算扩大器TL084就能够满意体系的运用要求。

2.3 数字量输入/输出规划

直接将通用背板的FPGA端口引到前端接口板,根据测验目标的接口电路,如27 V/开、地/开等方法,挑选继电器、OC门、光耦阻隔等方法,完结数字量的输入和输出。

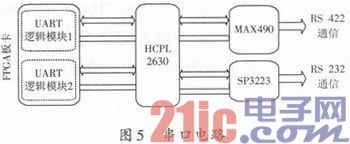

2.4 串口电路规划

由于FPGA板卡具有便当的输入输出操控功用,运用FPGA板卡能够很便利的通过衔接不同的接口芯片挑选相应的串口形式。MAX490是低功耗收发器,用于RS 485与RS 422通讯。它具有一个驱动器和一个接纳器,驱动器摆率不受约束,能够完结最高2.5 Mb/s的传输速率。驱动器具有短路电流约束,并能够通过热关断电路将驱动器输出置为高阻状况,避免过度的功率损耗。接纳器输入具有失效维护特性,当输入开路时,能够保证逻辑高电平输出。如图5所示,通过衔接低功耗收发器MAX490能够完结RS 422通讯,而改接SP3223芯片后就能够完结RS 232通讯,差异仅仅在于FPGA中树立的UART逻辑模块有所不同,进一步显现了体系杰出的通用性。

2.5 电气阻隔规划

由于该体系为模仿/数字混合信号体系,电路中的噪声会对数模和模数转化精度形成影响,因此在电路的完结上应该对板卡芯片进行降噪和阻隔维护,这样既避免了不同信号之间的相互影响,进步了体系的共模按捺才能,也使得一些比较贵重的芯片不会由于外部信号的不稳定而焚毁。

传统的阻隔方法是对每个通道都运用%&&&&&%耦合模仿阻隔芯片ISO124等进行阻隔。这类阻隔方法其输入和输出别离由两组直流电源供电,并且存在较大的漂移,输出信号一般存在纹波,特别当信号比较小时,输出的相对误差会增大。因此,还需求对输出信号进行滤波、调零等调度办法,使得体系电路比较杂乱。

光电耦合器功用优胜,具有杰出的抗干扰才能,因此被广泛地运用于输入和输出信号的电气阻隔。运用HCPL2630等高速光耦进行光耦阻隔,只需求一组直流供电电源,电路非常简略。其杰出的电绝缘才能和抗干扰才能使得模仿地和数字地分隔,消除了共模电压影响。体系选用串行而非并行的ADC和DAC,只需求阻隔三路的SPI总线数字信号,这样进一步简化了电路规划。

3 软件规划

3.1 FPGA逻辑

FPGA智能板卡是整个数据收集体系的中心,由其发生和发送DAC与ADC的SPI接口和作业时序。其内部的逻辑单元首要包含:DAC操控器、ADC操控器、接口单元等。DAC和ADC操控器是FPGA内部的首要履行单元,它依照DAC和ADC作业时序进行相应的作业。

DAC操控器:关于发送进程,在树立周期,DAC操控器初始化操控信号CS(置“1”);在指令周期,使能CS信号(置“0”),一起依照时钟节拍,将16 b指令字以串行方法发送至DAC;在采样周期,对CS信号进行坚持;转化周期,置位CS信号(置“1”);关于接纳进程,在树立周期LDAC处于确定状况(置“1”);在接纳周期,以串行方法接纳前次转化的16 b数据;在存储周期,操控器将LADC置“0”,改动寄存器内容;在闲暇周期,复位LADC(置“1”)康复寄存器的确定状况。

ADC操控器:关于发送进程,在树立周期,ADC操控器初始化操控信号CS(置“1”);在指令周期,使能CS信号(置“0”),一起依照时钟节拍,将16 b指令字以串行方法发送至ADC;在采样周期,对CS信号进行坚持;在转化周期,置位CS信号(置“1”),并载入下一通道的指令字,一起,核算下一次接纳数据的存储地址。关于接纳进程,在树立周期,操控器清零各接纳寄存器,一起复位内部RAM的写信号WR(置“0”);在接纳周期,操控器依照时钟节拍,接纳ADC上一次转化的14 b串行数据;在存储周期,操控器使能WR信号(置“1”),并将接纳到的数据写入ADC通道对应的RAM单元;在闲暇周期,操控器复位WR信号(置“0”)。

3.2 LabVIEW程序规划

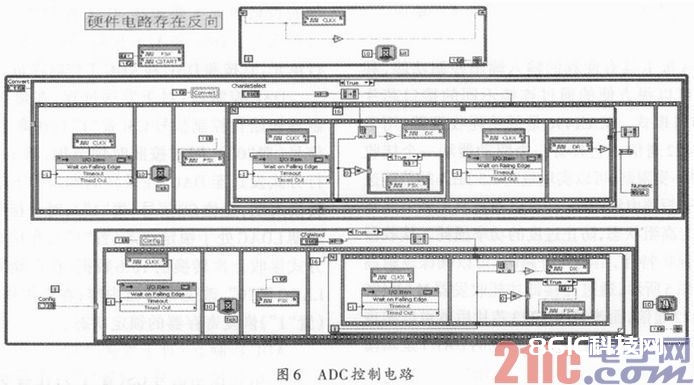

根据FPGA内部的逻辑单元结构和功用,通过NI公司的LabVIEW图形化编程开发渠道对上述逻辑进行了规划,并进行了功用仿真。给出ADC操控器LabVIEW程序完结,如图6所示。

NI公司的LabVIEW图形化编程开发渠道具有一系列的长处,它不同于VHDL等根据时序的言语,而是一种根据信号流向的言语,程序工作进程和实在硬件电路工作原理类似,用LabVIEW编程的进程就像规划电路图相同。别的它有不需求预先编译就存在语法查看和调试进程运用的数字探针,其丰厚的函数、数值剖析、信号处理和设备驱动等功用,都是非常优胜的。LabVIEW将广泛的数据收集、剖析与显现功用会集在了同一个环境中,能够在自己的渠道上无缝地集成一套完好的运用计划。

将由LabVIEW图形化编程开发渠道通过FPGA生成的正弦信号经D/A电路输出,通过A/D电路进行收集。别离选定四路不同的D/A通道和A/D通道进行输出和输入显现,图形共同,程序工作正常,波形显现明晰。限于DAC和ADC转化速度,收集到的波形存在着细小的相位推迟。如图7所示。

4 结语

根据NI公司FPGA板卡规划和完结的通用数据收集体系原理简略,易于完结。该体系牢靠性、实时性、快速性比较好,使得数据处理才能得到了极大的进步,可彻底担任大容量、高精度数据的高速收集。关于收集到的信号能够进行实时处理或保存,也可通过串行口将其送至上位机进行后续剖析处理。关于不同运用场合,在FPGA的逻辑单元满意的情况下能够很简洁地根据实际情况对其做相应调整,具有较强的通用性,实用价值比较高。