跟着一种新产品——咱们在Missing Link Electronics公司称之为“智能产品”的面市,嵌入式体系的开展呈现了新动向。这一名词源自最近新呈现的一个词“智能电话”,用于描绘具有智能电话特性的嵌入式体系:丰厚的交互式用户接口,可以经过各种传感器来感知环境,以及很强的本地处理才能等。

在智能产品中,这些功用集成到机械或许电子机械体系操控中:咱们可以称之为方针体系。其运用实例包含家电、车辆以及机器人等。在智能电话呈现之前,人们很早便开端了这类集成功用的研讨。1

跟着网路向泛在链接的开展,智能产品这一概念愈加丰厚了。现在,许多商场都要求新产品至少具有一种网络接口,用于接纳指令,陈述状况。逐渐的,新产品将参加“物联网”:设备之间经过点对点网络共享核算资源,进行操控,传递状况信息,还可以在云中经过深度核算和存储资源进行交互。现在对这类体系的规划和行为进行了深入研讨。2

在本文中,咱们的爱好不是剖析这类智能产品,而是怎样处理这类产品中许多的不匹配问题:不匹配的产品生命周期问题。一方面,问题在于,电子/机械方针体系开展缓慢,在某些情况下,数十年不会发生改变。而另一方面,智能产品的智能链接功用却在以网络速度发生着改变;新的躲藏用户接口、新传感器,乃至是新的操控算法等。这种改变的不合拍对体系的智能部分和方针部分之间的接口带来了很大的压力。

当然,可以经过软件来处理这一问题。可以在规范CPU内核上运转代码来完成智能产品的功用,并且还可以进行修正。可是,对物理接口触摸越深——智能体系和方针体系之间,或许智能体系及其传感器和网络之间,那么,就会知道硬件的效果会越来越大。在这些接口邻近,以及数字和模仿传感器感应器的实践链接中,一般需求硬件来加快对时刻要求较高的互操作。

这一问题的数字部分已经有FPGA运用。这些器材的最早运用是在数字接口中。现在,引脚数许多的大容量FPGA支撑完成完好的智能体系。这样,规划的一切数字部分,从接口到加快器和CPU内核,可以在现场针对用户接口和网络环境的改变进行重新装备。

可是模仿电路呢?无法装备智能体系和方针体系之间接口上的模仿信号通路,或许无法在智能体系自身添加传感器等,这些都极大的约束了智能产品的灵活性,及其产品生命周期。例如,在热传感器中,一种新运用怎样运用模仿信号——而接口现在还不能供给这类信号?在现场修正,添加模数转化器(ADC)和信号调度电路不太可行。

对此,人们不太留意的FPGA特性就显得十分重要了。高档FPGA的可装备I/O引脚支撑LVTTL——十分适用于咱们的意图,以及LVDS I/O,可以高达数百兆(MHz)。这一现实十分显着,由于LVDS输入实践上是功用杰出的高速电压比较器的外在输入。原理上,这一比较器可以用于构建delta-sigma调制器(DSM):即,过采样ADC。

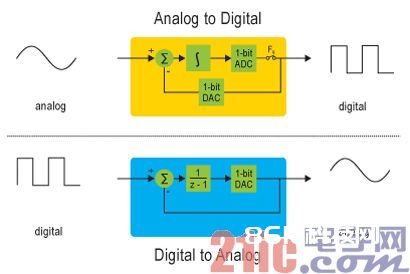

DSM是多种信号现在最好的数据转化办法,并且精度比较高。当然,其结构也可以用于树立数模转化器(DAC)。图1上部显现了一阶DSM的根本组成。这一版别选用了积分电路——“智能部分”,对差值进行求和——输入信号和反应信号之间的“delta”部分。1比特ADC仅仅比较器,1比特DAC是脉冲宽度调制数字输出。当积分电路输出高于参阅电压时,采样电路接通DAC,逐渐驱动积分电路后向输出。采样电路输出的脉冲列是模仿输入的数字表征。

图1.DSM技能可以一起完成模数转化器和数模转化器。

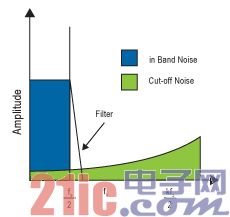

这涉及到一些要害点。在实践中,DSM会运用远远高于Nyquist频率的采样率,而这是传统闪存ADC采样所运用的频率;即,过采样。并且,DSM在反应网络中选用了滤波器,进行噪声整形。这些相结合,过采样扩展了采样噪声功率谱,噪声整形功用将噪声移出了信号带宽,如图2所示。这些理念相结合,仅运用FPGA的可装备I/O引脚以及少数的外部无源器材就可以构建十分好的ADC和DAC。

图2.过采样和噪声整形功用可以将大部分采样噪声从信号带宽中去掉。

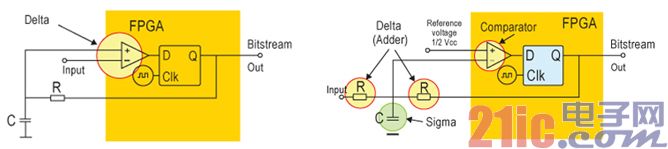

可是,完成起来并不是那么简略。图3左边显现了衔接输入的一个简略办法。可是,有一些名为delta调制器的源,不是DSM,它们不进行噪声整形。比照图中右侧的真DSM,FPGA的LVDS引脚高效的完成了1比特比较器,而选用了无源RC低通网络完成了环回滤波器。成果是具有噪声整形功用的真DSM。

图3.delta调制器(左边)与DSM (右侧)有彻底不同的噪声特性。

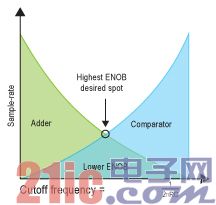

很显然,在模仿规划中,不能疏忽FPGA LVDS引脚的模仿行为。相应的,有限振幅判定时刻、亚稳态以及其他要素等都极大的影响了转化的信噪比(SNR)。如图4所示,从原理上画出了这些非线性效应,非线性加法器(例如,两个外部电阻)和LVDS比较器的反效果供给了较窄的“最佳点”,在这一点可以完成最佳SNR,即,最大有用比特数(ENOB)。

图4.无源网络和比较器特性相结合,确认了转化器规划的最佳点。

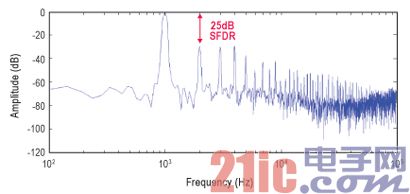

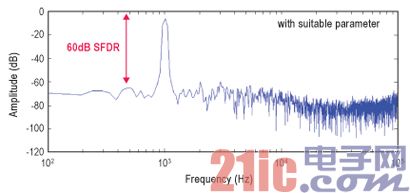

整个ADC/DAC电路的SPICE级仿真,包含FPGA LVDS引脚的SP%&&&&&%E具体表征,实践是找到图4中最佳点的最好办法,即,关于某一采样频率和输入电压,装备DSM的最优参数。假如没有适宜的参数,DSM会不稳定,呈现所谓的约束周期,劣化转化的质量。图5中的两条傅里叶曲线显现了同一DSM电路未优化和优化后组件之间的无杂散动态规模(SFDR)的差异。

图5.优化会在SFDR上发生很大的不同。

从这一优化电路的曲线上您可以看出,咱们在这里并没有评论低速、低分辨率的转化器。这一办法可以用于为体系监控等运用中的不要害慢变信号供给低本钱转化器。而这些DSM也适用于使命要害信号的信号通路。Missing Link Electronics公司开发人员社区:www.missinglinkelectronics.com/devzone/的技能摘要上供给这些“软ADC”和“软DAC”质量的具体信息。

可是,恰当的优化输入网络以进步这些根据LVDS的DSM的功用,并不是简略的作业。这需求很好的模仿规划技能,正确的运用FPGA引脚的电信号特性信息。换言之,这一般是专业知识产权(IP)供货商的作业。

为了可以选用这一ADC/DAC办法完成可装备体系,咱们引荐图6中的可装备模仿I/O体系结构。它在可装备ADC/DAC中结合了ADC单元和DAC单元,在转化器和先进的数字信号处理(DSP)之间设置了转化滤波器。在咱们的实验中,咱们发现,在大多数情况下,与其他需求许多资源的滤波器比较,轻量级抽取滤波器可以发生优异的SNR成果。

图6.完成这些DSM最有用的办法是选用第三方IP内核。

这意味着,智能体系中的模仿I/O数量首要受限于意图体系所运用的FPGA引脚的数量。规划将其他名贵的FPGA资源——逻辑单元和片内存储器,大部分留给了开发您的专用数字硬件。

运用根据FPGA I/O引脚的DSM,嵌入式体系的一切要害部分都是“软完成”——软件或许软核CPU的FPGA装备代码;加快器、信号处理流水线或许外设的软核IP;软核ADC和DAC等。因而,智能产品规划人员可以更好的操控嵌入式体系的资料本钱,少选用微操控器,找到并更新兼容的FPGA器材。

简历

Endric Schubert博士是电子体系规划、EDA和半导体方面的技能专家。他是Missing Link Electronics有限公司的创始人之一,这一嵌入式体系公司首要事务是可装备体系规划渠道。他从前从事过软件工程、FPGA技能、可装备核算以及嵌入式体系规划等。Endric获得了德国Karlsruhe大学的电子工程学位,获得了德国Tübingen大学的核算机科学博士学位。他出书了多篇技能论文,发明晰多项专利。

Christian Grumbein是Missing Link Electronics公司的规划工程师,擅长于微操控器规划和电源规划。他获得了德国Ulm大学的电子工程学位。

Missing Link Electronics (MLE)是一家新式公司,开发并出售嵌入式开发渠道。结合Open Source GNU/Linux,以及Android和可编程商用元器材,嵌入式开发人员可以敏捷完成他们的体系。MLE总部坐落硅谷,办事处设在德国。