张二丽(电子科技大学,四川 成都 610054)

摘 要:从1889年Nikola Tesla发明晰闻名的Tesla线圈开端,对无线充电技能的研讨受到了广阔规划者的注重[1],华为2018年发布的无线充电技能,其最大功率可达15 W,标志着无线充电年代的降临。可是由于芯片集成度的进步,SOC的功率密度越来越大[2],低功耗规划成为无线充电技能中应该重视的问题。针对Qi wirelesspower transfer version 1.1.2,选用格雷码的编码方法,二级门控时钟,多阈值电压以及低功耗计数器等功耗优化技能,使得该协议中主操控器的功耗下降了30%。

关键词:无线充电;数字电路;低功耗

0 导言

在传统无线传感网络中,一般运用蓄电池充电,需求不断替换电池,在限制了无线传感网络实践布置与广泛使用的一起大大进步了网络的保护本钱[3]。而早在1988年,约翰.鲍尔斯在实验室榜首次成功用无线充电技能点亮了1米外的60 W的灯泡,无线充电技能的可行性得到证明[4],至此无线充电技能的研讨越来越受到注重。

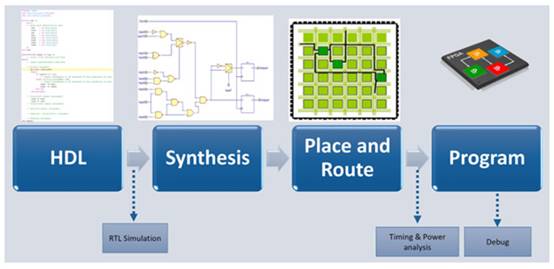

为了规范无线充电技能,WPC联盟提出的QI协议,该协议选用定频调占空比的架构运用操控器不断地对电路进行监控,通过调整线圈上的电压进行无线传输能量,与用蓄电池比较,其本钱大大下降,可是伴随着摩尔定律的盛行,每一代半导体工艺技能的进步,芯片密度的增大[5],关于规划者来说功耗就成为了必要的重视问题,电压巨细,dual-Vth和栅极尺度都与低功耗技能密切相关[6]。本文首要是对在RTL级电路规划的基础上进行低功耗规划。

1 数字电路功耗的构成

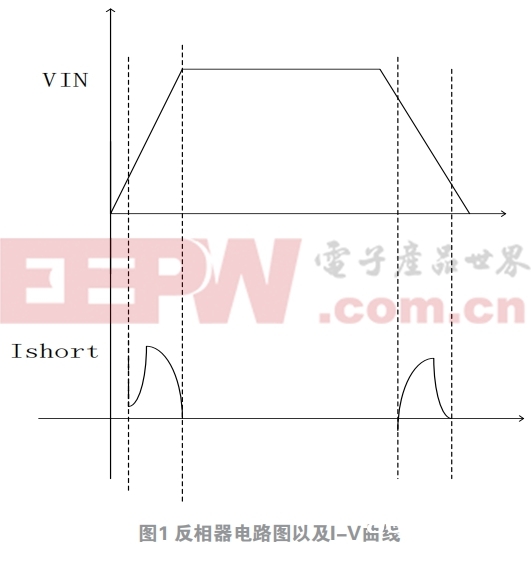

电路中的功耗分为两类:静态功耗和动态功耗。静态功耗首要是待机时的功耗,首要由走漏电流组成,一方面是由于MOS管阈值电压的存在,使得器材在关断状况下,具有亚阈值特性,因此会发生亚阈值电流[7]。动态功耗首要是由于短路电流和负载电容充电引起的。而在这两部分中有三种最首要的功耗耗费:对电容进行充放电的跳变功耗,在电路回转进程中发生的短路电流功耗和MOS器材的漏电流损耗[8]。其原理如下:当输入电平为低时,PMOS管会对输出节点上的电容进行充电,当输入电平为高电平时,NMOS会对电容进行放电,然后到达反相器的作用,在这一进程中构成了MOS管的动态功耗,如下图1所示。

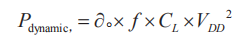

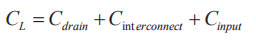

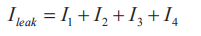

在输入信号的上升或下降的进程中,假如输入电平在 VTHN 与 VTHP+V DD 之间时,此刻NMOS与PMOS管一起导通,会呈现短路功耗。漏电流功耗是由MOS器材的各种走漏电流引起的损耗。其相应的公式如下:

其间 ∂ 是跳变系数, f 是输入跳变频率, VDD 是电源电压,

即MOS管本身电容,互连线之间的电容以及后级负载电容。

其间K为介电常数, τ为电平信号转化时刻, VTH 代表阈值电压,f代表时钟频率。可见阈值电压越高,短路功耗越低.

是走漏电流

PN结反向电流I4(PN-junction Reverse Current)

源极和漏极之间的亚阈值漏电流I2(Sub-thresholdCurrent)

栅极漏电流,包含栅极和漏极之间的感应漏电流I3(Gate Induced Drain Leakage)

栅极和衬底之间的地道漏电流I1(Gate Tunneling)

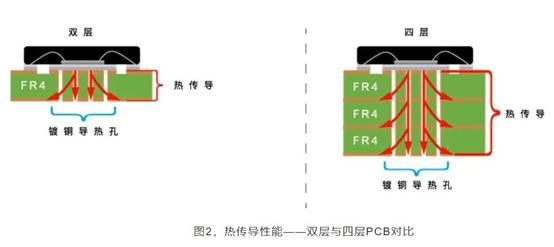

静态功耗首要于工艺有关。由于无线充电是数模混合电路,故对操控器的规划要考虑模仿方面的需求,选用的是0.25 μm ,5 V的规范CMOS数模混合库。

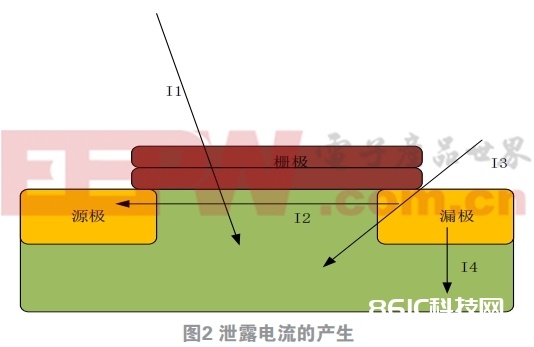

2 无线充电规划的整体架构

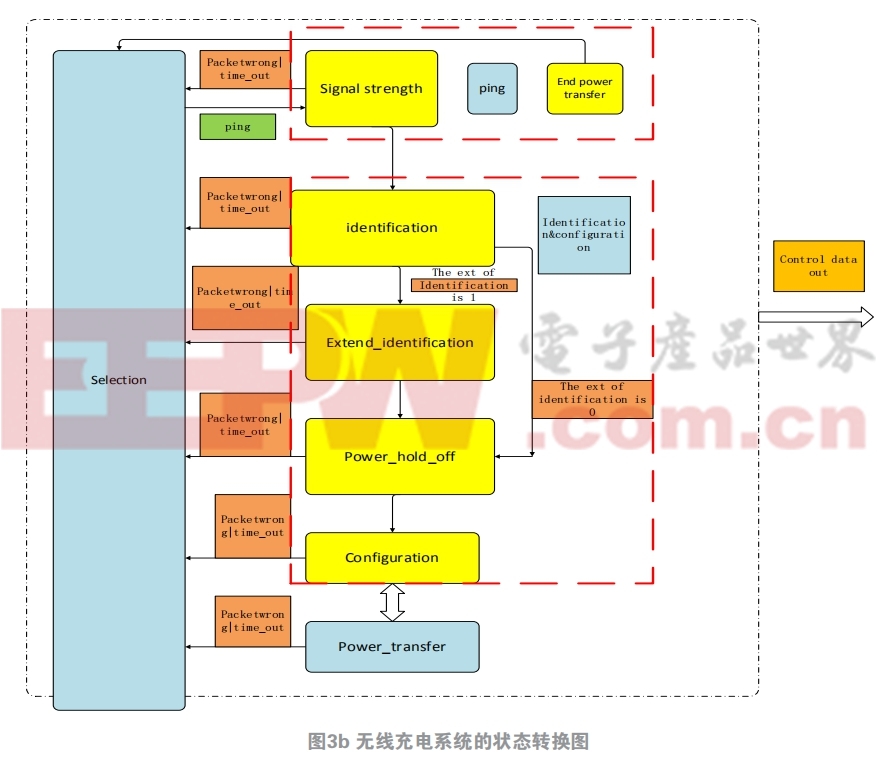

依据无线充电QI协议中操控器的规划要求,其操控器的规划架构如下图3a所示。该架构首要有:状况机,计数器,选择器和移位寄存器构成。状况机的规划如下所示,首要担任计数器的发动,在不同的状况下接纳相应的数据包,并进行CRC的比对,但在协议中运用的状况只要ping,selection,identication,powertransfer[9],在这四个状况下由于在identification状况下需求操控的信号较多,为防止瞬时功耗太高,将此状况依据数据包的不同进行了如下图所示的区分。计数器:由于操控器需求不断监控电路以及接纳方的充电状况,所以需求不断接纳数据包,不同的数据包的data位宽是不一样的,故需求计数器对发送来的数据位进行计数,一起不同的数据包之间有必定的时序要求,当超越必定的时刻时未接纳到相应的数据包,则电路进行断电处理。移位寄存器用来存储接纳方发送过来的辨认装备数据包以及当时充电的状况和电量的多少等,并将接纳到的串行信号改变为并行信号。

3 低功耗规划技能

3.1 选用二级门控时钟电路操控功耗

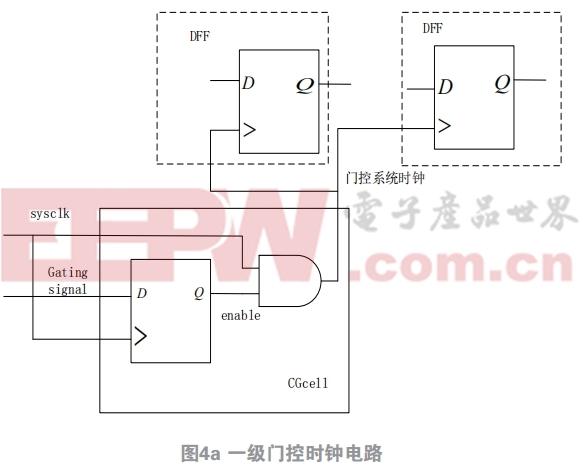

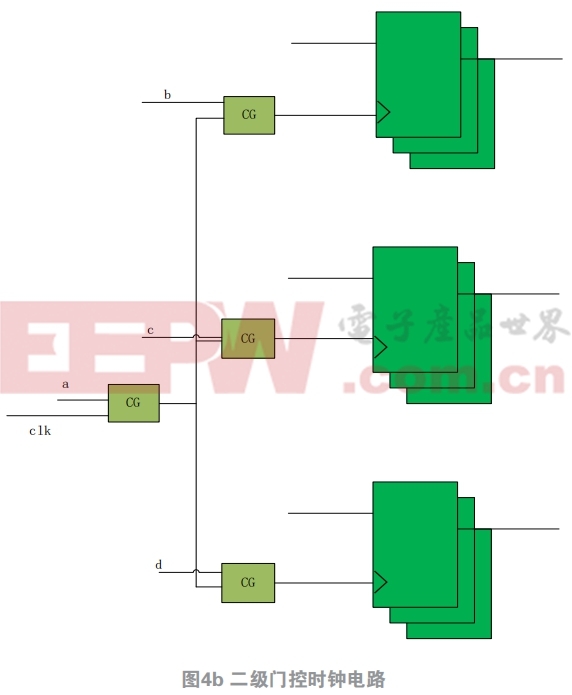

时钟信号是整个电路规划中回转率最高的信号,由此而带来的动态功耗是相当大。可是在单个时钟周期中,需求作业的模块并不是许多,故在规划中运用RTL特有的编码方法,在归纳的进程中参加相应的指令,就能够选用门控时钟的规划方法来下降功耗,可是一般状况下选用一级门控时钟操控,可是由于无线充电关于功耗的要求,在这里选用二级门控时钟,其相应的电路图如下所示,从图4a与图4b中能够看出,与一级门控时钟比较,二级门控时钟削减了三个与门而多了一个CGcell,且它能在削减体系面积的一起也下降了组合逻辑电路的功耗和第二级CGcell的功耗。门控基本原理便是通过封闭芯片上暂时用不到的功用和它的时钟,然后完成节约电流耗费的意图[10]。

3.2 分段式的移位寄存器

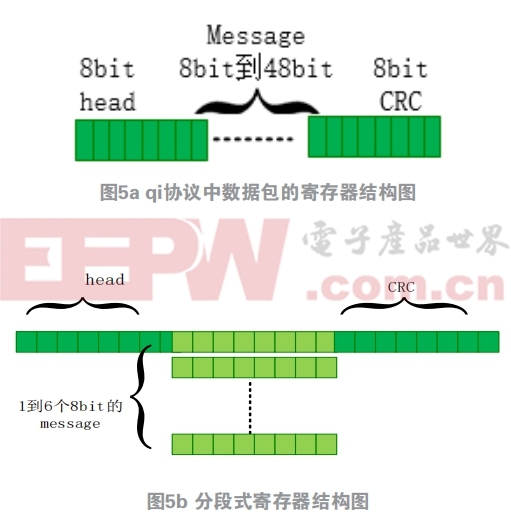

关于QI协议的操控器,需求接纳许多数据包,其间数据包的结构如下图5a所示,在规划中为了下降移位寄存器的翻转率,咱们将移位寄存器依照8bit一组进行了区分,如下图5b所示,很明显在存储数据的时分只对当时的8bit寄存器翻转。

3.3 计数器的规划

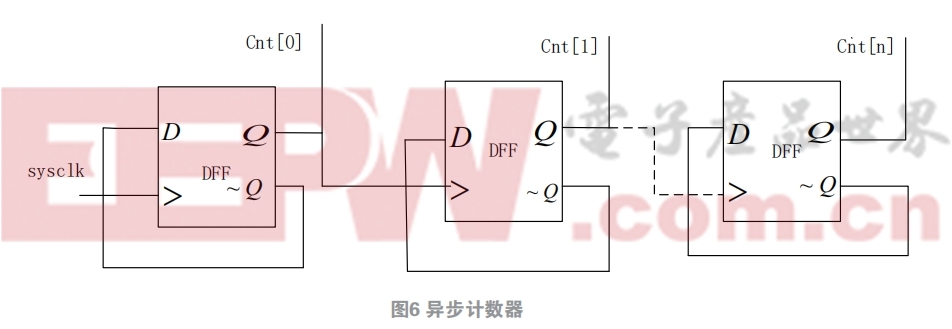

在接纳数据包的进程中,需求不断地监控时刻,所以就要用到计数器,在一般地规划中,用的是同步计数器,计数器首要是由触发器构成,在同一时钟下,一切触发器是一起翻转的,所以添加不必要的功耗,选用Jk触发器构成的异步计数器,在每次计数时只要榜首级触发器衔接高电平,第二级触发器由榜首级的输出端的下降沿驱动,第三级触发器由第二级的输出端的下降沿驱动,以此进行,来下降功耗,如下图6所示

3.4 状况机的编码方法

一般来说状况的改变是依照流程一步步走下来即可,可是在跳变的进程中会由于编码的方法而形成功耗多少的不同,一般来说,在规划时,尽量选用格雷编码方法,相邻状况之间只要一位数据发生变化,然后下降了功耗。

4 功耗剖析成果

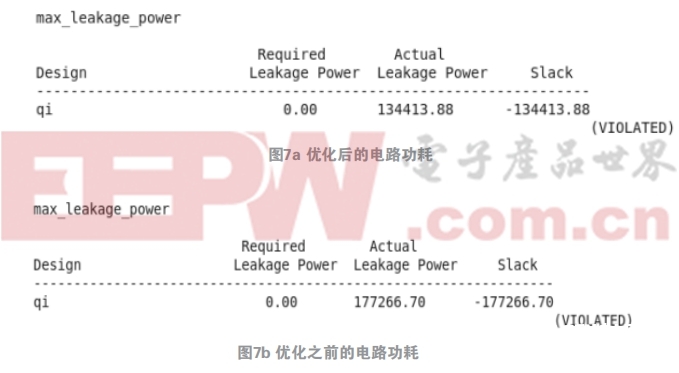

无线充电规划是一种数模混合的电路,故本次运用CSMC 0.25 μm 5 V enhance BCDMOS的规范单元的库,其通过功耗优化之后成果如下图7a所示。

与下图7b中未进行功耗优化的电路比较,能够发现其功耗大幅度下降,功耗优化率到达了30%。

参考文献

[1] B. Dennington, "Low Power Design from TechnologyChallenge to Great Products," ISLPED’06 Proceedings of the2006 International Symposium on Low Power Electronics andDesign, Tegernsee, 2006:213-213.

[2] R. Koster, S. H. Prasad and S. Ramachandra, "Failing tofail – achieving success in advanced low power design usingUPF," 2014 IEEE/ACM International Symposium on Low PowerElectronics and Design (ISLPED), La Jolla, CA, 2014:137-138.

[3] 王介阳. 根据Qi无线充电协议的气压传感器电路规划[D].广州:广东工业大学,2017.

[4] 王光宇.浅析无线充电技能的首要分类及使用现状[J].我国新通讯,2018,20(18):99-100.

[5] B. Dennington, "Low Power Design from TechnologyChallenge to Great Products," ISLPED’06 Proceedings of the2006 International Symposium on Low Power Electronics andDesign, Tegernsee:213-213.

[6] S. Bhunia and K. Roy, "Low power design under parametervariations," Proceeding of the 13th international symposium onLow power electronics and design (ISLPED ‘08), Bangalore,2008:137-138.

[7] 雷臻. 根据国家自主规范的RFID芯片数字基带的低功耗规划与完成[D].西安:西安电子科技大学,2017.

[8] JANRABAEY. LowPower Design Essentials[M]. USA:Springer, 2009.

[9] WPC.QI System Description Wireless PowerTransfer [S], 2013.

[10] 汪国平.数字集成电路门控时钟可靠性研讨[J].科学技能创新,2018(07):19-20.

本文来源于科技期刊《电子产品世界》2020年第02期第66页,欢迎您写论文时引证,并注明出处。