本体系是以STM32F407为中心,首要选用FIFO来做高速缓存。高速信号先经过AD采样,然后先将采样后的数据给FIFO先缓存处理,然后再经过STM32F407进行加Blackman预处理,再做1024个点FFT进行频谱剖析,最终将数据显现在LCD12864上,以便进行人机交互!该体系可完结恣意波形信号的频谱显现,以及能够主动寻觅各谐波重量的幅值,频率以及相位并进行8位有用数据显现。

体系规划使命

一、使命

规划并制造一个高速频谱剖析仪。

1体系计划

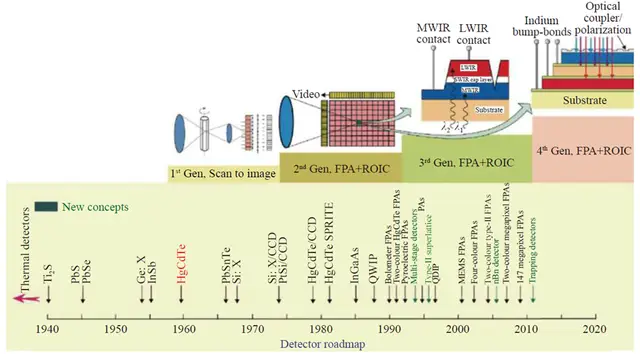

本体系由前置匹配扩大电路,AD采样电路,高速FIFO缓存电路,以及液晶显现电路组成。其间高速数据缓存电路,以及高精度的显现数据是本次规划的难点!下面别离证明这几个模块的挑选。

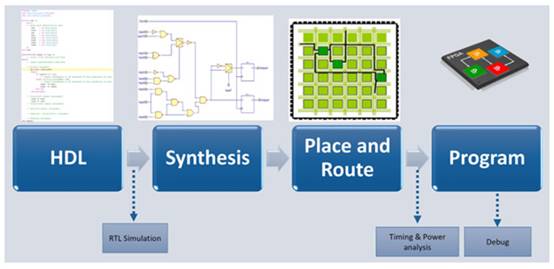

体系框图

1.1丈量办法的证明与挑选

1.1.1 MCU处理器的比较与挑选

做DSP处理首要是要考虑到运算速度。

在处理器的挑选上一般能够选用8位,16位或许32位的MCU,但由于在处理信号的过程中,一般会遇到快速傅里叶FFT算法,所以会遇到很多的浮点运算,并且一个浮点数要占用四个字节,故在处理过程中要占用很多的内存,一起浮点运算速度比较慢,所以选用一般的MCU在必定时刻内难以完结,所以归纳考虑运算速度和内存大小等要素。

本体系选用32位的STM32F407做为中心DSP处理器材,该芯片具有1MB的Flash闪存空间,196KB的SRAM空间,并且时钟频率到达了168MHz。程序运转于168MHz主频时,经过Flash取指令(不是内部SRAM),经过Dhrysone测验得到210DMIPS,首要选用ART加速器,能够最大极限的消除Flash存储器较慢然后约束MCU功用的发挥,这能够使CPU能够在所有作业频率下近乎零等候的办法,从Flash中运转程序。还有便是STM32F407带有硬件FPU处理单元,这样能够不必软件算法完结浮点运算,而直接选用硬件来完结浮点运算,这样就减小了编译器生成的代码量,并且运用更便利,浮点数只占用四个字节就能够表明的数据规模很大,因而不必忧虑核算后的数据溢出问题!进一步进步运算速度。

1.1.2 采样办法比较与挑选

计划一 经过DDS集成芯片发生一个频率安稳度和精度适当高的方波信号作为时钟信号。

可选用直接数字频率组成(DDS)芯片AD9851,AD9851为ADI公司出产的高功用器材,可与单片机经过简略的接口完结串行或许并行通讯。可完结外部输入频率操控字与芯片内部频率相位操控字之间的转化,能够十分简略的经过频率操控字调整输出频率,以及准确的调整输出信号的相位,输出信号幅值安稳,可是由于DDS操控也需求占用一部分MCU的IO口资源,并且DDS在价格上本钱有点高。

计划二 直接由MCU发生PWM波做为采样时钟信号。

可直接由STM32F407发生的PWM波,可完结频率,占空比可调的方波。最快IO口翻转速度能够到达84MHz,能够轻松完结想要的采样频率。由于输出的是3.3V的幅值的电压,与外围芯片相连,需求经过电平转化芯片转成5V,才干作为外围芯片的时钟信号。

计划三 采样时钟信号选用Linear公司出产的LTC1799供给。

LTC1799是一款精准型振动器,运用便利。它选用2.7V到5.5V单电源作业,并供给了轨至轨、占空比为50%的方波输出。CMOS输出驱动器保证了快速上升/下降时刻和轨至轨开关操作。频率设定经过电阻器调理,电阻阻值在 的规模内改变,以挑选处于100KHz到33MHz之间的任何一个频率。三态DIV输入担任决议驱动输出之前对主时钟进行1、10或100分频。

归纳上述计划,挑选计划三,选用一片LTC1799来发生15MHz的采样时钟信号。

1.1.3 AD采样芯片的证明与挑选

计划一 选用MCU内部ADC对采样信号进行采样。

STM32F407内部最大转化速率为7.2MSPS,并且被采样信号的幅值只能在0V到3.3V之间,能测得动态规模小,难以满意要求。

计划二 选用TI公司的8位TLC5510A作为AD采样芯片。

TLC5510A是选用高速CMOS技能,8位的,最大转化速率为20MSPS的AD转化芯片。支撑+5V电源供电,内部包括采样坚持电路,输出带有高阻态形式,以及带有内部参阅电阻。输出数据在时钟的下降沿有用,数据流水线结构导致了2.5个时钟的延时。并且高速AD遍及价格比较贵重,在满意输入信号在2V以上动态规模,TI公司可供请求的高速AD芯片只需TLC5510A这一种。

归纳上述计划,挑选计划二,在精度要求不高场合,选用TLC5510A作为高速采样芯片。

1.1.4 高速数据缓存芯片的证明与挑选

由于15MHz的高速数据流,假如中止来符号数据流的地址,由于MCU的中止呼应时刻有限,有12个时钟周期的中止延时,因而就需求外部存储器做高速数据缓存。

计划一 选用SRAM芯片作为外部高速数据缓存芯片。

选用IDT71024来做高速缓存,由于SRAM供给了地址线端口和数据输入和输出端口,假如用MCU来操控的SRAM的地址线,中止呼应不过来是反响不过来,假如用计数器作为地址计数器,原理是能够,可是实际操作作用欠安。

计划二 选用FIFO芯片作为外部高速数据缓存芯片。

IDT7205是单向异步FIFO的典型芯片,由IDT公司出产的,是一种高速、低功耗的先进先出双端口存储缓冲器。这种FIFO芯片内部的双端口RAM具有2套数据线,别离履行输入和输出功用,各自独立的写读指针别离在写、读时钟的操控下次序地从RAM中写、读数据。

归纳上述计划,挑选计划二,它无地址线,布线简略,只能是次序存取。

-

体系理论剖析与核算

2.1快速傅里叶改换(FFT)

DFT(离散傅里叶改换)是数字信号剖析与处理中的一种重要改换,它能够使数字信号处理能够在频域内选用数值运算的办法进行,大大增加了数字信号处理的灵活性,但直接核算DFT的核算量与改换区间长度N的平方成正比,当N较大时,核算量太大,所以在快速傅里叶改换(FFT)呈现曾经,直接用DFT算法进行谱剖析和信号的实时处理是不切实际的。

DFT的界说:设 是一个长度为N的有限长序列,界说 的N点离散傅里叶改换为

能进步DFT速度的仅有可运用的是因子 。 称为旋转因子 ,

, 可表明为

可表明为 具有以下两个重要性质。

具有以下两个重要性质。

①对称性

②周期性

运用 的周期性和对称性可把DFT的核算次数大大减小。

DFT分化法根本上分为两类:一类是将时刻序列X(n) (n 为时刻标号)进行逐次分化,由此得到的FFT算法称为按时刻抽取算法,另一类是将傅里叶交流序列X(k) ( k为频率标号)进行分化,叫做按频率抽取算法。对每一算法,按根本的蝶形运算的构成又可分为基2、基4、基8以及恣意因子等的FFT算法。不同基的FFT算法所需的核算量略有差异。之所以说略有差异是指并无数量级上的差异,乃至无成倍的不同。仅仅某种基的算法比另一种省几分之几罢了。

而本计划选用的便是ST公司官方固件库里DSP库中现已写好的关于FFT的库函数,调用的是基4复数序列1024个点的FFT函数库。

假定FFT之后某点n用复数 表明,那么这个复数的模便是

表明,那么这个复数的模便是 ,相位便是

,相位便是 ,频率便是

,频率便是 ,(其间N表明FFT要做的点数,n表明排序的点,Fs为采样频率)。依据以上的成果,就能够核算出n点

,(其间N表明FFT要做的点数,n表明排序的点,Fs为采样频率)。依据以上的成果,就能够核算出n点 ,

,

所对应信号的表达式为:

而关于n=1的点信号,是直流重量,起伏即为:

因而关于直流量要特别考虑,一是幅值是其它频率点的2倍,二是直流量不含有相位信息。

可是由于所做的点数有限,其会形成频谱走漏是必定的。因而并非要核算所有点的幅值,相位以及频率信息,而只需求核算出各个峰值点的幅值,相位以及频率即可表明采样信号各谐波重量的悉数信息。

因而算法模块要完结的功用:保存FFT之后峰值点的实部和虚部,以及峰值点所在的方位这几组点即可。

2.2窗函数的剖析与核算

在频谱剖析过程中,加窗是进步信号剖析精度的一个重要措施,对加窗函数的根本要求:时域为改进切断处的不接连状况(由于吉布斯现象形成的振动);频域为窗谱的主瓣窄而高,以进步分辩率,旁瓣幅值应小,正负替换挨近持平,以减小走漏和假频。因而在挑选窗函数的时分,应考虑被剖析信号的性质和处理要求,假如仅要求准确求出主瓣频率,而不考虑幅值精度,则可挑选用主瓣宽度比较窄而便于分辩的矩形窗,例如丈量物体的自振频率等;假如剖析窄带信号,且有较强的搅扰噪声,则应选用旁瓣起伏较小的窗函数,如汉宁窗(Hanning)等。

为了使加窗函数后的功率谱和幅值谱不受窗函数的影响,有必要依据必定的准则推导出康复系数。加窗后的康复系数一般恪守两个准则之一:幅值持平或能量持平的准则。

因而加窗模块要完结的功用:进步采样信号剖析的幅值精度。

频谱剖析中康复系数的运用准则

在频谱剖析中,依据不同用处选用不同康复系数,在进行倍频程和三分之一倍频程剖析时,为了使频带内总能量不变,必定要选用能量持平的康复系数;而进行谱剖析时,更关怀的是各峰值频率对应的幅值,此刻只能选用幅值持平的康复系数。

常用的各种窗函数的康复系数

2.3 A/D采样的剖析与核算

本体系选用的AD转化芯片为TLC5510A,TLC5510A是选用高速CMOS技能,8位的,最大转化速率为20MSPS的AD转化芯片。支撑+5V电源供电,内部包括采样坚持电路,输出带有高阻态形式,以及带有内部参阅电阻。输出数据在时钟的下降沿有用,数据流水线结构导致了2.5个时钟的延时。尽管AD转化数据输出有2.5个时钟延时,可是只需量化的成果是正确的和数据是次序输出,这个数据输出延时咱们能够不必关怀。外部还需求接一个4V的参阅电压,这样才干量化到0V~4V的输入信号。TLC5510A引脚图和时序图如下:

图2.3.1 TLC5510A的引脚图

引脚功用描绘:

由于TLC

在arm_math的最初部分是有这些编译操控信息:

#ifndef _ARM_MATH_H

#define _ARM_MATH_H

#define __CMSIS_GENERIC /* disable NVIC and Systick functions */

#if defined (ARM_MATH_CM4)

#include “core_cm4.h”

#elif defined (ARM_MATH_CM3)

#include “core_cm3.h”

#elif defined (ARM_MATH_CM0)

#include “core_cm0.h”

#else

#include “ARMCM4.h”

#warning “Define either ARM_MATH_CM4 OR ARM_MATH_CM3…By Default building on ARM_MATH_CM4…..”

#endif

#undef __CMSIS_GENERIC /* enable NV%&&&&&% and Systick functions */

#include “string.h”

#include “math.h”

便是说假如不运用CMSIS的,就会调用keil自带的规范库函数。不然就用CMSIS的界说。这儿由于是用的STM

3.有时分常会呈现编译过错,会呈现硬件过错,导致MCU锁住了,下不了程序。

解决办法便是硬件引导程序康复

STM32F407尽管芯片材料阐明端口能够忍耐+5V的电压,但这不代表其能够辨认+5的高电平,因而在读+5V的输入端口电平,需求用电平转化芯片将+5V转化成+3.3V的,不然读出的数据时一个错的。可是3.3V归于高电平,因而其能够驱动+5V作业的芯片。

参阅文献

[1] 万永革编著. 数字信号处理的MATLAB完结(第2版) 北京:科学出版社,2012.5.

[2] A.V.奥本海姆著. 离散时刻信号处理(第2版) 西安:西安交通大学出版社,2011.9.

[3] 李群芳著. 单片微型核算机与接口技能(第3版) 北京:电子工业出版社,2008.5.

[4] DSP常用算法的C言语完结

[5] Andrew Koenig著. C圈套与缺点. 北京:人民邮电出版社,2002.9.