1、 导言

触摸式图画传感器(Contact image sensor,简称 CIS)是由一排与扫描原稿宽度相同的光电传感阵列、 LED光源阵列和柱状透镜阵列等部件组成一种新式图画传感器。这些部件悉数集成在一个条状方形盒内,不需求别的的光学附件,没有调整光路和景深等问题,具有结构简略、体积小、使用便利等长处。在一些使用场合 CIS传感器比 CCD或 COMS等传感器有无法比拟的长处。在传真机、扫描仪、纸币清分兑零等范畴使用十分广泛。

在本文中选用杂乱可编程逻辑器材( CPLD)规划一个新式的CIS传感器操控器,完结了触摸式图画传感器的操控和图画数据的收集。

2、 硬件规划

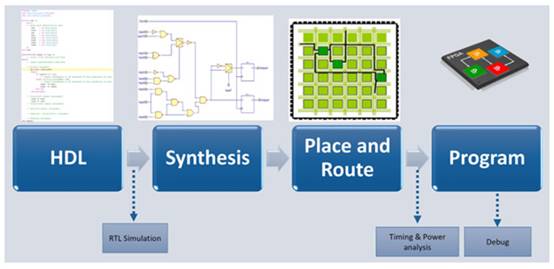

2.1体系总体计划

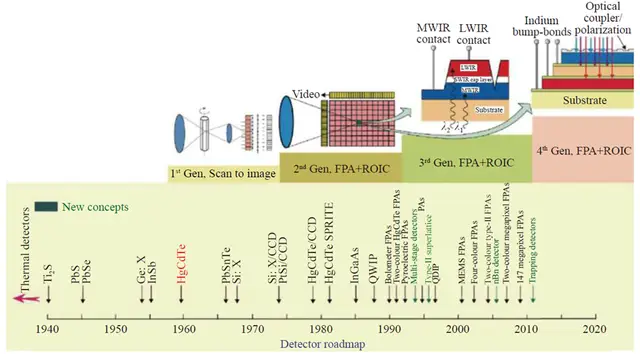

依据 CIS传感器的作业原理,其输出信号是串行输出的电压信号。因而,本文中的图画处理体系包含微处理器、CPLD模块、CIS传感器接口、信号差分扩大电路、图画信号的 A/D转化、双缓冲存储器接口等部分,然后完结图画的收集与处理。体系框图如图 1所示,

因为 CIS传感器的作业速度高,假如直接由微处理器(MPU)发生 CIS传感器的操控时序信号,则十分耗费微处理器的时刻和资源。因而,本驱动电路以 CPLD为操控中心,微处理器不直接操控 CIS传感器。微处理器只需求操控 CPLD的页使能信号( P_EN)和线使 能信号(L_EN)两个信号线。CPLD就能够主动完结 CIS操控时序的发生、A/D转化器操控时序的发生、数据的暂存和乒乓存储的总线切换等功用。这种选用 CPLD独立完结图画收集和数据存储,减少了微处理器对底层器材的操控,进步了微处理器在图画处理中的功率。

2.2 CIS操控模块与微处理器的接口规划

在图 1所示的图画处理体系中, CPLD首要完结两个使命:一是完结底层器材的操控,二是完结与微处理器 MPU的外围接口。图 1中,外围接口总线分为图画收集的操控线和缓冲存储器的读写总线两类。图画收集的操控线包含页使能信号和线使能信号两个信号。缓冲存储器的读写总线包含 8位数据线 D[0..7]、17位地址线 A[0..16]、读信号线 RD、写信号线 WR和选通信号线 CS。MPU经过 CPLD完结对 IS61C1024型缓冲存储器的读写。

2.3 CIS图画传感器的接口电路规划本文以FW2R216型CIS传感器为例,选用 EPM7128QC160型CPLD完结图画收集的操控。

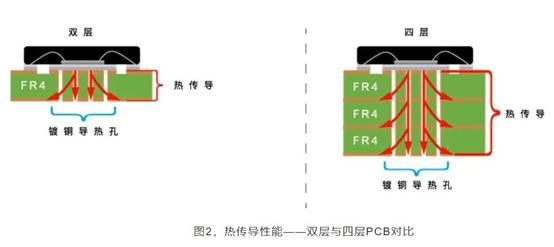

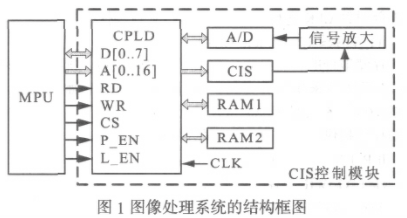

(1)CIS图画信号的扩大

CIS输出的图画信号幅值比较小,一般只要几百毫伏,并且是叠加在一个暗电流的直流信号上。因而要对信号进行扩大和零点校对。选用运算扩大器 LM7131构成差分扩大电路完结信号的调整,如图 2所示。图中,电阻 R1=R2,R3=R4,因而能够得到:

Vout=(Vsig-Vref)·R3/R1+V1

V1=Vref·R5/(R5+R6)

其间,Vref是为了去掉 CIS图画信号的暗电流重量,由基准稳压电源 LM285供给 1.25V的基准电压。V1电压是为了零点校对,由电阻 R5和 R6对 Vref分压后经电压跟从器取得。

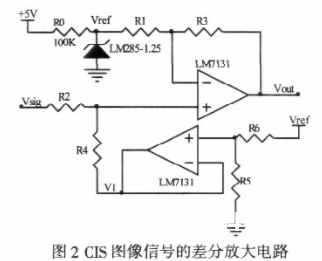

(3)A/D转化器的电路规划

因为灰度图画的灰阶一般为 256级,因而选用 8位的高速并行模数转化器 TLC5540,它的最高作业频率高达 40MHz,依托 5V单电源作业,并且内部带有基准电路构成分压电路取得参阅电压。+5V

TLC5540在其时钟信号的下降沿对输入模仿信号进行坚持和采样,在 2.5个时钟周期后将转化的数据输出到内部总线上。当 TLC5540读选通信号 OE有用时,数据输出到外围管脚上。 TLC5540的接口电路如图 3所示。

TLC5540的参阅电压由精细基准电压源 TL431、电阻 R6和 R7构成的电路供给。 TLC5540的 CLK管脚和 OE管脚由 CPLD直接操控,分别为 AD_EN和 AD_CLK。当 CPLD发生的 AD_EN为下降沿时,CPLD使能 TLC5540的 OE脚将数据 AD[0..7]读取到 CPLD的内部寄存器中,完结信号由模仿到数字的转化进程。

3、软件规划

3.1 CPLD的逻辑功用模块规划

CPLD是 CIS操控模块的中心部件。依据 CPLD需求完结的使命,将 CPLD的逻辑功用划分为不同的模块,包含时序操控模块、 A/D数据读取模块、数据暂存地址发生器、乒乓存储的总线切换和 MPU接口模块等。CPLD逻辑功用的模块如图 4所示。

3.2时序操控模块

时序操控模块是 CPLD在外部时钟信号 CLK操控下,依据 MPU供给的 P_EN与 L_EN信号,发生 CIS的操控时序、A/D转化器的操控时序、数据暂存的读写信号。

(1)CIS传感器和 AD转化器的操控时序发生

依据 CIS传感器的操控时序特性, CPLD为 CIS传感器供给时钟信号 CIS_CLK、选通信号 CIS_SI和光源操控信号 CIS_LED等。当微处理器将 P_EN置为高电平时,CPLD处于初始化状况。当 P_EN为低电平后,CPLD处于预备阶段。此刻,一旦微处理器给 L_EN管脚上发生一个脉冲信号,CPLD就随后主动发生 CIS_SI信号发动 CIS,一起 CPLD的内部计数器对外部 CLK进行计数。在依据计数值 CPLD发生 AD转化器的操控信号。这一时序电路的硬件描绘如下,其间 CNT是一个 0到 647的计数器。

if P_EN =‘1’ then

CNT《=0; AD_EN《=‘1’; CIS_SI《=‘0’;

elsif (CLK ‘event and CLK =’1‘) then

if L_EN =’1‘ then CNT《=1;

elsif CNT=647 or CNT=0 then CNT《=0;

else CNT《=CNT+1; end if;

if CNT=2 then CIS_SI 《=’1‘;

else CIS_SI 《=’0‘;end if;

if CNT》=64 and CNT《=640 then AD_EN《=’0‘;

else AD_EN《=’1‘; end if; end if;

3.3 A/D数据读取模块

A/D数据读取模块将模数转化器的输出数据暂存在 CPLD内部寄存器中。在 A/D转化器的读使能信号有用,即 AD_EN为 0时, CPLD为 ADC发生时钟 AD_CLK。CPLD在 AD_CLK的下降沿将 ADC的转化成果暂存在寄存器 D1中,其硬件的描绘如下。

if AD_CLK’EVENT and AD_CLK =‘0’ then D1(7 downto 0)《=AD(7 downto 0); end if;

3.4数据暂存的地址发生器

CIS传感器是依照一个个像素逐次串行输出。因而必须将图画数据依照地址逐次增一的格局存储在存储器 IS61C1024中。其写信号 A1_WR是由 A/D转化器的读使能信号 AD_EN和外部时钟 CLK进行逻辑与得到的,其硬件描绘如下。

A1_WR《=AD_EN and CLK;

存储地址的发生是由一个 17位计数器 A1完结,当 P_EN=1时表明图画收集没有开端,地址计数器 A1初始化为0。当 P_EN=0时,在写信号 A1_WR的上升沿地址增 1,为下一个数据的存储供给地址。这一进程的硬件描绘如下。

If P_EN =‘1’ then A1《=(others=》‘0’); elsif A1_WR‘event and A1_WR =’1‘ then A1《=A1+1; end if;

3.5乒乓存储功用的总线切换

为了进步体系的功率,当 CPLD在收集数据时,微处理器一起完结前幅图画数据的处理,因而在体系中选用双缓冲存储区[2]。当 CPLD向 RAM1写数据时,缓冲区 RAM2的总线操控权交给微处理器。当微处理器完结 RAM2中数据的处理且 CPLD完结当时幅图画的收集后,总线进行切换,使 CPLD将下一幅图画的数据写入 RAM2,此刻 RAM1的总线操控权切换给微处理器。总线切换由 P_EN的上升沿触发 EXCH信号取反。下面的程序是 EXCH信号在不同情况下,各总线作业状况的硬件描绘。双向数据总线的 VHDL硬件描绘如下。

D《=R1D when EXCH=’0‘ and RD=’0‘ else

R2D when EXCH=’1‘ and RD=’0‘ else

“ZZZZZZZZ”;

R1D《=D when EXCH=’0‘ and WR=’0‘ else

D1 when EXCH=’1‘ and A1_WR=’0‘ else

“ZZZZZZZZ”;

R2D《=D1 when EXCH=’0‘ and A1_WR=’0‘else

D when EXCH=’1‘ and WR= ’0‘ else

“ZZZZZZZZ”;

地址总线和操控总线切换进程的硬件描绘如下。

if EXCH =’0‘ then

R1A《=A;R1_WR《=WR;R1_RD《=RD;

R1_CE《=CS;R2A《=A1;R2_WR《=A1_WR;

R2_RD《=’1‘;R2_CE《=’0‘;

else

R1A《= A1;R1_WR《= A1_WR; R1_RD《=’1‘;

R1_CE《=’0‘; R2A《= A;R2_WR《= WR;

R2_RD《=RD; R2_CE《= CS;

end if;

4 、定论

图5给出了在 Quartus II 6.0中选用 EPM7128QC160型 CPLD对上述计划的仿真时序波形图,仿真成果与规划思维彻底符合。此驱动电路已在纸币清分设备中得到较好的使用。

本文作者立异点:以 CPLD为中心完结 CIS传感器时序驱动、A/D转化器操控、双缓冲区的乒乓总线切换以及微处理器接口等功用;微处理器不直接操控底层器材,进步了微处理器的功率;选用双缓冲区的乒乓作业方式,图画收集和图画处理完结并行作业,进步了图画处理体系的功能。

责任编辑:gt