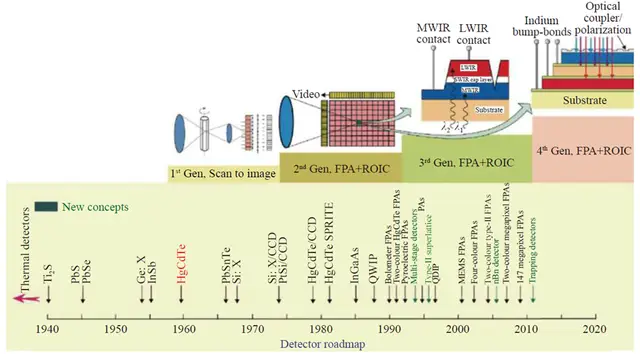

Cortex-M0体系结构包括:体系模型、存储器映射、反常中止。这篇文章首要解说Cortex-M0的体系模型。

操作形式和状况

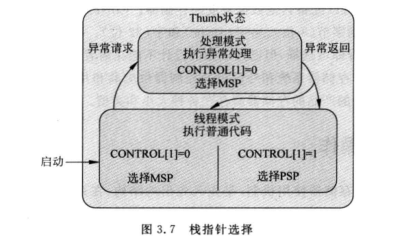

如上图所示,Cortex-M0包括两种操作形式和两种状况

Thumb状况(Thumb state)

处理形式

线程形式

调试状况

处理器发动后处于Thumb状况,在这种状况下,处理器能够处于线程形式和处理形式,线程形式时履行一般代码,处理形式时履行反常处理。线程形式和处理形式的体系模型简直如出一辙,仅有的不同在于线程形式经过装备CONTROL特别寄存器,能够运用进程指针。

调试状况仅用于调试操作,暂停处理器内核后,履行不会再履行。在这种状况下,调试器能够读取乃至改动内核寄存器的值。

处理器上电后默许处于Thumb状况的线程形式,履行一般代码。

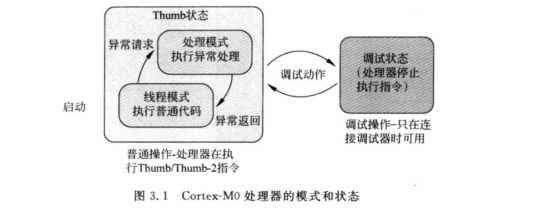

寄存器和特别寄存器

数据的解析和控制器的处理过程中,需求处理器内核寄存器的参加。假如需求处理控制器中的数据,这些数据需求先加载到处理器内核的寄存器(寄存器组中的摸个),处理完成后,假如有需必要,它们还会被送到存储器中,这种方法被称为“加载-存储架构”(load-store architecture)。

Cortex-M0有13个32位通用寄存器R0-R12,以及多个特别寄存器。

寄存器组包括16个32位寄存器,其间13个时通用的,其他三个具有特别用处。

R0-R12 通用寄存器

R0-R12为32位通用寄存器,因为16位thumb指令集在空间上的约束,许多Thumb指令只能操作R0-R7,它们被称为低寄存器,而想MOV之类的一些指令则能够运用悉数的寄存器。R0-R12寄存器的初始化值未界说。

R13,栈指针(SP)

R13为栈指针,对栈空间进行存取操作(经过PUSH和POP指令),Cortex-M0在不同的物理地址上有两个栈指针,一个为主栈指针(MSP),也被称为SP_main,一个指针称为进程栈指针(PSP),也为称为SP_process,只能用在线程形式。能够经过CONTROL寄存器,挑选运用那个栈指针。

在ARM处理器中,因为寄存器是32位的,所以PUSH和POP指令永远是32位操作,并且存取地址是32位字对齐(32位对齐)。在处理器上电过程中,中止向量表的头4字节会被去除(中止向量表在0x000000000地址),然后填充到MSP,作为MSP的初始值,PSP的初始值为界说。

一般运用操作体系是PSP进程栈指针才会被运用,这是因为操作体系内核的栈空间和线程级的应用程序的栈空间是彼此独立的。

R14,链接寄存器(LR)

R14为链接寄存器,用于存储子程序或许函数调用的回来地址。子程序或许函数履行结束,存储在LR中的回来地址将被装在到程序计数器PC中,以便调用程序能够持续履行。当产生反常中止时,LR会供给一个特定值,用于中止回来机制。

虽然Cortex-M0处理器的函数回来地址一直时偶数(最低位为0,因为最小的指令都是16位的),LR的0位时可读写的。为了指明当时处于thumb状况,一些指令需求函数地址最低位为1。

R15,程序计数器(PC)

R15为程序计数器,为可读写。读操作回来当时正在履行的指令加上4(这是由流水线的特性决议的),而写入R15会导致程序跳转履行,这和函数调用不同,链接寄存器不会更新。

Cortex-M0处理器指令是16位对齐的,所以PC寄存器的最低位有必要一直为0.不过在运用跳转指令BX或许BLX履行跳转履行时,PC的最低位应该被置1,以标明方针分支处于thumb程序区域。假如企图切换到Cortex-M0不知道的ARM状况,过错反常中止会被触发。

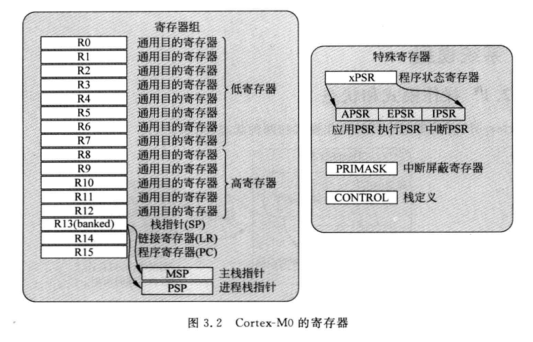

xPSR,组合程序状况寄存器

xPSR寄存器

xPSR寄存器

组合程序状况寄存器供给了程序履行信息和ALU(管用逻辑单元)标志,改寄存器由三个程序状况寄存器(PSR)组成,如上图:

应用程序状况寄存器(APSR)

中止程序状况寄存器(IPSR)

履行程序状况寄存器(EPSR)

应用程序状况寄存器

APSR包括了ALU管用逻辑单元标志,坐落xPSR最高4位,一般用于控制程序跳转:

N表明负号标志

Z表明零标志

C表明进位或借位标志

V表明溢出标志

中止程序状况寄存器

IPSR包括了当时正在履行的中止服务程序(ISR)编号,Cortex-M0的每个反常中止都会由一个特定的中止编号(表明中止类型)。这对调试时辨认当时的中止十分有用,并且在多个中止共用一个中止处理的情况下,能够看出放生的时哪个中止。

履行程序状况寄存器

EPSR包括了T位,该位用来表明当时是否处于Thumb状况。因为Cortex-M0处理器只支撑Thumb状况,所以T位一般为1.铲除该位(置零)后,履行吓一跳置零会触发硬件反常中止。

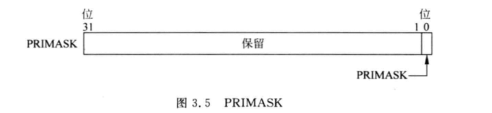

PRIMASK,中止屏蔽特别寄存器

PRIMASK仅有一位位宽,置位后,除了不行屏蔽中止(NMI)和硬件过错反常外的其他中止都会被屏蔽。实际上,此刻当时中止优先级被置为0,也便是最高等级。

要拜访PRIMASK寄存器,能够经过特别寄存器操作置零(MSR和MRS),也能够运用“改动处理器状况”置零(CPS)。在处理器对事情灵敏的应用时,需求操作PRIMASK寄存器。

CONTROL,特别寄存器

前面现已说到,Cortex-M0处理器具有两个栈指针。处理器形式决议了运用的栈指针,而处理器形式以来与CONTROL寄存器的装备。

复位今后,体系默许运用主栈指针,在线程形式下,经过装备CONTROL寄存器的榜首方位1,处理器能够切换至运用进程栈指针(条件是当时不是处在反常中止处理中)。在处理反常中止时(运行在处理形式下),体系只能运用主栈指针,CONTROL寄存器读出的值为0。要改动CONTROL寄存器的值,应该在线程形式下进行操作,或许凭借反常中止进入和回来机制。

为了兼容Cortex-M3,CONTROL寄存器的0位保存。在Cortex-M3中,第0位用于将处理器切换至用户形式,这个特性在M0中没有。