传统的数据传输运用渠道是依据PCI总线规划完结的。PCI总线是并行同享总线,具有数据传输速率慢等缺陷。跟着点对点高速串行PCI Express(Peripheral Component Int erconnect Express,PCI—E)总线的开展,依据PCI—E总线的新式数据传输运用渠道已逐步替代了传统的依据PCI总线数据传输运用渠道。PCI-E总线不仅在体系软件级与PCI总线兼容,且与PCI等传统总线比较具有更高的带宽和灵敏的可装备通道数。

以FPGA为中心规划数据传输运用渠道,具有硬件电路规划简略、可重构性、供给片上PCI—E IP硬核、并可完结SOPC功用等特色。所以在计算机、通讯等范畴获得了广泛运用,更使得高速体系规划不用过多地重视PCI—E总线的杂乱规划,大幅进步了规划的可靠性,缩短了规划的研制周期。本文规划完结了依据FPGA的PCI Express运用渠道。

1 计划施行根底

1.1 PCI-E协议标准

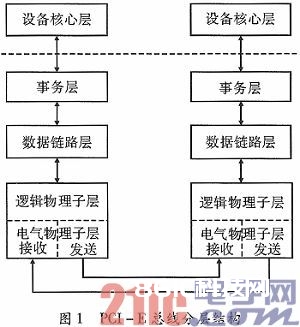

PCI—E作为第三代I/O技能由Intel发布,并随后被PCI—SIG (Peripheral Component Interconne—ct Special Interest Group)正式命名为“PCI Expres—s。作为串行衔接方法的总线,PCI—E协议标准界说了一种分层的设备体系结构,包括业务层(Transaction Layer)、数据链路层(Data Link Layer)和物理层(PhysicalLayer),一切数据的接纳和发送过程中均以包的方法在各层之间传输。PCI—E总线的层次结构如图1所示。

(1)业务层是PCI—E中的最上层,担任业务层包(Transaction Layer Packet,TLP)的封装与分化,并进行流速操控办理、数据包行列办理以及运用多虚拟通道供给服务质量(Quality of Service)。

(2)数据链路层是PCI—E的中间层,首要担任完结数据完整性查看、过错检测与纠正。数据链路层完结了包的应对和重传机制,每个包用一个仅有的标识来确保应对可正确地定位恳求,若犯错则重传犯错标识的一切后续包,以此确保数据的可靠性。

(3)物理层分为逻辑物理子层和电气物理子层。逻辑物理子层完结与数据链路层的数据交换、8b/10b编解码、并串和串并转化。电气物理子层担任对每路串行数据进行差分驱动传输。

(4)设备中心层并不归于PCI—E协议标准。其首要向业务层供给封装TLP所需的数据,或接纳业务层拆包后的数据。

1.2 FPGA器材选型

选用Altera公司的Cyclone IV GX系列FPGA为中心完结PCI—E数据传输运用渠道。该系列FPGA器材包括多达8个3.125 Gbit·s-1速率的全双工高速收发器,并支撑物理编码子层(PCS)、物理介质附加子层(PMA)和PCI—E IP硬核,可彻底完结PCI—E根本标准所需的2.5 Gbit·s-1速率、8b/10b编解码和PCI—E分层协议栈,并可削减运用渠道规划的难度,且加快了研制周期。

2 运用渠道规划

依据PCI—E总线规划了一种Windows XP操作体系下的数据传输及处理运用渠道,满意PCI—E根本标准所需的总线传输速率和分层体系结构,并可经过多种数据传输形式来适用于不同的运用场合,如数据收集、数据下发和数据处理等。运用渠道规划包括软件和硬件两部分组成,硬件部分包括FPGA内部逻辑电路,PCI—E IP硬核等;软件部分包括上位机操控程序和运用渠道在Windows操作体系下的驱动程序。

2.1 硬件规划

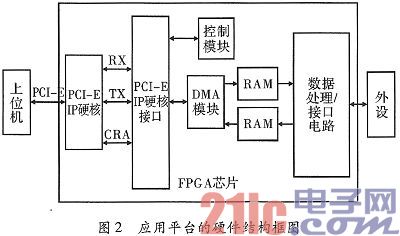

硬件规划首要包括PCI—E IP硬核接口、操控模块、DMA模块和数据处理/接口电路,运用渠道的硬件结构如图2所示。

(1)PCI—E IP硬核接口完结PCI—E IP硬核与设备中心层之间的数据桥接功用。PCI—E IP硬核完结了PCI—E的协议标准,还供给了与设备中心层的接口。Cyclone IV GX系列器材供给的PCI—E IP硬核与设备中心层的接口为一组内存映射(Avalon Memory Map)接口,其间包括TX接口、RX接口和CRA接口。

TX接口是指由设备中心层建议的数据传输接口,映射了业务层存储器的读和写恳求业务。TX接口支撑突发数据传输,完结设备中心层与PCI—E硬核接口的高速数据传输。

RX接口是指由上位机建议的数据传输接口,是对业务层存储器读和写业务的映射。用作上位机发送操控指令的接口。

CRA接口是PCI—E IP硬核装备空间拜访接口,经过此接口可拜访PCI—E IP硬核的装备寄存器,并完结对PCI—E IP硬核的初始化和装备。此接口可由设备中心层直接拜访或上位机经过RX接口拜访。

(2)操控模块首要完结设备中心层数据传输和数据处理操控。上位机经过RX接口向操控寄存器写入指令字,操控模块则经过解析指令字,发动相应的模块完结指令。依据运用的不同,操控模块可由CPU或电路完结。CPU可经过编写不同的运用软件来完结相对杂乱的操控,但运转速率有限。尽管电路的运转速率较高,但杂乱的操控指令将使电路的规划变得杂乱。

(3)DMA模块完结上位机与运用渠道之间高速数据传输。该模块包括两个独立的DMA通道,通道1操控数据从上位机到运用渠道的数据下发传输;通道2操控数据从运用渠道到上位机的数据上传。上位机经过RX接口操控运用渠道上的DMA模块完结数据下发和上传操作。运用渠道上包括下发和上传缓存,别离缓存来自上位机的下发数据和来自外设输入的上传数据。每个缓存均由两块独立的8 kB RAM组成,两块8 kB RAM选用乒乓作业方法,完结不间断的高速数据传输。

(4)数据处王里/接口电路是PCI—E设备的功用模块,完结PCI—E运用渠道的数据处理或接口电路功用,如数据收会集完结收集设备的接口电路,或在图画处理中完结对图画信号的处理算法等。

2.2 传输形式一

适用于高速数据上传,这种形式首要是将外设收集到的数据经过PCI—E总线数据传输运用渠道高速上传至上位机。其作业流程如下:

(1)将渠道装备为上传形式。

(2)由上位机经过RX接口向操控模块写入数据上传指令,而操控模块在接到指令后发动外设开端收集数据,外设将收集的数据经过数据处理/接口电路送入FPGA内部两块8 kB的缓存RAM中。

(3)操控模块一起发动DMA模块,将FPGA内部两块8 kB RAM缓存的输入数据选用乒乓作业方法上传到上位机。

(4)当DMA数据传输完结时,经过RX接口告诉上位机数据传输完结,上位机选用查询方法进行数据提取等项操作,至此一次传输使命完结。

2.3 传输形式二

传输形式二适用于高速数据下发,这种形式首要是将上位机数据经过PCI—E总线数据传输运用渠道高速下发至外设。其作业流程如下:

(1)将渠道装备为下发形式。

(2)由上位机经过RX接口向操控模块写入数据下发指令,操控模块在接到指令后发动DMA模块从上位机中读出数据,并写入到8 kB RAM中。

(3)一起数据处理/接口电路选用乒乓作业方法从8 kB RAM中读出数据,并输出到外设。

(4)当DMA数据传输完结时,经过RX接口告诉上位机数据传输完结,上位机选用查询方法获取DMA数据传输状况,至此一次传输使命完结。

2.4 传输形式三

传输形式三适用于高速数据上传或下发,这种形式中PCI—E运用渠道先完结对上位机中待处理数据的下发,然后将FPGA处理后的数据再上传到上位机。传输形式三可看作形式一与形式二的混合运用。其不同之处在于,形式三履行形式一操作,或履行形式二操作,不能两种一起履行。形式三适用于高速数据灵敏收发的作业方法。相关于形式一或形式二来说,形式三收发速率较低。

2.5 软件规划

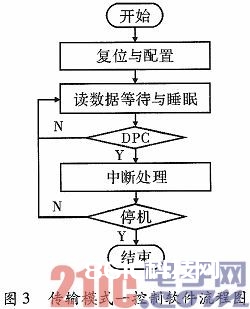

软件规划包括运用渠道的设备驱动和不同传输形式下的操控软件规划。传输形式一的操控软件流程如图3所示。

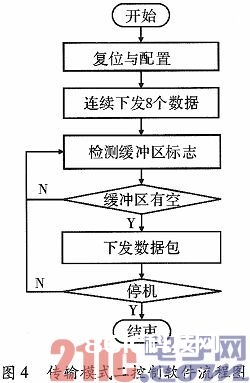

传输形式二的操控软件流程如图4所示。

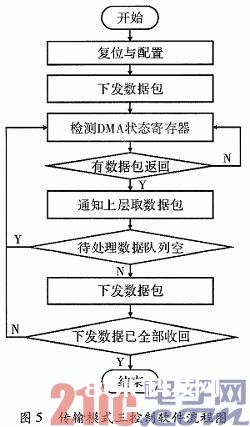

传输形式三的操控软件流程如图5所示。

设备驱动是计算机体系中软硬件的交互接口,此运用渠道的设备驱动依据Windows下的WDF(Windows Driver Foundation)结构完结。为进步驱动功率及通用性,此规划的设备驱动将内核态的硬件资源悉数映射到了运用空间,详细操控由各形式操控软件完结。

3 验证与完结

运用渠道选用Altera公司型号为EP4CGX50CF23C6的FPGA器材为中心,研制规划出PCI—E X4通道PCB板卡,运用Verilog HDL言语规划FPGA内部硬件电路,并在Qusrtus II 12.0开发环境下进行规划完结。依据Windows XP操作体系编写PCI—E运用渠道驱动,进行验证测验。受所选FPGA器材的PCI—EIP硬核约束,仅以PCI—E根底标准1.1版别进行验证。在传输形式一中,由运用渠道上的FPGA电路模仿外设生成的随机数作为测验数据包;在传输形式二中,由上位机软件发生随机数作为测验数据包。测验数据包选用接连生成方法,生成速率>8Gbit·s-1。测验成果选用计算均匀方法,即从一次接连10 s的数据传输量中,计算出数据的传输速率。

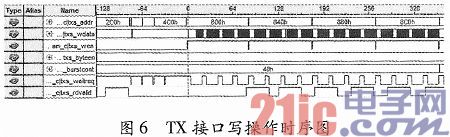

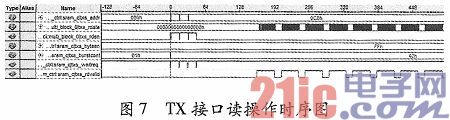

传输形式三下Signal Tap II逻辑分析仪捕获的作业包长为2 kB时的TX接口写和读操作时序图如图6和图7所示。

图6中txs_addr表明输出缓冲区地址,0x800表明输出缓冲区开始地址;txs_wdata表明写数据;txs_wen为高电平有用写使能;txs_byteen表明字节使能;burstcont表明TX接口一次写突发的数据长度,0x40表明此次突发长度为512字节;txs_waitreq表明TX接口等候恳求,为低电平时方可进行TX接口写操作。关于2 kB的包,TX接口需进行4次写操作,每次写512字节才可将FPGA内的上传缓存RAM中的数据包写到上位机内存中。

图7中txs_addr表明输入缓冲区地址,0x000表明输入缓冲区开始地址。txs_rdvalid为高电平时txs_rdata读数据才为有用数据。关于2 kB的包,TX接口读操作需进行4次,每次读512 Byte才干将上位机内存中的数据包读到FPCA内的下发缓存RAM中。

验证测验成果如表1~表3所示。传输形式一和传输形式二的测验速率低于PCI—E理论速率。因实践进行DMA传输时,需消耗必定时刻,一起数据在PCI—E IP硬核传输过程中也不可避免的会发生必定的时刻损耗,这些下降了数据的传输速率。传输形式三包括有上传和下发两种作业方法,此形式下上传和下发不能一起作业,实践传输速率显着下降,此外还包括传输形式一和二所提及的原因。

4 结束语

介绍了一种依据FPGA的PCI—E运用渠道规划,且描绘了3种不同的数据传输形式,以Windows XP操作体系为验证渠道,别离对3种传输形式进行了完结及验证,体系作业安稳,资源运用率较高,最高传输速率可达7.12 Gbit·s-1。此运用渠道的规划与完结,为需求构建各种高速数据传输体系的规划师供给了参阅。