摘要 在通讯设备、成像设备、工业仪器仪表等需求很多数据的体系中,要求数据转化级供给越来越宽的分辨率和越来越高的采样率。并行接口的物理布局和串行LVDS办法的比特率约束,给规划人员带来技能妨碍。文中依据Xilinx Vertx6 FPGA的GTX高速串行接口完结了JESD204B协议,有用地处理了传统收集数据并行传输时的各种问题。

要害词 高速串行接口;GTX;Xilinx VertX6;JESD204B

跟着转化器分辨率和速度的进步,对更高功率接口的需求也随之增加。JESD204接口可供给这种高功率,较之CMOS和LVDS接口产品在速度、尺度和本钱上更有优势。选用JESD 204的规划具有更高的接口速率,能支撑转化器的更高采样速率。此外,引脚数量的削减使得封装尺度更小且布线数量更少,这些都让电路板更简略规划而且全体体系本钱更低JESD204规范经过两次更新,现在版别为B。由于该规范已为越来越多的转化器供货商、用户以及FPGA制造商所选用,它被细分并增加了新特性,进步了功率和施行的便利性。此规范既适用于模数转化器(ADC)也适用于数模转化器(DAC),还能够作为FPGA的通用接口。

1 JESD204协议

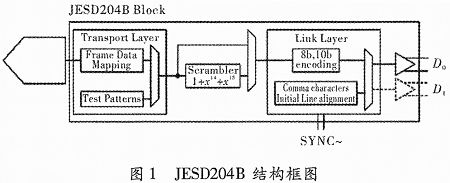

JESD204B协议体系结构能够分为物理层、链路层、传输层和使用层其结构原理框图如图1所示。

物理层完结高速串行信号的发送和接纳完结数据串并、并串转化以及编解码处理。接口选用电流形式逻辑(CML)驱动器和接纳器的差分对组成,通讯速率界说在 312.5 Mbit ·s-1与3.125Gbit·s-1之间。差分电平界说为标称800 mV峰峰值、共模电平规模是0.72~1.23 V。该链路运用8h/10b编码选用嵌入式时钟。这样便无须额定的时钟线路,避免了高速速率下传输数据与额定的时钟信号对齐的复杂性。链路层担任编码帧数据。校验数据,增加帧的鸿沟和流量操控。链路层只发送和接纳帧,并不需求知道帧的内容。传输层的作业是将A/D采样信息从数据流中提取出来。

2 JESD204B协议计划

2.1 Xilinx V6 FPGA

Virtex-6 FPGA是Xilinx公司推出的一块高性能低功耗FPGA。其内嵌8~72个千兆位收发器GTX。每个GTX收发器都集成了发射器和接纳器功用,能以 480 Mbit·s-1~6.6 Gbit·s-1的数据速率运转。经过选用依据FPGA逻辑的过采样技能,可支撑较低的数据速率。每个GTX收发器都有很多用户界说的特性和参数,这些特性和参数可在器材装备器材界说,也有许多能够在运转过程中进行修正。GTX发射器实质上是一款并串转化器,输出运用单通道差分电流形式逻辑(CML)信号,TXOUTCLK是进行恰当共处的串行数据时钟,可直接作为来自内部逻辑的并行数据寄存器。输入的并行数据由一个小型FIFO供给,可选择运用 8b/10b、64b/66b算法对齐进行修正,以确保满意数量的跳变。输出信号摆幅可通以经过程序设定,其预加剧也可编程然后补偿印刷电路板的损耗和其他互联特性。将输入的位差分信号转化为并行字流位宽可为8、10、16、20、32或40。可经过可编程均衡器,并运用FREF输入对时钟辨认进行初始化,无须图例的时钟线路。数据形式选用不归零(NRZ)编码,可经过选定的编码计划确保充沛的数据跳变。随后运用RXUSRCLK时钟将并行数据传输到 FPGA逻辑中。

GTX接口很多特性使其能够便利地完结PCI—E、SATA、SAS等高速串行接口的物理层与链路层桥接。能够考虑运用GTX接口完结JESD204B协议,以正确解析JESD204B接口ADC转化器宣布的数据。

2.2 JESD204接口ADC转化器

运用的ADC为TI公司出产的ADS42JB69,它是一款高线性、双通道,16位,250 MSample·s-1的模数转化器。该器材支撑JESD204B串口,数据速率高达3.125 Gbit·s-1。经缓冲的模仿输入在大幅下降采样坚持毛刺脉冲能量的一起,在宽频率规模内供给共同的输入阻抗,这使得它能够轻松地将模仿输入驱动至极高输入频率。采样时钟分频器可完结更灵敏的体系时钟架构规划。此期间选用内部颤动算法以在宽输入频率规模内供给超卓的无杂散动态规模(SFDR)。

2.3 协议的完结

协议的完结是完结对AD42JB69的A/D采样数据进行读取。物理层完结了数据在线路上的传输,能够直接运用GTX与A/D相连完结。 A/D作为发送端FPGA作为接纳端,链路层完结的主要功用是线路编码和对操控字符的查看。GTX接口内嵌了8b/10b编解码模块和操控字符检测模块,能够便利地完结与JESD204B规范设备的对接。在FPGA中依据GTX完结JESD204B协议,其难点主要有时钟的装备,以及对协议据帧的解析。

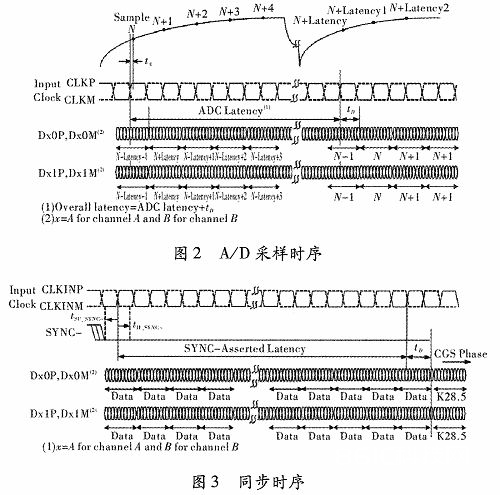

从时序图能够看出,由A/D的采样时间到该时间的采样数据被FPGA接纳到存在一个延时。

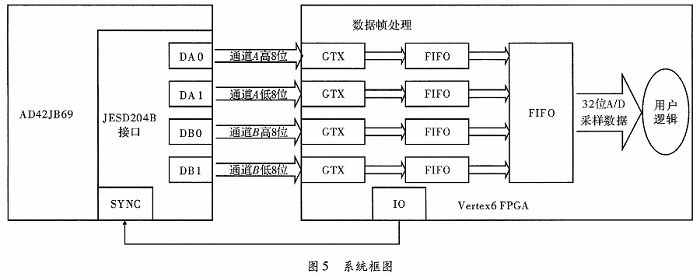

工程中需求满意A/D采样率200 MSample·s-1。AD42JB69的JESD204接口能够装备为四线形式和两线形式。依据项目需求,应该运用四线形式才干到达200 MSample·s-1的采样要求。在四线形式下A/D的数据映射联系如表2所示。其间DA0、DA1、DB0、DB1别离接4个GTX接口。传输两个 A/D转化器采样数据的高8位和低8位。由于采样时钟与传输时钟共同,JESD204设备先将A/D采样的数据进行8b/10b编码然后用与采样频率相同的时钟将编码后的数据进行并串转化并发送给接纳端。核算可得到发送线速度为2.0 Gbit·s-1。因而FPGA需求正确装备RXPLL_DIVSEL_REF、RXPLL_DIVSEL45_FB、TXPLL_DIVSEL_FB、 TXPLL_DIVSEL_OUT的值使GTX接纳线速度能安稳作业在2.0 Gbit·s-1。

2.4 数据帧解析的完结

在串行数据收发过程中怎么判别数据的鸿沟尤为要害,JESD204协议选用字同步和帧同步处理数据鸿沟问题。经过在数据流中刺进操控字符完结字同步和帧同步。以下列出JESD204B中运用的操控字符以及他们的功用。FPGA经过对操控字符的正确解析能够完结时钟康复、数据鸿沟确认,对齐等。

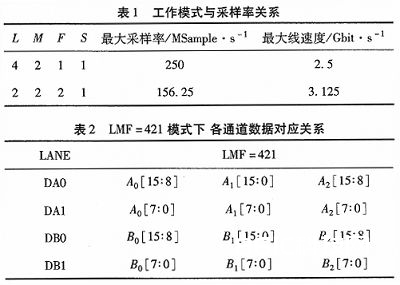

/K/=/K28.5/操控字符用来完结字同步。接纳端能够经过拉低

使发送端继续发送/K28.5/操控字。当接纳端接纳到接连的4个/K28.5/字符后字同步树立。此刻FPGA作为接纳端现已完结了时钟康复,Comma字符检测。字同步树立今后进行帧鸿沟确认。接纳端拉高

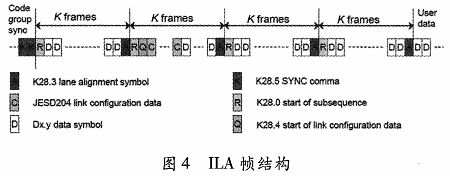

后发送端中止发送/K/28.5/操控字,开端发送ILA帧。ILA帧的结构如图4所示,每个ILA帧包括4个多帧(Multi—Frame)。

/R/=/K28.0/做为每个多帧(Multi—Frame)的开端标志。

/A/=/K28.3/用于串行数据流中的多帧(Multi—Frame)同步。作为多帧(Multi—Frame)的完毕标志。

/F/=/K28.7/用于串行数据流中的帧(Frame)同步,当当时帧的最终一个8位字节(Octet)等于前一帧的最终一个8位字节(Octet)时用/F/=/K28.7/操控字替换当时帧的最终一个字节。

经过上述规矩检测K字符并将A/D采样数据存入FIFO。当完结了操控字符检测后需求将A/D的采样数据进行拼接,由于每路A/D转化器都是以凹凸字节分隔的方法传输数据的,因而要严厉确保采样时钟的同步。体系运用两级FIFO来对A/D采样数据进行缓存。榜首级4个FIFO完结采样数据凹凸字节的同步,其存储深度为16 Byte,4个FIFO的时钟别离接4个GTX的RXUSRCLK,当FIFO存储数据到达10时开端读出数据,这样就能确保4个FIFO的输出由一个时钟同步。第二级FIFO作为数据缓存,为用户逻辑供给简略接口,深度为4 kByte。用户逻辑接口有RD_CLK,RD_READY。当FIFO存储深度到达4 000时RD_READY信号拉高。能够经过判别该信号开端读取数据。RD_CLK需求>200 MHz,每次读取4 kByte数据后再等候RD_READY信号有用,这样循环就能够将A/D采样数据接连地读入到用户逻辑。

3 试验剖析

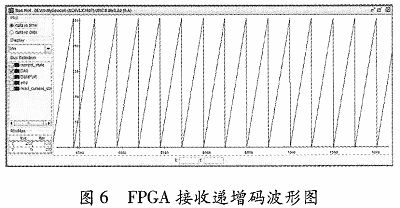

AD42JB69中包括了22个8位操控寄存器能够运用SPI接口对芯片的作业方法进行灵敏的装备。能够装备芯片输出递加码、随机码、零 -交错码、正弦信号等多种测验码源。这些测验码源能够用于验证接口传输数据的正确性,试验选用递加码作为测验码源便利发现过错,图6所示为运用 Chipscope调查FPGA接纳到的递加码波形。

4 完毕语

跟着传送速率的不断进步,并行传输技能中的同步码串扰等问题越来越严峻,已不能满意高速数据传输的要求,成为工程使用瓶颈。笔者在剖析FPGA中高速串行收发器CTX功用和JESD204协议后。完结了一种A/D收集数据的串行传输方法,处理了并行传输中遇到的问题。用Verilog言语编写了 JESD204协议操控核,节省了工程本钱。