1 导言

I2C总线是PHILIPS公司推出的新一代串行总线,因为其结构简略、灵敏,各结点具有独立的电气特性,可完结电路的模块化、规范化而被广泛使用。现在许多MCU都带有I2C总线接口,对没有I2C总线的MCU,可选用软件模仿,有通用软件包能够运用,但功用比较简略。在MCU(以Motorola 68000系列为例)和CPLD电子体系规划中,使用CPLD器材资源,依照I2C总线协议规范形式,规划了功用完善的I2C总线操控器,给出了规划思路和完结办法。

2 I2C总线操控器的规划与完结

2.1 I2C总线操控器的原理图

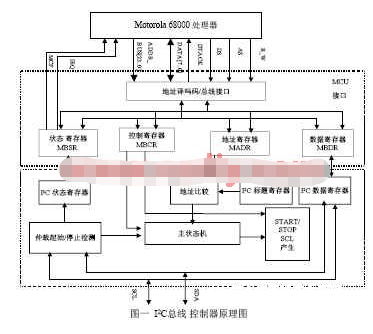

I2C总线操控器的规划选用VHDL言语描绘,经编译、归纳、适配,下载到详细的CPLD方针器材中,即可完结I2C总线操控器功用。其原理图如图一所示,该规划包含MCU接口和I2C总线接口两大部分。

2.2微处理器(MCU)接口逻辑的规划

MCU接口逻辑包含:地址译码/总线接口、状况寄存器(MBSR)、操控寄存器(MBCR)、地址寄存器(MADR)和数据寄存器(MBDR)等组成。I2C总线操控器的微处理器接口支撑异步字节数据传输协议,该协议的履行是经过MCU对I2C总线操控器中有关寄存器读写完结的,MCU读写协议如图二所示。

2.2.1地址译码/总线接口的规划

在I2C总线操控器中对MCU数据读/写协议的履行由MCU总线接口状况机完结,整个状况机包含闲暇状况、地址译码状况、数据传输状况和应对状况。当MCU设置读/写操作、输出要拜访的I2C操控器中寄存器地址信号,并使地址选通信号有用时,状况机从闲暇状况进入地址译码状况。若I2C操控器中寄存器被寻址且数据选通信号有用,状况机从地址译码状况进入数据传输状况:假如是读周期,I2C操控器将被拜访的寄存器中数据放置在MCU接口总线上;假如是写周期,I2C操控器将从MCU接口总线取数据锁存到I2C操控器的内部被拜访的寄存器中,状况机主动进入应对状况,此刻,DTACK信号有用标明,假如是读周期,MCU即可从MCU接口总线读取数据;假如是写周期,数据已锁存到I2C的内部寄存器中。

2.2.2 MCU接口特别功用寄存器的功用

MCU接口地址线共24根,其中高16位为基址(MBASE),用于确认I2C操控器的地址,低8位为MCU接口中特别功用寄存器的地址。

1)地址寄存器(MADR):寄存器地址为MBASE+$8Dh,寄存I2C操控器作业在从机形式时的从机地址。从机地址占高7位,最低位未用。

2) 操控寄存器(MBCR):寄存器地址为MBASE+$91h,发生操控信号,各位功用如下:

![]()

MEN:I2C操控器使能。该位为1时,操控寄存器的其他各位才有用;MIEN:中止使能;

MSTA:主/从形式转化。当MCU使该位从0变为1,I2C进入主机形式,并发生开始条件;若清0,发生中止条件,并转化为从机形式;

MTX:主机发送/接纳形式挑选。置1,主机发送,清0,主机接纳;

TXAK:传输应对使能。置1,无应对;清0,有应对;

RSTA:重复开始条件。I2C操控器在主机形式,写入1,发生重复开始条件;若总线被其他主机占用,写入1时,读回0。

3)状况寄存器(MBSR):寄存器地址为MBASE+$93h,各位设置与功用如下:

![]()

MCF:数据传送标志位,当一字节数据正在传输时,为0,一字节数据传输完毕,置1;

MASS:从机地址寻址标志位。当I2C操控器中地址寄存器的值与I2C总线传输的地址匹配时,置1,否则为0;

MBB:I2C数据总线忙标志位;

MAL:裁定丢掉标志位。当I2C操控器裁定丢掉时,由硬件置1,MCU的软件清0;

SRW:从机读/写标志位。I2C作业于从机形式,主机从I2C操控器读,置1;写,清0;

MIF:中止恳求标志位。当MIEN置1,且有中止恳求时,该方位1,在MCU的中止服务程序中,由软件清0;

RXAK:接纳应对信号标志位。有应对信号接纳,置1;无应对信号接纳,清0。

4) 数据寄存器(MBDR):寄存器地址为MBASE+$95h,在物理上,数据寄存器映射成两个独立的寄存器,一个用于发送数据,一个用于接纳数据,当MCU拜访它们时,两个寄存器共用一个地址。

2.3 I2C接口逻辑的规划

I2C接口首要包含:主状况机、开始条件/中止条件/SCL时钟信号的生成、裁定/开始条件/中止条件的检测、I2C状况寄存器、I2C数据寄存器、地址比较、和I2C标题寄存器模块等组成。

2.3.1裁定、开始条件/中止条件的检测

I2C操控器在下列状况将发生裁定丢掉:1) I2C操控器在主机形式,在地址或数据发送周期,当主机发送“1”,但在数据线上的采样值“0”;2) I2C操控器在主机接纳形式,在数据接纳周期的应对位,当主机发送“1”,但在数据线的上采样值“0”;3)当总线忙时,MCU妄图发生开始条件;4) I2C操控器在从机形式,MCU妄图发生重复开始条件;5) I2C操控器在主机形式,没有发生中止恳求,但检测到中止条件。当I2C操控器检测到开始条件时,数据总线忙标志方位1,检测到中止条件时,数据总线忙标志位清0。

2.3.2 SCL、SDA、开始、中止条件的发生

该模块完结如下功用: 1)答应任何主机操控总线,一旦I2C总线操控器操控总线,将发生开始条件;2)发生SCL串行时钟信号,且对SCL进行逐位裁定,满意时钟同步协议;3)I2C总线操控器在发送形式时从数据寄存器(MBDR)发送数据到SDA数据线上;4)若I2C总线操控器检测到裁定丢掉,将持续发生SCL信号直到丢掉裁定的该字节结尾;5)当有重复开始条件和中止条件恳求时,发生重复开始条件和中止条件。

2.3.3 I2C接口主状况机

I2C接口主状况机如图三所示,不管I2C操控器作业于主机仍是从机形式,这个状况机都适用。当裁定丢掉或作为从机被寻址时,I2C操控器当即从主机形式转化为从机形式。

在HEADER状况,I2C作业在主机形式时,一方面从数据寄存器(MBDR)发送标题到I2C总线上,另一方面将I2C数据线上的数据逐位接纳到标题移位寄存器内,当8位数据悉数移入时,进入ACK_HEADER状况。在ACK_HEADER状况,I2C操控器于主机形式,采样SDA的值, 然后决议是否有从机应对,假如从机不应对,进入STOP状况,等候生成中止条件;假如从机有应对,标题移位寄存器中最低位决议I2C操控器是接纳仍是发送数据,状况转化到RCV_DATA或XMIT_DATA状况。一起,不断地将地址寄存器(MADR)的值与标题移位寄存器的值进行比较,若地址匹配,I2C操控器作为从机被寻址并当即转化为从机形式。状况寄存器(MBSR)中的从机寻址标志位MAAS置位,将TXAK位发送到SDA线上应对当时的主机,相同标题移位寄存器中最低位决议数据传送方向和下一状况。

3 结语

本文依据I2C总线规范的规范形式,在MCU和CPLD归纳使用体系中规划了I2C总线操控器。在实践使用体系中嵌入该IP核,能够节省本钱,进步体系的适用范围和可靠性,具有很高的参阅规划价值和工程实用价值。

责任编辑:gt