1.前语

跟着电子技术的迅速发展,使得电子电路的规划日趋杂乱,单片机由于具有高集成度、高稳定性和本钱低价等特色,因而在电子规划中得到越来越广泛的运用。

榜首,运用数码显现管尽管本钱低价,可是显现内容十分有限且单一,不能满意越来越多的显现需求;第二,运用CRT或许五颜六色液晶显现器可以显现更多的内容,可是存在着规划杂乱化、进步规划本钱和浪费资源等坏处。因而,实践工作中迫切需要一种简略有用,本钱低价,规划简略的显现其产品。

2.基本原理

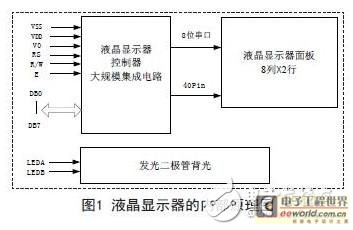

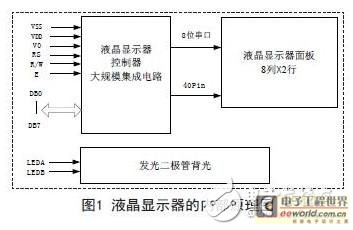

LC0811-SL由液晶显现器控制器和液晶显现器面板以及发光二极管背光三部分组成。其间液晶显现器显现控制器是整个显现器的中心部分。其内部结构图如图1所示。

2.1 电源

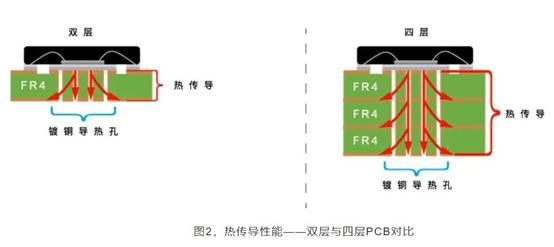

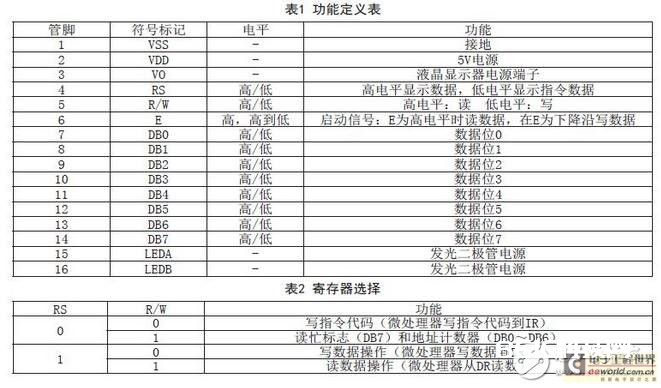

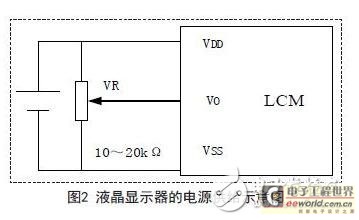

液晶显现器运用5V直流电源,电源供应示意图如图2所示。

2.2 管脚功用界说

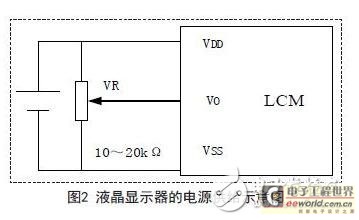

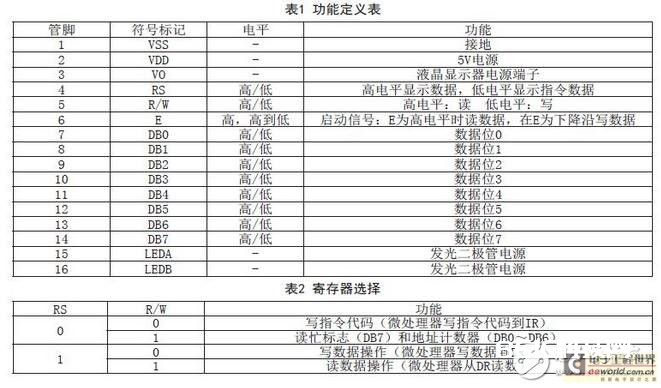

LC0811-SL具有16个管脚(PIN),详细功用界说如表1、表2所示。

2.3 存放器

LCD控制器有2个8位存放器,指令存放器(IR)和数据存放器(DR)。

指令存放器(IR)是一个只写存放器,既用于存储指令代码如清显现或许光标移位,又用来存储显现数据RAM(DD RAM)地址或许字符发发生器RAM(CG RAM)地址。

数据存放器(DR)是一个读写存放器,用于暂存对DD RAM或CG RAM读/写的数据,数据写入DR是经过一个显现控制器的内部操作主动写入到DD RAM或CG RAM.一起,DR也用来存储从DD RAM或CG RAM读出的数据。当地址信息写入IR,经过一个内部操作从DD RAM或CG RAM读出数据到DR,此刻的数据传输彻底经过读DR来完结。履行完一个从DR的读操作后,数据保存在DD RAM或CG RAM,下一地址送到DR,为下一个读周期做准备,如表2所示,存放挑选器(RS)信号决议两个存放器中的哪一个被选中。

2.4 忙标志(BF)

当忙标志位是1(即高)时履行一个内部操作而且下一个指令是不能被承受的。

当RS=0而且履行完一个读操作时,忙标志位输出到DB7,下一个指令只要在忙标志位为0(即低)时才可以被写入。

2.5 地址计数器(AC)

地址计数器分配地址给D D R A M或C GRAM,当一个指令的地址写入IR,地址信息从IR送到AC,这个指令一起决议DD RAM或CGRAM的挑选。从DD RAM或CG RAM完结一次读/写操作后,地址计数器(AC)主动减1或许加1,当RS=0而且读操作完结后,AC中的内容输出到DB0DB0~DB7.

2.6 显现数据存储器(DD RAM)

DD RAM用8位字符代码的方式来存储显现数据,容量是80*8或许80字节,DD RAM不用于显现时,可用作通用的数据R A M.

DD RAM地址是用AC来设置而且用16进制表明,这个地址计数器可以经过“Set DD RAMAddress”指令进行写操作,用“Read BusFlag and Address”指令进行读操作。如图3所示,在读/写时,数据位DB0~DB6代表DDRAM地址,DB7为忙标志位。

2.7 字符发生器ROM(CG ROM)

字符发生器ROM(CG ROM)从8位字符代码发生5×7点阵或许5×10点阵字符图形,可以发生等于192种5×7点阵字符图形和32种5×10点阵字符图形。

1.前语

跟着电子技术的迅速发展,使得电子电路的规划日趋杂乱,单片机由于具有高集成度、高稳定性和本钱低价等特色,因而在电子规划中得到越来越广泛的运用。

榜首,运用数码显现管尽管本钱低价,可是显现内容十分有限且单一,不能满意越来越多的显现需求;第二,运用CRT或许五颜六色液晶显现器可以显现更多的内容,可是存在着规划杂乱化、进步规划本钱和浪费资源等坏处。因而,实践工作中迫切需要一种简略有用,本钱低价,规划简略的显现其产品。

2.基本原理

LC0811-SL由液晶显现器控制器和液晶显现器面板以及发光二极管背光三部分组成。其间液晶显现器显现控制器是整个显现器的中心部分。其内部结构图如图1所示。

2.1 电源

液晶显现器运用5V直流电源,电源供应示意图如图2所示。

2.2 管脚功用界说

LC0811-SL具有16个管脚(PIN),详细功用界说如表1、表2所示。

2.3 存放器

LCD控制器有2个8位存放器,指令存放器(IR)和数据存放器(DR)。

指令存放器(IR)是一个只写存放器,既用于存储指令代码如清显现或许光标移位,又用来存储显现数据RAM(DD RAM)地址或许字符发发生器RAM(CG RAM)地址。

数据存放器(DR)是一个读写存放器,用于暂存对DD RAM或CG RAM读/写的数据,数据写入DR是经过一个显现控制器的内部操作主动写入到DD RAM或CG RAM.一起,DR也用来存储从DD RAM或CG RAM读出的数据。当地址信息写入IR,经过一个内部操作从DD RAM或CG RAM读出数据到DR,此刻的数据传输彻底经过读DR来完结。履行完一个从DR的读操作后,数据保存在DD RAM或CG RAM,下一地址送到DR,为下一个读周期做准备,如表2所示,存放挑选器(RS)信号决议两个存放器中的哪一个被选中。

2.4 忙标志(BF)

当忙标志位是1(即高)时履行一个内部操作而且下一个指令是不能被承受的。

当RS=0而且履行完一个读操作时,忙标志位输出到DB7,下一个指令只要在忙标志位为0(即低)时才可以被写入。

2.5 地址计数器(AC)

地址计数器分配地址给D D R A M或C GRAM,当一个指令的地址写入IR,地址信息从IR送到AC,这个指令一起决议DD RAM或CGRAM的挑选。从DD RAM或CG RAM完结一次读/写操作后,地址计数器(AC)主动减1或许加1,当RS=0而且读操作完结后,AC中的内容输出到DB0DB0~DB7.

2.6 显现数据存储器(DD RAM)

DD RAM用8位字符代码的方式来存储显现数据,容量是80*8或许80字节,DD RAM不用于显现时,可用作通用的数据R A M.

DD RAM地址是用AC来设置而且用16进制表明,这个地址计数器可以经过“Set DD RAMAddress”指令进行写操作,用“Read BusFlag and Address”指令进行读操作。如图3所示,在读/写时,数据位DB0~DB6代表DDRAM地址,DB7为忙标志位。

2.7 字符发生器ROM(CG ROM)

字符发生器ROM(CG ROM)从8位字符代码发生5×7点阵或许5×10点阵字符图形,可以发生等于192种5×7点阵字符图形和32种5×10点阵字符图形。