0 导言

与H.264/AVC比较,新一代视频紧缩规范H.265/HEVC能够在相同的图画质量下完结更低的码率,即更高的紧缩比 。因为人眼的视觉特性,在动态码率编码进程中,不同区域的码率分配是研讨中的一个关键问题。假如能够在编码进程中将视频区分为感兴趣区域(Region of Interest,ROI)和一般区域,动态调整二者的码率分配,则能够在相同乃至更低的码率下得到更好的片面视频质量,然后增强用户体会 。ROI区域的提取速度和质量对编码算法影响很大,因而完结低杂乱度、高质量的ROI区域提取,并针对H.265/HEVC视频编码的本身特色进行码率的分配尤为重要。

将ROI提取及码率分配办法用于JPEG 2000静止图画紧缩,提升了ROI区域的图画质量并取得了较好的码率节约作用,并运用FPGA对ROI的提取进行了VLSI硬件规划,然后在不显着进步图画编码时刻的条件下得到了满意的作用,但该体系只能用于静止图画编码; 均提出了依据ROI的H.265/HEVC码率操控即紧缩功能优化办法,并取得了必定成效。 研讨标明尽管H.265/HEVC编码规范现已在必定程度上较H.264/AVC规范下降了码率,但ROI区域码率操控关于最新的HEVC规范相同起作用,但未考虑ROI提取算法杂乱度对编码速率带来的影响;文献 运用高斯布景模型树立虚拟布景帧,下降了H.265/HEVC编码的码率,但未考虑针对人眼特性的ROI变质量编码,也未考虑布景帧树立功率对编码器速率的影响。

本文依据视频编码算法分块进行的特色和FPGA的细粒度并行特性,提出了依据块匹配的高斯布景建模-ROI映射办法,并运用HLS东西在FPGA渠道进步行了算法的硬件完结与验证。FPGA处理速度到达22 fps@1 080 p,对ROI映射CTU区域进行变质量编码,可得到均匀10%左右的码率节约,视频整体质量保持稳定。

1 高斯布景建模及其面向视频编码的改善

1.1 依据像素的高斯布景建模的根本原理

高斯布景建模是一种依据概率模型的布景建模办法,传统的高斯布景建模算法是以像素为单位的。数字视频中的一帧图画能够看作是关于时空方位(x,y,t)的二维离散函数f(x,y,t),在给定颜色空间的给定通道下,关于给定的(x0,y0,t0),f仅有仅有值;关于给定的时刻t0,f可看成是一个二维随机场,一般以为其为平稳随机场。

从统计学视点来看,远景物体的呈现与运动是暂时的、突发性的,而布景则是长时刻的、具有必定稳定性的,关于时刻t来说,给定(x0,y0),f(x0,y0,t)满意必定的概率散布,一般契合高斯散布。

高斯布景模型的表达式为:

1.2 依据块匹配高斯布景建模-ROI映射算法

由原始高斯布景模型的表达式可知,依据像素的高斯布景建模算法需求进行很多的杂乱浮点核算,一般要经过数百帧才干完结模型的树立,导致算法耗时很高且不合适进行硬件完结。

高斯布景建模办法仅考虑了同一方位像素点的时刻相关性,而且将一切的像素看作是孤立的点,一方面需求进行很多的重复性核算,另一方面在布景发生改变时,会发生“虚警”现象。

视频序列中存在空间冗余、时刻冗余和常识冗余等。针对一帧图画空间上的冗余,视频编码算法中选用分块办法进行帧内猜测,对猜测值与原始值的残差进行改换编码和量化编码,到达视频紧缩的意图。

本文运用块匹配办法替代原高斯布景建模的像素匹配和更新办法,提出依据块匹配的高斯布景建模-ROI提取算法。一方面,依据块进行布景建模核算能够避免依据像素算法进程中的很多运算;另一方面,依据块进行高斯布景建模能够将布景树立与视频编码块的区分一致起来。

运用高斯建模树立布景后,将新的视频帧分块,依据SAD判别原则进行远景块与布景块的断定,SAD判别的表达式如式(5)所示。其间B表明现已树立好的布景块,C表明当时视频帧对应方位的像素块,本文中N取8。

其根本进程描绘如下:

进程1:视频块区分。按N&TImes;N规范将原始视频区分红若干个不相交的子区域。

进程2:模型初始化。针对分块区域,初始化高斯模型的根本参数μ、σ、λ、α。

进程3:帧计数断定。读入视频,若视频帧数满意更新周期p,则进入进程4,不然进入进程5。

进程4:模型更新。更新分块布景模型。

进程5:前布景断定。依据SAD判别原则,区分远景与布景。

进程6:ROI区域映射。依据远景块散布,对视频中的CTU进行映射。本文中设定HEVC CTU规范为32&TImes;32,映射成果将送入H.265/HEVC编码器。

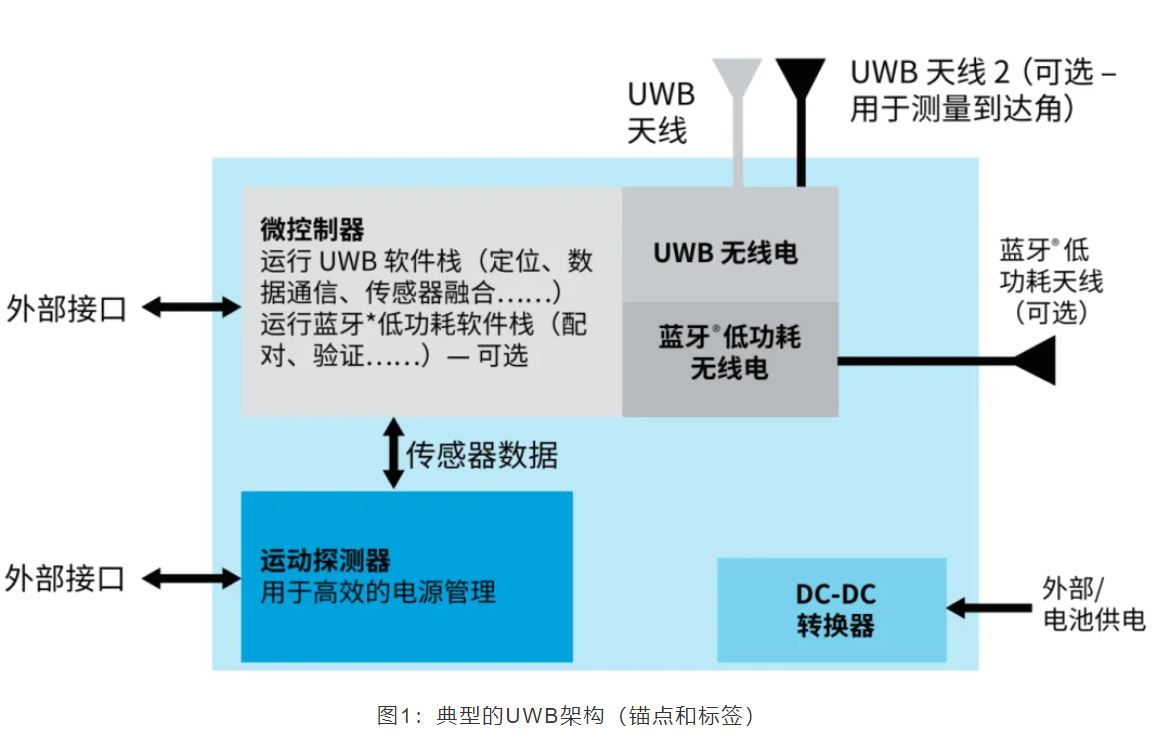

算法流程如图1所示。

2 依据率失真优化的ROI区域自适应编码

2.1 面向ROI区域的率失真优化

为了下降码率一起到达较好的图画质量,率失真优化能够界说为如下优化问题:在码率R≤Rmax时,经过调整编码算法使得失真D最小,即:

式(8)一般被用作RDO的依据,但事实上往往编码块之间不彼此独立,然后导致求得的值为部分最优解。

本文经过ROI区域的区分,假设在一帧中ROI区域与非ROI区域独立同散布,则率失真优化函数可描绘为:

因为式(9)考虑到了编码块的相关性问题,能够在必定程度上避免堕入部分最优,剖析可知,式(9)将比式(8)得到更优解。

进一步地,从片面视频质量动身,人眼希望ROI区域能够有更好的视频质量,因而,本文在完结进程中参加约束条件:

2.2 集成ROI提取的HEVC编码

本文将ROI区域送入HEVC编码器中进行变质量编码。为了避免ROI区域与周围非ROI区域的编码参数差异过大形成显着的方块效应,本文运用非线性补偿对量化参数进行了调整,具体做法如下。

记ROI区域地点的编码块A的量化参数为q1,在其邻近的非ROI区域中编码块B的量化参数为q2,A的中心点坐标记作(xA,yA),B的中心点坐标记作(xB,yB),则q1、q2以及A、B中心方位的汉明间隔D应满意如下联系:

3 硬件规划与完结

为了阐明本文办法的有效性,将依据块匹配的高斯布景建模-ROI算法进行了硬件完结并嵌入到HEVC编码的进程之中。

本文运用高层次归纳(High Level Synthesis,HLS)东西,依据Xilinx MPSoC渠道ZCU102进行了依据布景建模的ROI区域映射与自适应编码的硬件规划。HLS东西能够将C/C++言语的高层次描绘映射为硬件描绘言语(VHDL或Verilog),进步开发功率。

硬件包含3个模块,别离为:布景树立、布景更新、ROI断定与映射,最终将映射成果送入视频编码器。其根本结构如图2所示。

原始视频数据缓存在DDR中,在FPGA内部经过行缓存加速存取速率,视频数据多路选择器在帧计数器的操控下,将视频送入不同的处理单元,将ROI区域映射到H.265规范中的编码树单元(CTU),映射成果送入H.265编码器。在编码器中,依据区域性质进行ROI自适应的QP调整,最终将编码后生成的码流写回DDR。

4 试验成果与剖析

4.1 试验环境

本文依据Xilinx ZCU102嵌入式开发渠道进行了试验。ZCU102搭载了Zynq UltraScale XCZU9EG-2FFVB1156 FPGA芯片。该芯片内部架构首要包含处理器体系(Processing System,PS)和可编程逻辑(Programmable Logic,PL)两部分。

其间PL端硬件资源耗费状况如表1所示。考虑到必定的伸缩性,硬件规划中图画的分辨率能够进行装备,最高分辨率为1 920&TImes;1 080。

4.2 布景建模作用与ROI映射成果

图3为依据FPGA的布景建模和ROI映射成果。所用序列为HEVC规范测验序列BasketballDrill_832&TImes;480_50.yuv。图3(a)为视频序列的第201帧,图3(b)为运用前200帧建模得到的布景帧,图3(c)为针对HEVC CTU的映射成果,其间白色区域为映射得到的ROI区域。能够看出视频中运动的人物被精确映射到以CTU巨细为鸿沟的区域中。调查原始视频序列可知,原始视频序列中的布景区域随时刻改变有改变(如篮筐会随篮球碰击而颤动等),但这些改变并未对ROI区域的映射形成影响(即未呈现“虚警”现象),算法具有必定的鲁棒性。

表2为不同分辨率下进行处理的速度比照,PL部分的时钟频率为120 MHz。由表可知本文规划在1 920×1 080的分辨率下仍可到达较高的实时性。

4.3 嵌入ROI码率操控的HEVC视频编码功能评价

为了进一步阐明嵌入ROI区域后HEVC编码的有效性,本文对HEVC编码器的编码成果进行了试验验证。别离选取不同分辨率和不同场景下的测验序列,核算整体码率及PSNR的改变状况,成果如表3所示。

从表3能够看出,选用本文提出的布景建模-ROI映射算法进行码率操控,编码后图画整体的PSNR没有较大改变,可是码率有了均匀10%左右的节约,然后验证了本文算法在对码率操控的有效性。

5 定论

依据视频编码算法分块进行的特色,本文提出一种依据块的高斯布景建模-ROI映射办法,经过HLS办法在FPGA上完结,并用于H.265/HEVC视频编码。试验成果标明,在FPGA渠道上该算法运转速度较快,能够有效地集成到H.265/HEVC硬件编码器中;在H.265/HEVC中对提取ROI区域进行变质量编码,可得到均匀约10%的码率节约,整体的视频质量保持稳定。