一、LPC32×0通用描绘

恩智浦公司的90nm工艺ARM926EJ-S核(包含矢量浮点联合处理器),以及很多的规范片上外围.CPU频率最高到达266Mhz。

ARM926EJ-S核采用了哈佛结构,5级流水线还有一个集成存储办理单元MMU。MMU支撑现代操作体系需求的虚拟存储技能。

LPC32X0包含了256KB的片上静态RAM,NAND FLASH接口,以太网MAC,LCD操控器(支撑STN,TFT),还有一个扩展的总线接口,支撑SDR和DDR SDRAM。别的还有一个USB2.0接口,7个UART,2个I2C总线接口,2个SPI/SSP接口,2个I2S接口,2个单输出PWM,一个电机操控PWM,6个通用定时器(具有输入捕获和比较输出功用),一个安全数字(SD)接口,一个10比特ADC(与触摸屏共用)。

二、主要特点

1. ARM926EJS 处理器,CPU时钟做高可达266MHZ

2. 向量浮点联合处理器(VFP)

3. 32KB指令高速缓存,32KB数据缓存

4. 可选择从不同的外围设备发动:NAND Flash, SPI memory,USB,UART,或许静态存储器。

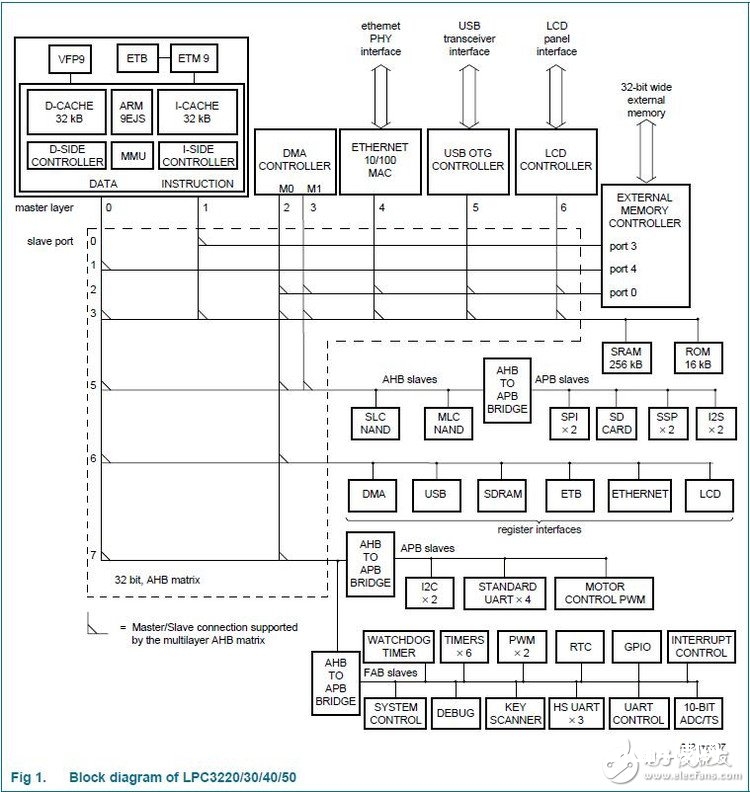

5. 多层AHB体系为每个AHB主机供给独自的总线,包含CPU的指令、数据总线,DMA操控器的两个数据总线,USB操控器总线,LCD操控器总线,以太网MAC操控器总线。除非两个主机企图一起拜访同一个从设备,那么就不存在总裁延时。

6. 2个NAND FLASH操控器:一个用于单级NAND FLASH设备,一个用于多级NAND FLASH 设备。

7. 主机中止操控器(MIC)以及两个从设备中止操控器(SIC),支撑74个中止源。

8. 8通道通用DMA(GPDMA)操控器,用于SD卡接口,高速UART,I2S接口,SPI接口,以及存储器之间的传输。

9.串行接口:

a)10/100 以太网 MAC,带有专用的DMA操控器。

b)USB接口,支撑8个设备,主机,OTG(专用的PLL用于发生要求的48MHZ USB 时钟)

c)7个高速UART,都支撑64B的FIFO

d)2个SPI,2个SSP,2个I2C,2个I2S。

10. 其他外围

a)LCD操控器,带有专用的DMA,支撑1024X768显现分辨率

b)保密数字存储卡接口(SD)

c)GPIO

d)10比特,400KHZ,ADC.

e)实时时钟(RTC),独立的供电引脚以及32KHZ振荡器。

f)32比特,通用高速定时器。

11. 规范ARM测验/调试接口

三、结构图

四、功用概述

1. VFP

VFP供给单精度、双精度的加减乘除以及乘加运算。

2. EmulaTIon & debugging

LPC32X0支撑经过专用的JTAG串行接口进行在线调试和评价,一个嵌入式的盯梢缓冲器能够盯梢程序的履行进程。

3. 嵌入式ICE

规范的ARM EmbeddedICE 逻辑支撑在片调试。方针体系的调试要求一个主机运转在调试软件而且要求一个嵌入式ICE 协议转换器。嵌入式ICE 协议转换器将远端调试协议指令转换成拜访ARM核的JTAG数据。

4. ARM核有一个调试通道(DCC), Debug CommunicaTIon Channel。主机Debugger经过 DCC和运转程序进行通讯,而不打断程序的运转或让程序进入调试状况。

5.

6. AHB 阵列

AHB用于内部块间的通讯。AHB是ARM界说的高速总线,是ARM总线结构的一部分。AHB是高带宽低延时总线,支撑多主机裁定和总线授权/恳求机制。

多层AHB为7个AHB主机别离装备了独自的AHB总线:

.CPU 数据总线

.CPU指令总线

.通用DMA主机0

.通用DMA主机1

.以太网操控器

.USB操控器

.LCD操控器

7.APB 是外围设备与AHB之间的桥梁

8. FAB :是衔接某些特别的外围的桥,一个AHB时钟进行读操作,2个AHB时钟用于写操作。

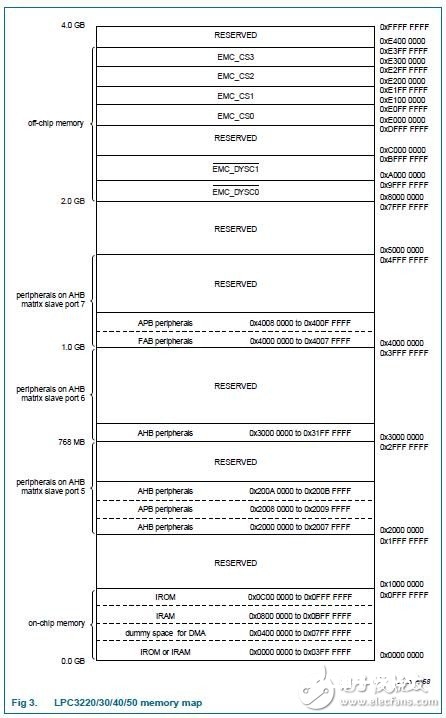

9.物理地址分配

10、 片上ROM

16KB的ROM包含上电引导程序,决议从以下四个接口中引导进程序: UART5,SSP0(SPI形式),EMC的CS0或许NAND FLASH.

上电完结今后,程序总是从ROM开端履行。bootstrap软件首要读取SERVICE输入(GPI_1),假如SERVEICE为低,那么从UART5下载程序到IRAM而且开端履行下载的代码。假如SERVICE为高,那么Bootstrap跳到惯例引导。首要查看SPI存储器,看是否存在引导信息,假如存在SPI存储器,而且有引导信息,那么下载里面的代码并开端履行。假如SPI不存在或许不存在引导信息,那么开端查看EMC 的CS0空间,最终查看NAND Flash空间。

11. 动态Memory空间:

DYCS0: 0X8000 0000~0X9FFF FFFF

DYCS1: 0XA000 0000~0XBFFF FFFF

静态Memory空间:

CS0: 0XE000 0000~0XE0FF FFFF

CS1: 0XE100 0000~0XE1FF FFFF

CS2: 0XE200 0000~0XE2FF FFFF

CS3: 0XE300 0000~0XE3FF FFFF

12. AHB主机外围

LPC32x0完成4个AHB主机外围,包含GPDMA,MAC,USB以及LCD操控器。

13. GPDMA操控器

GPDMA完成外围到存储器、存储器到外围、外围到外围、存储器到存储器的数据传输。

14. 体系功用

…..To be conTInued.