在操作系统中,有一种重要的进程间的同步机制称作信号量机制。信号量即当时可用资源的计数。信号量是一个用来完结同步的整型或记载型(Record)变量,除了初始化外,对它只能履行等候和开释这两种原子操作。一次对信号量的等候操作是取得信号量的进程,读取当时信号量的值,假如发现有可利用资源,则将信号量减1,不然进入等候状况。一次对信号量的开释进程行将信号量加1。一个进程对信号的读取、核算新的信号量值、更新信号量的值这三个进程是不允许被其他进程打破的,假如被打破,则信号量的值将会产生过错,RMW操作的最大用处在于信号量操作。

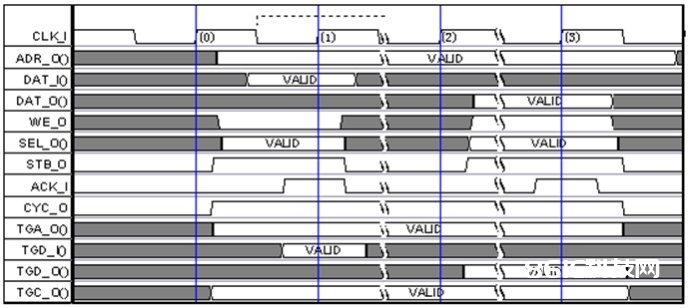

一次RMW操作关于总线来说,本质上是两次子操作,一次读,一次写,只不过这两次子操作必须由同一个主设备的完结,且读数据和写数据的地址相同。”改”是不产生在总线上的,它产生在主设备内部。一个RMW操作的比如如图13所示,其进程如下:

在时钟上升沿0,主设备将地址信号ADR_O()、TGA_O()放到总线上,将WE_O置为低表明读操作,将恰当的SEL_O()信号置高告诉从设备将数据放在数据总线的恰当方位,将CYC_O和TGC_O()置高表明操作正在进行,将STB_O置高表明榜首次子操作开端。CYC_O和TGC_O()能够产生在上升沿0曾经的任何时刻。

在时钟上升沿1抵达之前,从设备检测到主设备建议的操作,将恰当的数据放到主设备的DAT_I()和TGD_I(),将主设备的ACK_I置高作为对主设备STB_O的呼应。

在时钟上升沿1,主设备发现ACK_I信号为高,将DAT_I()和TGD_I()采样,完结榜首次子操作。主设备将STB_O置低表明刺进等候。

在时钟上升沿1之后新的上升沿抵达之前,从设备检测到主设备将STB_O置低,所以将ACK_I置低。

通过若干等候周期,在上升沿2,主设备将地址信号ADR_O()、TGA_O()放到总线上,将数据信号DAT_O()、TGD_O()放到总线上,将WE_O置为高表明写操作,将恰当的SEL_O()信号置高告诉从设备将数据总线上哪些信号是有用的,将STB_O置高表明第二次子操作开端。

在时钟上升沿3抵达之前,从设备检测到主设备建议的操作,将主设备的ACK_I置高作为对主设备STB_O的呼应。

在时钟上升沿3,从设备将DAT_I()和TGD_I()采样;主设备发现ACK_I信号为高,得知第二次子操作完结,所以将STB_O和CYC_O置低表明整个RMW操作完结。

在时钟上升沿之后,从设备发现STB_O为低,所以将ACK_I置低。

图 Wishbone总线的RMW操作