驱动工业物联网 (IIoT) 的“恣意衔接”完结了超高速增加,这不只仅只是衔接许多截然不同的设备。这还与跨各种广泛运用搜集、剖析和操作的数据有关。IIoT 概念的要害点在于能够保证设备的安全性,以便能够搜集和同化数据并向其他方位进行传输。

“恣意衔接”这一理念的超高速增加所引发的新缝隙远远快于公司能够施行的安全办法。一般最简单被疏忽的缝隙之一便是资源受约束的硬件渠道,例如,2010 年进犯伊朗核反应堆的震网 (Stuxnet) 病毒就引发了全球范围内的重视。

PFP Cybersecurity 是一家科技公司,其拟定的共同办法能处理许多安全性问题,例如因资源受约束的硬件渠道和网络安全要挟(如震网等病毒)的增加所导致的问题。iVeia 经过充分运用 赛灵思’s Zynq-7000 All Programmable SoC 来协助 PFP Cybersecurity 面向 IIoT 运用施行新颖、高效的算法型网络安全处理计划。与 PFP 的依据 PC 的概念验证比较终究规划在体积和功耗方面均削减或下降了一个数量级。

在讨论咱们两家公司如安在 Zynq SoC 上运用名为 Power Fingerprinting (PFP) 的专有技能来开发和商用化某个 IIoT 网络安全处理计划之前,咱们首先来深化了解一下资源受限硬件渠道不断增加的安全缝隙。

资源受限型硬件渠道的缝隙

因为规范工业操控设备运用资源受约束的嵌入式渠道,因而操控要害根底设施的许多体系简直没有网络安全性规则。现在,这种体系等级缝隙正被以为是要害根底设施的严重要挟。在要害根底设施环境中,许多体系具有陈腐的处理器,运用仅有硬件,而且不支撑典型网络安全办法所引进的功用降级,它们为侵略留下了后门。最近的一次是在 2014 年 11 月,查询人员发现操控美国电厂、电网、水处理工厂和石油天然气根底设施的体系感染了病毒。[1]

四年前,因为震网病毒感染了伊朗担任运转核离心机的可编程逻辑操控器 (PLC),然后导致了离心机的破坏。[2] 渠道过于死板,就十分简单遭到侵略, PLC 便是其间的模范。PLC 很大程度上由嵌入式 MPU 组成,能主动对工业设备进行操控和监控。企业一般会树立其 PLC 渠道网络,但却趋向于不为任何类型的安全监控或完整性评价供给资源。[3] 一起为了防备零日进犯(zero-day attack)或供货商未意识到的安全缝隙,他们也不会特别频频地去更新这些渠道。[4]

POWER FINGERPRINTING:一种新颖且有用的安全办法

PFP Cybersecurity 开端寻求能处理这类问题的处理计划,其不只是能与现有装置设备高效协作运转的非侵入式处理计划,一起也不需求装置任何重要的设备或发生许多软件更新。。该公司开发的 PFP 技能可作为完整性评价的立异办法。正如人类指纹是个人的仅有标识相同,相同的理念也适用于特定体系或芯片。PFP 运用物理侧通道(例如,功耗)来获取在处理器中全面履行协议栈内部履行状况的相关信息,而且这与渠道或运用无关。PFP 技能将辨认被体系以为正常运转的“指纹”。假如之后获取的某个指纹不匹配,则或许标明某些方面犯错。

这可经过外部监控器来完结,该监控器在物理上与方针处理器别离,而且在网络进犯破坏了方针时能以极高的准确度进行检测。PFP 一起适用于新体系和原有体系,是现有网络安全性处理计划的弥补,而且不需求在方针上装置任何软件或硬件。

PFP 可支撑能捕获通道侧信号的各种传感器,并依靠于核算密集型信号处理算法进行功用抽取,而且依靠机器学习进行分类。能经过各种办法来完结感应侧通道,包括 AC 或 DC 电流或许在方针周围获取电场或磁场改变的电磁 (EM) 传感器。PFP 从捕获的信号中抽取仅有有不同特征,将其与一组基线参阅进行比较并查找误差。基线参阅是“指纹”,可仅有辨认的正常履行方针软件,而且是经过机器学习办法来抽取的。PFP 运用存储的参阅来实时检测未经授权的履行误差。

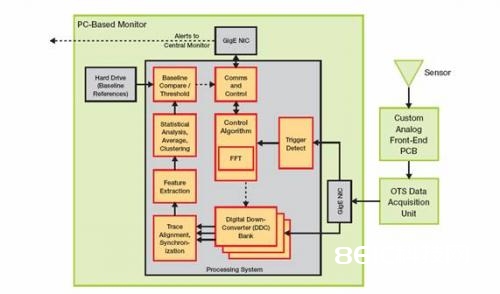

PFP Cybersecurity 成功开发了概念验证用的监控体系,并运用如下设备对该体系进行了演示:个人核算机 (PC) 、 具有高速模数转化器 (ADC)以及能将 EM 传感器与数据搜集设备(如图 1 中所示)完结接口相连的定制模仿前端。PFP 算法引擎在 PC 上履行,并以从数据搜集设备搜集原始 ADC 数据为切入点。体系的前端处理在规划方面类似于许多多通道数字无线电接收器,即,在 ADC处搜集可用于由多个数字调谐器进行处理(一般称为数字下变频,也可简称 DDC)的宽波段。这些 DDC 可调谐到更广波段中的更窄相关波段,然后对这些波段进行过滤和抽取。此办法能发生高得多的可办理数据带宽以进行后续盯梢处理,并可极大简化体系规划的模仿部分。

功用抽取和分类算法可处理 DDC 的输出,并将其与一组基线参阅进行比较,一切这些都有必要进行实时操作才干保证它们察觉到任何侵略。操控算法的并行运转能够确认ADC 采样率及相关波段的处理参数。此进程可在原始 ADC 样本的大型相邻模块上履行许多操作,其间包括快速傅里叶变换 (FFT)。 此办法可依据方针渠道供给接连的 24/7 全天候完整性监控。 假如检测到侵略,FPP 监督器就会经过提示操作人员、将事情数据记录到中心监控站和/或采纳活跃办法来依据特定于运用的战略进行呼应。

依据 PC 的概念验证体系能够发生的超卓的成果,但因为多种原因,无法作为能够在商业上广泛布置可行体系。PC 体系根本包括一个监督器节点,而每一个实际国际的装置都或许需求几百个监督器节点。对算法功用的要求标明 PC 需求具有功用强大的高端处理器。因而,其一般将需求电扇散热、相对大型的机柜以及大功率电源。

为了最大极限下降体系的抗扰性,传感器信号的模数转化应在接近方针的一端进行。方针处理器邻近恰当的物理空间和电源可用性因各个装置的不同而有所差异,而且关于大部分装置而言,PC 的巨细与电源要求过于大型,而无法行得通。虽然 PC 的本钱或许较低,但将其他组件与 PC 进行集成所带来的本钱和杂乱性反而会让导致难以承受的昂扬本钱。更不用说, PC 会使得监督节点本身更简单遭到网络的进犯。

从架构方面而言,一种挑选或许是将一切原始数字信息经过规范网络传输到中心处理器或服务器。 但因为 ADC 极高的采样率,支撑如此许多数据所需求的网络根底设施在装置时或许会不可用,而且购买和装置不只杂乱而且本钱过高。

因而,分布式核算架构是最抱负的挑选,因为每个传感器都具有一个核算节点。 此外,分布式架构还能在同一单元中将传感器模仿前端和算法处理高度整合在一起,然后下降本钱和杂乱性。此外,关于大部分装置来说,现有的网络根底设施足以支撑现在被以为是超低的数据速率。可是,在选用分布式处理处理的状况下,监控器节点的规划就变得更具挑战性,因为其本身有必要满意传感器节点和监控器算法处理的归纳要求。

因而监控器节点有必要体积小、功耗低、本钱低。其有必要能够处理弛缓冲来自于高速 ADC 的数据,而且还能够满意算法的核算需求。此单元有必要满意小才干紧靠方针器材放置,然后不只能约束线缆长度,而且还可进步传感器的抗扰度。巨细和潜在的装置空间约束确认该单元可在无电扇的状况下运转;因而有必要规划为低功耗。

因为在需求监控的既定装置中或许稀有百个方针器材,因而该单元的本钱有必要十分低才干坚持较低的整体装置本钱低价。许多嵌入式处理器都能够满意上述大部分条件,例如部分依据盛行的 ARM® 架构的嵌入式处理器。除了大部分由 ARM 器材完结的低功耗和低本钱之外,ARM 产品还具有更多优势,例如对大型社区的支撑、嵌入式操作体系和开发工具的可用性以及针对大部分器材的原生千兆以太网支撑。

其间简直一切器材都短缺处理原始 ADC 数据的才干(速率高达 8 Gbps)。它们也不具有对该数据进行任何有意义操作的数字信号处理 (DSP) 功用。

充分运用 ZYNQ SOC 以完结 FFP CYBERSECURITY

这些更严厉的要求使得 Zynq SoC 抱负适用于该运用。Zynq SoC 可在单个全功用器材中将双核 ARM 处理体系与高功用可编程逻辑高度整合在一起。这种组合不光可供给能满意运用的处理需求的异构核算架构,一起还能简化依据 PC 体系的代码移植作业。

Zynq SoC 的处理体系能供给上述嵌入式 ARM 处理器的一切优势,而增加的可编程逻辑也具有若干优势。它们包括与 ADC 的无缝衔接,而且还能够处理 ADC 的全数据速率。此外,Zynq SoC 在可编程逻辑结构中包括几百个 DSP 模块和几万个逻辑模块,能够运用它们对检测和练习算法完结显着加快。Zynq SoC 还可全方位满意针对低功耗、低本钱和小尺度的要求。

经过选用 28 纳米可编程逻辑结构和 ARM 处理体系,器材可完结相对较低的功耗。因为 Zynq SoC 具有极高的集成度,因而无需选用之前原本所必需的许多支撑电路和外设,这不只能缩小整体体系规划,一起还可下降本钱。此外,为了下降危险并加快上市进程,抱负的状况是在规划中增加依据 Zynq SoC 的小型模块级体系 (SoM)。

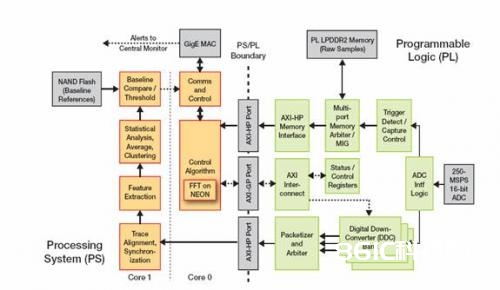

iVeia 公司推出的 Atlas-I-Z7e 抱负适用于嵌入式监控器规划,因为其具有如下优势:极高的功用功耗比(归功于低功耗 Zynq 7020 器材和 LPDDR2 内存);专用的可编程逻辑内存在无需处理器干涉的状况下对 ADC 数据进行缓冲;以及能在工业环境中牢靠运转。Atlas 高度灵敏的无缝接口可简化根底板规划。此外,SoM 开发套件还包括具有参阅规划的免版权信号处理 IP 资源库,其不只能供给监控器运用代码的首要部分,而且还能快速提高规划功用。图 2 描绘了的依据 Zynq SoC 的终究监控器规划。

怎么履行核算密集型体系功用

一旦选定硬件,现在的重点将改变成为爸代码从依据 PC 的规划移植到依据 Zynq SoC 的嵌入式渠道。因为对 PC 的核算负载具有重要意义,因而有必要将 Zynq SoC 的可编程逻辑部分有必要用于加快代码而且不能仅充任无缝逻辑。一种或许的办法是将 PC 代码移植到 ARM 处理器,对代码进行概要剖析以确认核算瓶颈拟定计划以将软件分组为要在可编程逻辑中加快的代码(比照于 ARM 处理器上运转的代码)。可是,在偏重加快上市进程的状况下,咱们的开始办法是经过将这些具有等效、随时可用的 IP 核(而且已知为核算密集型)功用搬运到可编程逻辑中,然后对规划进行分组。接下来,咱们重构并移植了 PC 代码,然后对其他代码进行概要剖析以确认是否还需求任何其他加快。图 3 对此计划进行了阐明。

毋庸置疑,DDC 是可编程逻辑完结办法的抱负之选,因为 DDC 内核被纳为 SoM 开发套件的一部分 ,而且 DDC 组的兼并核算要求可超越 20 gigaflop。DDC 组是侵略检测算法的一部分,其有必要实时运转才干防止失去侵略事情。DDC 组的抽取输出可传递到 ARM 处理器,以便在软件中进一步处理侵略算法。虽然输出速率可达 2 Gbps,但却能被高功用 AXI 端口轻松处理,这些端口可将 Zynq SoC 的可编程逻辑衔接到 ARM 内存。

经过运用运用编程接口的通用型 AXI 总线从 ARM 处理器对 DDC 内核进行装备。API 答应在 ARM 上运转的软件动态更改 DDC 参数,以便中心频率、带宽和抽取速率方面的更新能够依据操控算法指令实时进行。

因为经过搬运 DDC 负载而显着下降数据速率,因而以 766 MHz 频率运转的两个 ARM 中心处理单元 (CPU) 具有满意的功用来支撑后续处理进程。因为该规划在对称多处理 (SMP) 形式中选用 Linux 操作体系,因而能别离两个 ARM CPU 内核之间的处理,一个处理侵略检测,而另一个处理操控算法以及可与中心监控站的通讯接口。此外,Linux 还具有稳健牢靠的网络支撑和安全性,可答应进行长途网络办理(这正是大部分装置所必需的),一起禁用任安在不久的将来或许会呈现缝隙的不用要特性。

操控处理需求原始 ADC 样本的大型相邻模块。一个需注意事项是将原始 ADC 样本经过高功用 AXI 端口从 ADC 接口逻辑直接串流到 ARM 内存。可是,为了保存处理器体系的内存带宽以用于处理算法,咱们反而挑选了将 ADC 数据缓冲在可编程逻辑专用的物理内存中。这种内存具有确认性的带宽并保证相邻 ADC 样本的许多调集,而不会搅扰 ARM CPU 的操作。

可将从专用可编程逻辑内存中搜集的数据经过其间一个高功用 AXI 端口传输到 ARM,以坚持低推迟并最大极限下降 ARM CPU 的开支。咱们运用多端口内存裁定器供给了一个搜集端口和一个检索端口。这种办法可供给在搜集样本的一起并发检索样本所需的裁定,然后进一步削减推迟。

在对新分区的规划进行剖析时,操控算法不会满意频频地运转来充分地坚持检测精度。功用瓶颈在很大程度上归因于 16,000 点 FFT 运算。凭借赛灵思的 Vivado Design Suite 供给的 FFT IP 核,FFT 的功用将远远满意,因为其规划为实时运转。可是,对可编程逻辑的其他资源需求将强制规划运用更大的 Zynq 7030 器材。

走运的是,来自 Project Ne10 的开源 Ne10 库供给了专为 ARM 的 NEON 架构扩展优化的 FFT 功用,这加快了通用浮点和固定点数学运算。虽然来自 Ne10 库的 FFT 功用不会像赛灵思 IP 核那样实时运转,但其可充分地加快操控算法以坚持检测精度。

终究的依据 Zynq SoC 的监控规划渠道可与依据 PC 的原型相媲美,有时乃至技高一筹。而且,终究的规划比依据 PC 的规划制作本钱显着下降,而且消除了 PC 规划存在的尺度大、功耗高这两大商场壁垒。相对来说,Zynq SoC 规划在尺度和功耗方面简直下降了一个数量级。

PFP Cybersecurity 开发了 Power Fingerprinting 技能来处理在要害设备中检测因为工业物联网趋势而暴增的网络进犯的杂乱问题。凭借业经验证的技能,呈现了怎么规划体系以完结技能并一起满意商场需求的问题。凭借 Zynq SoC,PFP 技能可在杂乱且核算强度大的处理才干需求与低本钱、小尺度、低功耗的商场需求之间获得最佳平衡,然后在商业上具有可行性。

图 1 – 依据PC的监控体系中的模块包括前端模仿、数据搜集和处理体系功用。

图 2 – 依据Zynq SoC的监控体系是经过iVeia的Atlas-I-Z7e体系级模块构建的。

图 3 – 该图表显现了Zynq SoC的PS和PL模块(包括数据流)的功用分区。