摘要 介绍了DDR3 SDRAM的技能特色、作业原理,以及操控器的构成。使用Xilinx公司的MIG软件东西在Virtex-6系列FPGA芯片上,完结了操控器的规划办法,并给出了ISim仿真验证成果,验证了该规划计划的可行性。

DDR3 SDRAM是第三代双倍数据速率动态同步随机存储器的简称。是SDRAM内存产品宗族中的一员。DDR3内存模组是选用多颗DDR3 SDRAM,并依据JEDEC的相关内存模组规划标准而制造。DDR3SDRAM有如下技能特色:(1)DDR3新增了重置(RESET)功用,并为此新功用设置了管脚,当RESET指令有用时,DDR3将停止一切操作,此刻处于活动量最少的状况,以降低功耗。(2)DDR3新增ZQ校准功用,ZQ也是一个新的管脚,这个引脚经过一个指令集及片上校准引擎(On—Die Calihration Engine,ODCE)主动校验数据输出驱动器导通电阻与ODT的完结电阻值。(3)在DDR3体系中,将参阅电压分红两个:一个是为地址和操控总线供给服务的VREFC,另一个是为数据总线供给服务的VREFDQ,两个不同的参阅电压为DDR3供给更好的抗噪才干。(4)在DDR3体系中,操控器和存储器是一一对应的,由此便可大幅减轻地址、操控、数据信号的总线担负,供给了信号的完整性。这是DDR3和DDR2的一个要害差异。对单个Rank的模组,操控器和内存是点对点(Point to Point)的衔接联系,对双Rank的模组,操控器和内存是点对双点(Point to 2Points)的衔接联系。(5)DDR3存储器模块的地址、指令、操控信号和时钟选用了“Fly—by”的拓扑结构,大幅减轻了地址、指令、操控和数据总线的负载,进步了信号的完整性。

1 DDR3 SDRAM作业原理

体系上电后,在DDR3 SDRAM进行正常读写操作前,有必要依照规则过程完结初始化操作,然后才干进入闲暇的状况,等候操控器的拜访。初始化操作过程中首要完结对形式寄存器的装备作业,DDR3芯片上有4个形式寄存器,经过形式寄存器的装备,可完结比方突发长度、读取突发品种、CAS长度、测验形式、DLL复位、输出驱动才干等的设置。

DDR3 SDRAM的作业状况转化是经过指令来完结的,首要经过CS#(片选信号)、RAS#(行选通信号)、CAS#(列选通信号)、WE#(读写操控信号)之间的组合状况完结,DDR3 SDRAM支撑的指令首要有:

(1)预充电指令。作用是封闭特定Bank中翻开的行或许一切Bank中翻开的行,SDRAM寻址具有较强的独占性。关于第一次的读写,只需用激活指令翻开此行即可,而关于当时行仍处于翻开状况,要对新一行进行读写,此刻就要封闭当时行,此指令便是预充电指令。

(2)改写指令。SDRAM单元有个缺陷便是用电容存储数据。但由于漏电流的存在,数据不能长期存在存储单元中,需求周期性的改写来坚持数据,所以在SDRAM进行存储作业时,有必要进行改写操作。改写距离和存储芯片的温度有关,改写办法分为自改写(SREF)和主动改写(AREF)。自改写用于正常形式下,而主动改写用于低功耗情况下。

(3)激活指令。用于激活所要进行读或许写操作的Bank、行和列。在读或许写指令抵达DDR3 SDRAM的行之前,要先对要读或写操作的行用激活指令进行激活。与激活指令一同发送的地址位用于寻觅进行操作的Bank和行,与读或写指令一同发送的地址位用于寻觅进行操作的开端列单元。

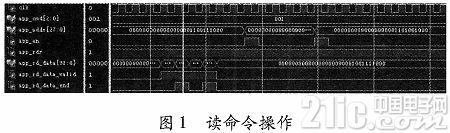

(4)读指令。用于对一个已激活的行进行读操作。在读操作完结之后,被拜访的行仍然处于翻开状况,直到被预充电指令封闭。BA0~BA2用来挑选Bank的地址,A0~Ai供给的输入地址用于挑选开端列地址,读指令操作如图1所示。

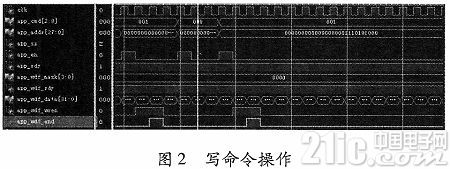

(5)写指令。用于发动一个突发的存储器写操作,由FPGA向DDR3 SDRAM中写入数据。BA0~BA2用于挑选Bank的地址,A0~Ai供给的输入地址用于挑选开端列地址由FPGA将数据写入DDR3 SDRAM中。写指令操作如图2所示。

DDR3芯片内部操控器中有8个Bank处于敞开的状况,Bank敞开的次序由操控器宣布的指令决议。若8个Bank均处于敞开状况,但还有数据要进入Bank,则最终敞开的Bank将被封闭,以翻开一个新的Bank。在自改写时,一切Bank都会被封闭,一旦有预充电指令,Bank就会敞开。

2 DDR3 SDRAM操控器规划计划

规划选用Xilinx公司供给的DDR3 SDRAM操控器IP核。选用此计划的优点是缩短开发周期、简化体系规划。规划者只需在Xilinx公司供给的MIG3.92软件东西界面上挑选FPGA及DDR3 SDRAM芯片类型、总线宽度、速度等级,设置突发长度、CAS推迟、引脚分配等参数,即可生成DDR3 SDRAM操控器。FPGA芯片选用Xilinx公司的Virtex-6系列XC6VLX240T-1FFG1759C类型,DDR3 SDRAM芯片选用镁光公司的MT8JSF25664HZ-1C4D1,该内存芯片行地址宽度为15位。列地址宽度为10位,Bank地址位宽为3位,总容量为2 GB。设置突发长度为8位,数据宽度为64位,速度等级为-2,时钟频率为400 MHz。

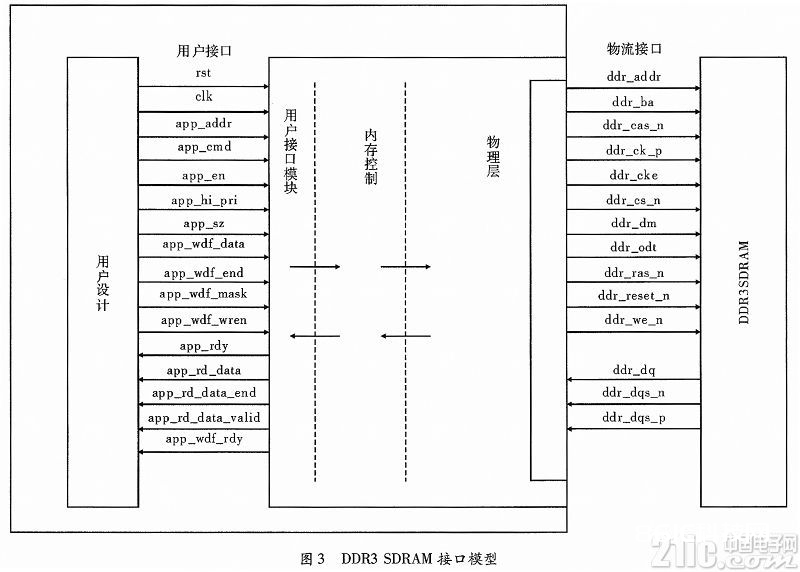

DDR3 SDRAM操控器的首要功用是完结对DDR3SDRAM的初始化,将DDR3 SDRAM杂乱的读写时序转化成用户简略的读写时序,将DDR3 SDRAM接口的双时钟数据转化成用户的单时钟数据,并发送周期性的改写指令来保持DDR3 SDRAM中的数据。操控器首要分为传输层和物理层,传输层担任接纳上层用户逻辑的访存恳求,并将这些恳求转化成DDR3SDRAM所需的时序发送给物理层。物理层担任将操控和地址信号依照DDR3 SDRAM需求的时序发送给存储芯片,一起在传输层和存储芯片之间创立地址通路和数据通路,捕获DDR3 SDRAM宣布的数据,经过输入输出缓存发送DDR3 SDRAM一切的操控信号、地址信号以及数据信号,一起确保指令与地址,数据的同步,DDR3 SDRAM接口模型如图3所示。

DDR3 SDRAM内存操控器的规划有必要满意两大基本要求:(1)所规划的操控器要完结对内存模组的办理,完结CPU的访存要求。(2)需尽可能进步拜访内存的速度和带宽,这是衡量内存操控器功用的重要目标,一起还需考虑内存的兼容性和本钱问题。

3 试验成果

为验证DDR3操控器IP核的正确性,对MIG生成的测验模块在ISE14.2环境下进行功用仿真验证,该模块可以对DDR3存储器进行一系列操作,并对写入和读出的数据进行比较,然后验证操控器的正确性。仿真成果如图4所示,phy_init_done的值为1,阐明初始化完结。当app_cmd=000时,表明当时进行写操作,只要一起app_en=1和app_rdy=1,app_ addr才干写入成功。当app_cmd=001时,表明当时操作为读操作,可经过rror这一比较信号验证操控器是否正确。从仿真成果可看出,比较信号error一直为低电平,阐明写入和读出的数据是共同的。

4 结束语

经过对DDR3的技能特色和作业原理进行剖析,将DDR3操控器的从层次上分为传输层和物理层,然后给出了DDR3 SDRAM操控器的规划办法,将操控器在Xilinx公司的Virtex-6系列FPGA芯片上完结,经过ISim软件仿真成果,证明了规划的可行性和正确性,以及IP核规划的DDR3操控器具有较好的适应性和灵活性,缩短了体系开发周期、降低了体系开发本钱。