1 导言

以往的数据收集体系大都选用单片机、DSP等微处理器发生A/D转化芯片所需求的操控时序,以及通道转化所需求的时序逻辑信号,这样会占用CPU较多的时刻。本文介绍依据CPLD的高速高精度数据收集体系规划办法,所需操控时序及地址译码等电路均由CPLD发生,并将转化成果放于双端口RAM中,CPU随时从双端口RAM中读取转化成果,大大提高体系的数据收集速度。

在某些操控体系中,其数据收集除了要满意最基本的精度和速度要求外,还有必要在动态规模、分辨率等指标上满意要求。一般的高位数A/D在转化精度和速度上难以统筹,例如现在市场上∑-Δ型串行输出24位A/D,其转化时刻都在ms级,不能满意高速数据收集的要求,为了在较低本钱的前提下仍能获得较高的动态规模和收集速度,规划中选用了依据CPLD操控的带浮点扩大器的两级并行A/D转化计划,体系在小信号输入时扩大较高的倍数,以添加A/D转化的有用位数,在大信号时扩大较低的倍数,切断小量确保信号的首要部分,既确保了数据收集体系的动态丈量规模,一起又统筹到体系的收集精度和速度。

2 带浮点扩大器的CPLD数据收集体系硬件规划

2.1 体系硬件全体框图

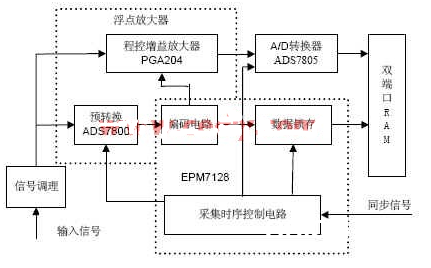

带浮点扩大器的CPLD高速高精度数据收集体系硬件电路如图1所示,它由模拟信号输入调度电路、程控扩大器PGA204、A/D 转化器ADS7800和ADS7805、双端口存储器IDT7134、数据收集时序操控器EPM7128等构成。

所需操控时序及地址译码等电路均由可编程逻辑器材EPM7128发生,CPLD经过编程用多种计数器、逻辑电路、时钟电路等组成的纯硬件子体系完成A/D的操控、转化、读取时序,不只节省了PCB面积,减少了整个体系结构的杂乱程度,提高了体系的牢靠性。

图1 带浮点扩大器的CPLD多通道数据收集体系硬件电路图

浮点扩大器的结构如图1的上方虚线框内所示,首要由12位的预转化A/D转化器ADS7800、编码电路和程控增益扩大器PGA204组成。首要,输入信号接入预转化电路,依据ADS7800的输出成果,由编码电路判别输入信号的规模,设定程控扩大器的扩大倍数(1、10、100、1000倍四个档);程控扩大电路首要是依据编码电路确认下来的增益码完成对输入信号的扩大,在不超出16位A/D输入规模的前提下,尽量将信号扩大满足的倍数,以扩大数据收集体系的动态规模,随后将扩大恰当倍数的模拟信号再送入16位A/D转化器。起浮的扩大倍数称为“阶码”,16位A/D转化成果称为“尾码”,数据收集体系的输出成果由“阶码”+“尾码”组成,这类似于计算机中浮点数的表达方式,“浮点”扩大器也因而得名。

体系选用了具有高速收集坚持功用的转化器ADS7800,它支撑双极性模拟量输入,输入规模±10V、±5V可选,内部具有时钟和电压参阅,采样速率可高达333kHz,然后确保了信号分档的速度。美国BB公司出品的16位A/D芯片ADS7805具有如下杰出特色:(1)自带采样/坚持器,便利对沟通信号的采样;(2)最高采样频率可达100kHz;(3)转化成果全16位并行输出,具有三态缓冲功用,与16位数据总线接口便利;(4)供给±10V的输入规模,与工业规范兼容;(5)单+5V电源供电,可便利地与其它芯片接口。

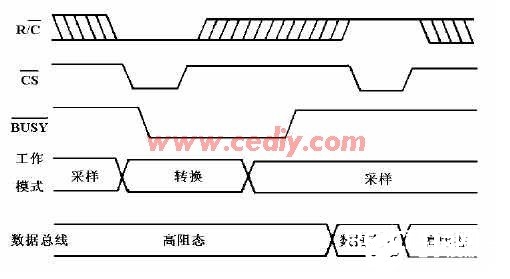

2.2 ADS7800和ADS7805的时序

图2 A/D转化器的作业时序图

2.3 体系作业流程

数据收集子体系的首要操控流程如下:输入信号接入ADS7800进行预转化;编码电路将ADS7800的12位转化成果,取其绝对值,并依据输入信号落在那个区间,确认程控扩大器的增益,获得“阶码”;确定增益数值,经恰当扩大后的信号送入A/D转化器ADS7805获得16位的有用“尾码”;将“阶码”和“尾码”送入双端口RAM保存;切换地址重复上述进程。

从上述进程能够看出时序逻辑操控电路有必要确保两片A/D转化器的转化与成果存储、读取和谐牢靠有序地运转,时序操控电路应当主动生成A/D操控信号以及同享RAM的写入、地址等信号。

3 数据收集体系软件规划

运用VHDL硬件规划语言,选用状况机办法对CPLD进行编程完成流水操控。下面以对ADS7800和PGA204组成的浮点扩大器的操控为例,CPLD扼要程序如下:

ARCHITECTURE AD_CPLD OF adnew_test IS

PROCESS(clockin)

begin

if Reset=‘1’ then

RC12《=‘1’;

state《=s0;

elsif clockin‘event and clockin=’1‘ then

busy_12n1《=busy_12n2; –判别ADS7800的BUSY端是否上升沿

busy_12n2《=Busy12; –读取ADS7800的BUSY端状况

busy_12pd《=not busy_12n1 and busy_12n2;

case state is

when s0=》

RC12《=’1‘;

state《=s1;

when s1=》 –发动ADS7800

RC12《=’0‘;

state《=s2;

when s2=》

RC12《=’1‘;

state《=s3;

when s3=》

if busy_12pd=’1‘ then –ADS7800转化完毕

Data_fw《=Data12_in; –读取ADS7800成果

state《=s4;

end if;

when s4=》 –转化成果取绝对值

if Data_fw》2047 then –》7FFH

Temp_fw《=Data_fw AND “011111111111”;

else

Temp_fw《=not Data_fw AND “011111111111”;

end if;

state《=s5;

when s5=》 –PGA204的增益操控

if Temp_fw《3 then

PGA_G《=“11”; –扩大1000倍

else

if Temp_fw《20 then

PGA_G《=“10”; –扩大100倍

else

if Temp_fw《200 then

PGA_G《=“01”; –扩大10倍

else

PGA_G《=“00”; –扩大1倍

end if;

end if;

end if;

state《=s0;

when others=》 –初始化状况;

state《=s0;

end case;

end if;

end PROCESS;

END AD_CPLD;

4 完毕语

本文作者立异点:所规划的带浮点扩大器的CPLD数据收集体系,其浮点扩大器在小信号输入时扩大较高的倍数,在大信号时扩大较低的倍数,确保了数据收集体系的动态丈量规模;双端口RAM作为A/D转化与CPU之间的桥梁,为高速数据吞吐供给了有力的硬件支撑;CPLD具有很多I/O管脚和较强的带载才能,内部资源丰富、处理速度快, 可完成灵敏多变的操控流程;结合以上几方面的优势,体系总体上完成了对输入模拟信号的高速、高精度数据收集。该体系已应用于自己参加规划的MSINS/GPS微小型组合导航体系中,已发生经济效益20余万元;该数据收集体系也能够广泛应用于需求宽输入规模、高精度、高采样速度和数据处理速度的智能仪器规划中,经济效益将会相当可观。

责任编辑:gt