数模转化器(DAC)是将数字量转化成模仿量,完结这个转化的器材叫做数模转化器。本文将介绍数模转化器的概念、原理、首要技能目标以及不同类型DAC特色进行介绍。

1 数模转化器的概念

经数字体系处理后的数字量,有时又要求再转化成模仿量以便实践运用,这种转化称为“数模转化”。完结数模转化的电路称为数模转化器, 简称 DAC(Digital to Analog Converter)。

DAC的作业原理框图

2、DAC 中的基本概念

分辩率

DAC中的分辩率界说为在不同的输入数字码值下一切或许输出的模仿电平的 个数,N位分辩率意味着DAC能发生2 N −1 个不同的模仿电平,一般情况下它就指输入 数字码的位数。

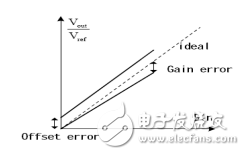

失谐和增益差错

失调界说为当输入0码值时实践输出的模仿信号的值,增益差错定 义为当扣除失调后抱负的满量程输出的值和实践输出的值的差,如图所示。

DAC的失谐和增益差错

精度

DAC中的精度分为肯定精度和相对精度。肯定精度界说为抱负输出和实践输出之 间的差,包含各种失谐和非线性差错在内。相对精度界说为最大积分非线性差错。精度表明为满量程的份额,用有效位数来表明。例如8-bit 精度表明DAC的差错小于DAC输出满量程的 1/8 2 。留意精度这个概念和分辩率不相关。一个12-bit 分辩率的DAC或许精度只要10-bit;而一个10-bit分辩率的DAC或许有12-bit的精度。精 度大于分辩率意味着DAC的传输呼应能够被比较精确地操控。

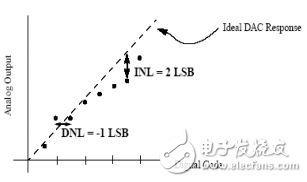

积分线性差错(INL-Integral Nonlinearity)

当除掉失谐和增益差错后,积分线性差错就界说为实践输出传输特性曲线对抱负传输特性曲线(一条直线)的违背。如图所示。

DAC的积分和微分线性差错

微分线性差错(DNL-Differential Nonlinearity)

在抱负的DAC中,每次模仿输 出改变最小为1LSB,微分线性差错界说为每次模仿输出改变最小时对1LSB的违背(将增 益差错和失调在外)。咱们界说的DNL是对每个数字输入码值而言的,有时也有用最大 的DNL来界说整个DAC的DNL。抱负的DAC关于每个数字输入其微分线性差错均为0, 而一个具有最大DNL为0.5LSB的DAC的每次最小改变输出在0.5LSB到1.5LSB之间。如图DAC的积分和微分线性差错所示。

颤动能量(Glitch Impulse Area) 输入信号改变今后在输出端呈现的颤动下的 最大面积。

树立时刻(Settling Time) 在最终值的一个特定的差错规模之内,输出阅历满 幅转化所需求的时刻。

单调性 一个单调的DAC指跟着输入数字码值添加输出模仿电平一向添加DAC。假如 最大的DNL操控在0.5LSB以内,那么DAC的单调性天然能得到确保。

伪动态规模(SFDR) SFDR便是Spurious Free Dynamic Range,即无噪声和谐波的动态规模。噪声和谐波都称为伪信号(Spurious)。

3 数模转化原理

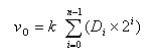

将输入的每一位二进制代码按其权的巨细转化成相应的模仿量,然后将代表各位的模仿量相加,所得的总模仿量就与数字量成正比,这样便完成了从数字量到模仿量的转化。

其间 为二进制数按位权打开转化成的十进制数值。

为二进制数按位权打开转化成的十进制数值。

4 数模转化器的构成及不同类型数模转化器的特色

DAC 首要由数字寄存器、模仿电子开关、位权网络、求和运算扩大 器和基准电压源(或恒流源)组成。用存于数字寄存器的数字量的各 位数码,别离操控对应位的模仿电子开关,使数码为 1 的位在位权 网络上发生与其位权成正比的电流值,再由运算扩大器对各电流值求和,并转化成电压值。

依据位权网络的不同,能够构成不同类型的 DAC,如权电阻网络 DAC、R–2R 倒 T 形电阻网络 DAC 和单值电流型网络 DAC 等。 权电阻网络DAC 的转化精度取决于基准电压VREF,以及模仿电子开 关、运算扩大器和各权电阻值的精度。它的缺陷是各权电阻的阻值都 不相同,位数多时,其阻值相差甚远,这给确保精度带来很大困难, 特别是关于%&&&&&%的制造很晦气,因此在集成的 DAC 中很少独自运用该电路。

5 模数转化器的首要技能目标

DAC 的转化精度与转化速度:转化精度 在 DAC 中一般用分辩率和转化差错来描绘转化精度。

(1) 分辩率

一般用 DAC 的位数来衡量分辩率的凹凸,因为位数越多,其输出电 压vO的取值个数就越多(2n 个),也就越能反映出输出电压的纤细改变,分辩才能就越高。

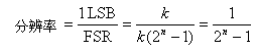

此外,也能够用 DAC 能分辩出来的最小输出电压 1 LSB 与最大输出 电压 FSR 之比界说分辩率。即

该值越小,分辩率越高。

(2) 转化差错

转化差错是指实践输出的模仿电压与抱负值之间的最大差错。常用这 个最大差错与 FSR 之比的百分数或 若干个 LSB 表明。实践上它是三种差错的归纳目标。

(3) 转化速度

转化速度一般由树立时刻决议。从输入由全0 突变为全1 时开端,到 输出电压稳定在 FSR±½ LSB 规模(或以 FSR±x%FSR 指明规模)内 停止,这段时刻称为树立时刻,它是DAC 的最大呼应时刻,所以用它衡量转化速度的快慢。

6 数模转化器的构成

DAC 首要由数字寄存器、模仿电子开关、位权网络、求和运算扩大器和基准电压源(或恒流源)组成。用存于数字寄存器的数字量的各 位数码,别离操控对应位的模仿电子开关,使数码为 1 的位在位权网络上发生与其位权成正比的电流值,再由运算扩大器对各电流值求和,并转化成电压值。

依据位权网络的不同,能够构成不同类型的 DAC,如权电阻网络 DAC、R–2R 倒 T 形电阻网络 DAC 和单值电流型网络 DAC 等

7 DAC 的各种拓扑结构

电阻型:

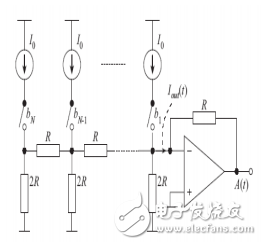

结构如图1所示。图1所示的是一个R-2R阶梯网络型的转化器。其长处在于能完成很好的线性度,因为一切的电流源都是等值的,咱们能够用特别的附加技能使它们间 差错较小,与电阻分压比较其结构简略得多。缺陷是电阻总对错线性的,还包含着和信 号有关的寄生电容,要做到彻底匹配较难。一起速度遭到输出缓冲器的约束,速度做不到很高。

图1 电阻型DAC的结构图

电容型:

结构如图2所示。最高位的电容CN 是最低位电容C1的 1 2N− 倍。长处是功耗较小, 匹配精度比电阻高。首要的约束要素是电容的不匹配,开关的导通电阻,较大RC推迟 以及扩大器有限带宽对DAC速度的影响。电荷分配型DAC的一个首要缺陷是CMOS工 艺中的电容完成起来要占很大的芯片面积。最终因为CMOS工艺中的电容实质对错线性 的,总的DAC的线性度将遭到按捺。适用于中宽带高精度。

图2 %&&&&&%型DAC的结构图

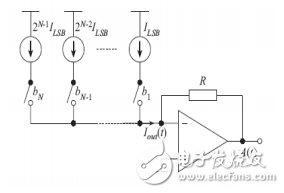

电流型:

结构如图3所示。其长处是当精度小于10位时能将面积做得很小,速度不受扩大 器带宽和较大RC推迟的约束,可到达很高的速度,因为一切的电流都直接流向输出端, 所以能量的运用功率很高,且简单完成。缺陷是对器材不匹配性的灵敏和有限的电流源输出阻抗。合适高速宽带的要求。

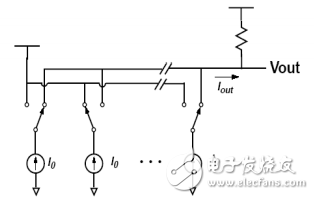

输出时也能够不选用运算扩大器,直接使用负载电阻将电流转化成电压输出,如图4所示。这种方式使得DAC的速率能够不受运放带宽的约束。

图3 电流型DAC的结构图

图4 输出直接使用负载电阻进行转化