作者:张宇清

可编程逻辑器材(PLD)的两种首要类型是现场可编程门阵列(FPGA)和杂乱可编程逻辑器材(CPLD)。依据半导体职业协会供给的数据,PLD现在是半导体职业中增加最快的范畴之一,高功能PLD现在现已从选用最先进的规范单元技能制作的固定逻辑器材手中夺得部分商场份额。而消费电子则是PLD正在快速增加的运用范畴。

PLD职业最近呈现了许多新变化。以往,PLD更多是用在一些特别产品中,例如低本钱原型,或许像路由器这样的小批量产品。而今日,PLD则更多进入消费电子范畴。

PLD快速浸透消费电子商场

在摩尔定律的效果下,跟着电子技能向新一代技能发展,即便在大批量产品的规划中,可编程器材也将变得越来越有竞赛力,这正是赛灵思公司在2007年扩展亚太区总部新加坡研制规划团队的原因之一,扩展后的研制团队还将针对大批量、低本钱的运用规划FPGA。其间一个新项目便是开发低端的、大批量的FPGA,专门针对消费商场。现在,赛灵思的产品现已用在数字高清电视、高档机顶盒与电缆等设备中。众所周知,消费商场的产品现在首要是在亚洲出产,消费电子产品的吸引力越来越大,这种吸引力首要来自亚洲用户的需求。

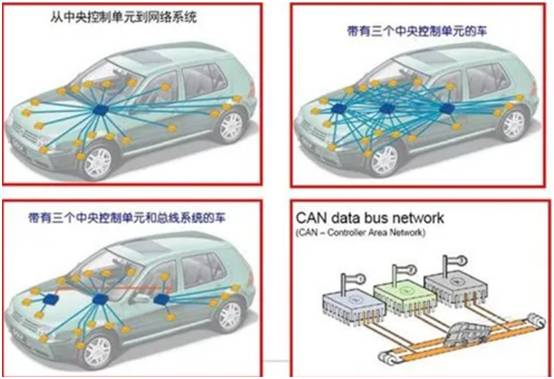

估计2008年又将是一个快速增加的年份,特别是在消费和轿车范畴。平板显现是电子职业中另一个增加最快的范畴,依据iSuppli的数据,全球液晶电视和等离子电视的出货量到2009年将到达近8000万台。FPGA在支撑这些显现技能背面的很多要害技能方面扮演了要害人物,平板显现商场成为赛灵思公司快速增加的商场之一。

跟着便携式电子设备制作商不断向商场推出新产品,移动设备也为PLD带来巨大的时机。今日的规划人员越来越多地将视界转向ASIC(专用集成电路)和ASSP(专用规范产品)的固定架构之外,以充分运用可编程逻辑内涵的规划灵活性和上市时刻优势。除了需求更高的功能以外,顾客现在还需求更高的易用性——iPhone便是一个很好的比如。PLD使得规划人员可以运用易用性特色使产品在商场上锋芒毕露,一起还可以加速产品推向商场的速度。遵从摩尔定律的安稳跋涉,PLD现在可以一起满意这一快速增加的移动设备商场对本钱和功耗方面的严苛要求。

FPGA产品凸显功能优势

赛灵思有两个系列产品是面向消费运用的:Spartan-3系列FPGA和 CoolRunner-II CPLD。Spartan系列供给了多个面向范畴优化的FPGA渠道来满意本钱功率方面的需求。而竞赛厂商关于一切运用仅供给一种渠道,单一渠道的问题是客户需求为芯片上特定运用并不需求的电路付出必定的本钱,因而本钱功率低。

Spartan-3A以及更新的系列产品供给了丰厚的功能来下降客户的整体体系本钱,并将所需求的电源轨数量削减到两个,而咱们最接近的竞赛对手的产品也需求四个电源轨。电源轨越多,就意味着需求更多的稳压器和分立器材,也就意味着规划更杂乱,电路板本钱更高。

赛灵思的FPGA产品比竞赛产品具有更宽的供电电压规划,而窄供电电压规划需求本钱更高的稳压器。赛灵思FPGA器材经过高度集成可支撑业界最广泛的I/O 规范挑选,因而在许多规划中不再需求外围器材,然后进一步节省了本钱。赛灵思供给业界最广泛的FPGA器材和封装挑选。关于大多数消费运用,赛灵思供给的 MicroBlaze针对嵌入式和操控运用的微处理器进一步削减了对外部MCU(微操控器)的需求,免费的RTOS(实时多任务操作体系)支撑(如 uCLinux)可协助客户将整体本钱降到最低。Spartan-3A渠道系列器材支撑系列内器材以及与Spartan-3AN系列器材的引脚对引脚 (pin-to-pin)移植,这在FPGA职业仍是创始。客户不需求从头规划电路板就可以选用不同密度规划的器材。Spartan仍是第一个支撑客户专用I/O接口的FPGA,如现在数字显现范畴常用的TMDS(最小化传输差分信号)和RSDS(低摆幅差分信号传输)。依据咱们的经历,大多数消费运用需求的FPGA密度规划都在160万门上下。赛灵思的CoolRunner-II CPLD是全球本钱最低的低功耗CPLD,而且选用了最小的晶圆规划封装(如4mm×4mm)。

低功耗堪与专用电路对抗

关于数字显现、机顶盒和无线路由器等大多数消费运用来说,低的待机和静态功耗十分重要。Spartan-3A供给了比竞赛产品更多的节电作业形式。悬挂节电形式下FPGA可快速唤醒,不需求等候装备时刻,一起可节省待机电耗高达80%。休眠形式可节省待机电耗高达99%,这一水平是最接近竞赛对手产品所选用的中止时钟所不可以到达的。即便对最接近的竞赛厂商来说,为了仿真完成上述两种形式,他们都需求选用外部电源办理芯片。

而 Spartan-3A的电源轨规划就考虑到将外部器材的运用减到最少,如去耦滤波电路、钽电容和铁氧体磁珠(Ferrite Bead)等,因而可以下降体系本钱和功耗。高度集成的I/O不再需求驱动器、缓冲器和电平移位器,然后可进一步节省功耗。在低功耗形式下,FPGA供电电压可下降至1伏,而关于竞赛产品来说完成这一点十分具有挑战性,价值也比较贵重。在最近的功耗基准测验中,Spartan-3A的静态功耗比竞赛对手 65纳米系列的产品还低。功率驱动的编译器和软件优化也会协助客户在规划中进一步下降功耗。未来,FPGA软件、工艺和高档低功耗形式相结合的组合技能将会使功耗可以与ASIC和ASSP器材的功耗相对抗。