1 导言

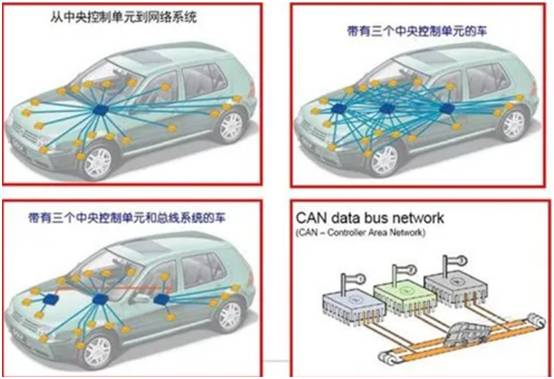

跟着高速铁路的迅速发展以及机车车辆的现代化发展趋势,对列车总线的牢靠性、安全性、通讯实时性的要求进一步进步,国内的传统的现场总线难于满意要求,而多功用车辆总线(MVB)是快速的进程操控总线,能供给最佳的响应速度,且合适用作车辆总线,这就使得MVB逐步成为下一代车辆的通讯总线规范。跟着MVB通讯网络运用的日益广泛,我国铁道部已将其作为列车通讯的规范渠道,国内铁路轨迹交通设备制作企业也相继从国外引入配备有MVB网络的列车微机操控体系,一些部分也展开了MVB相关产品的国产化研讨和自主研制作业。为了确保不同设备制作厂家出产设备的兼容性,也为了验证所研制的MVB产品的协议一致性,有必要对各个MVB设备进行协议一致性测验,以进步MVB设备互连的成功率。在MVB的规划和施行进程中,正确地分分出MVB总线运转状况是一个重要的作业。因此对MVB网络进行剖析是进一步研讨MVB技能的必备手法。

2 MVB协议简介

MVB在物理层能够运用3种不同的物理介质:无阻隔的短距离电气介质ESD、有阻隔的中距离电气质EMD和长距离光纤介质OGF,一切的介质均选用1.5 Mb/s的传输速率。MVB对总线的介质拜访选用集中操控、周期性分配的主一从方法,由总线上专一的总线管理器即主设备集中操控介质的存取。作业时主设备将总线带(每个底子周期)分为周期性预先分配(周期相)和非周期性按需分配(偶发相)两部分。周期相用于紧迫性、时性要求高且矮小的周期性进程变量数据的传输速度、电机电流、司机指令等;偶发相则用于传输冗长但不频频的非周期性的音讯数据,如设备确诊或旅信息。为满意MVB在链路层上供给的2类数据通讯服务的要求,TCN规范在MVB上界说了与总线类无关的实时协议RTP。从运用层看,RTP供给了2种类型的通讯服务:进程变量和音讯服务。进程变量服务的协议只包含物理层、链路层(分为介质存取操控MAC子层和逻辑链路操控LLC子层)运用层3个层次,用以传输周期性的操控指令和操控变量,以完结操控的实时性要求。其间链路层首要经过链路进程数据接口LPI处理端口和通讯缓存的操作,完结协议大部分的作业;运用层则经过运用变量接口AVI处理进程变量的拜访。

3 MVB总线剖析结构规划

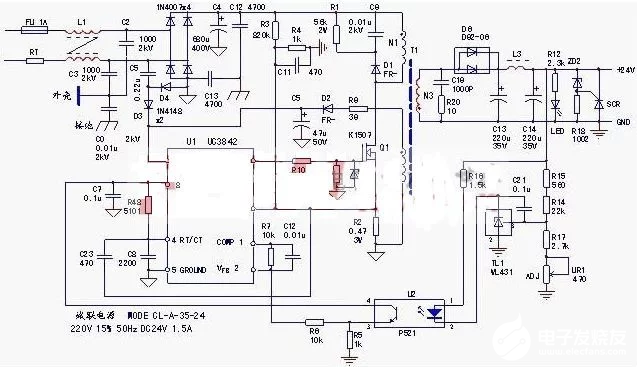

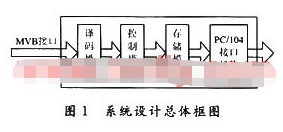

MVB网络上传输的进程变量数据是经过主从帧应对与周期性播送的方法,总线剖析仪可衔接在MVB网络中时刻监听MVB网络中传输的帧数据。MVB总线剖析仪按功用可分为译码模块、操控模块、存储模块和PC/104接口模块4个部分,体系规划整体框图如图1所示。译码模块收集总线上的数据,将数据传送给操控模块,操控模块则依据帧的不同状况写入存储模块,存储模块用于存储帧数据,而对上位机供给PC/104接口。

3.1 译码模块

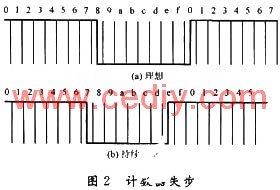

在MVB网络中选用曼彻斯特编码,数据传输速率为1.5 Mb/s,采样频率为数据传送频率的16倍频率即24 MHz(周期为41.67 ns),因此一个完美的数据波形应为8个低电平和8个高电平,如图2(a)所示。在非抱负的状况下,曼彻斯码凹凸电平的持续时刻会在一个有限的范围内随机的改变,当这种改变是接连的变长或许接连的变短时,就有或许形成计数器的失步,如图2(b)所示。

形成这一失步的底子原因是计数器的归零是不受操控的,而采样这一动作的触发又是受制于计数器的,4 b计数器的归零完全是24 MHz时钟驱动下累加的成果(0000~1111的循环累加)。因此当呈现电平接连变长或接连变短的状况时,本应该在每个曼彻斯码周期完毕后归零的计数器不能在下个曼彻斯码周期到来时回复到初始状况即“0000”,这种过错的不断累积将导致译码的失步(位失步)。这里是采纳如下办法处理这一问题:检测每位曼彻斯码中必定呈现的电平跳变沿,将这一跳变沿作为计数器的操控信号;当此信号有用行将计数器置于抱负状况,这样在每位曼彻斯码中,计数器都能够进行1次与MVB串行信号的同步。

3.2 操控模块

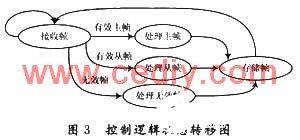

操控逻辑接纳解码器单元解码后的信号,假如帧不完好或许CRC校验过错,则加过错标志2直接与入存储单元;帧完好则需求判别主从帧;假如主帧则可直接加标志0写入存储单元;假如为从帧,则需求判别从帧抵达时刻是否满意要求;假如符合要求则加标志1写入存储单元。不然加标志2写入存储单元,整个操控逻辑的状况搬运如图3所示。

3.3 存储模块

通讯存储器是MVB总线剖析仪的重要组成部分,它担任存储MVB总线通讯的数据,因此MVB与上位机经过PC/104接口模块会频频的拜访通讯存储器进行数据的读操作。完结通讯存储器有3种方法:用FPGA内部自带的RAM资源完结;用FPGA内部的寄存器完结;用外部存储器,例如SRAM,E2PROM等完结。终究选用FPGA内部自带的RAM资源完结通讯存储器。原因包含以下几点:现在高档的FPGA都带有大小不等的片内RAM资源,假如运用外部的存储器,则需求一些扩展电路因此导致电路变的杂乱,增加了不稳定性的一起也带来了外部寄存器的拜访推迟问题。经过比较,选用FPGA内部RAM完结通讯存储器是较好的计划。

3.4 PC104接口模块

PC104接口有4种拜访方法:8位存储器、16位存储器、8位I/O和16位I/O。这里是8位存储器方法,逻辑完结和布线都相对简略。经过PC104总线接口,设备能够衔接到PC104总线上并作为PC104总线上的一个规范设备运用。上位机能够经过PC104总线拜访设备和通讯存储器。一类设备仅仅CPU操控的设备之一,因此分配的内存空间有约束的。内存空间为0xD0000~0xE0000,需求地址译码将设备的通讯存储器映射到CPU的该内存区。PC104选用仓库式结构,单列双排插针和插孔,P1:64针,P2:40针,算计104个总线信号,接口引脚界说如表1所示。

4 试验与运用

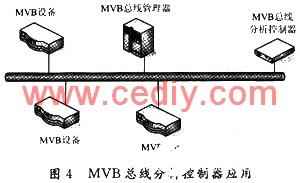

试验室里在试验室建立的MVB网络如图4所示,MVB网络由MVB主设备DUAGON公司的总线管理器D412,MVBC01芯片规划的MVB一类设备1与FPGA规划的MVB一类设备2与设备3。

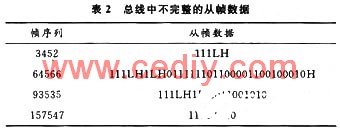

MVB总线剖析仪衔接MVB网络,上位机经过PC/104总线读取MVB总线剖析仪存储模块,MVB总线剖析仪完好存储了总线上数据,其间在一切取得的数据中不完好的从帧数据如表2所示。

依据对收集到的不完好帧数据的剖析,帧不完好的原因首要体现在帧头的不正确(存在高电平或低电平时刻过长或过短),CRC校验过错(生成的CRC不正确),帧数据不完好,完毕符时刻过短。对主从帧数据对应联系来看,当总线上传输主帧时,设备应发送但没有发送从帧的现象呈现,针对这些问题能够逐个查看FPGA等可编程器件里逻辑规划过错,经过改善削减不完好帧的呈现,然后确保自主研制的MVB设备的数据在MVB网络中牢靠传输。

5 结 语

本文在研讨MVB多功用车辆总线的基础上,开发了具有PC104总线接口的MVB总线剖析仪。该MVB总线剖析仪现已完结了记载MVB网络传输一切数据,有利于更深一步把握MVB总线网络数据传输技能,并为验证MVB设备互连与互操作性做好预备。

责任修改:gt