与开发本钱很高的ASIC比较,FPGA可重复编程的功用正遭到体系规划者的喜爱。此外, FPGA的功用和功用也越来越强壮,包含32位软处理器、SERDES、DSP块和高功用的接口。现在的低本钱FPGA乃至能够满足大批量的运用。规划人员选用FPGA能够快速开发产品,以应对产品快速上市(商场要求缩短产品的开发时刻)和长途更新的需求。 可是,把器材出产、现场更新和固件长途重构的作业外包或许会导致FPGA被仿制、克隆或盗版。这对某些企业是个严峻的问题,因为有些算法对企业坚持竞赛优势是必不可少的,而外包或许使这些算法被他人运用。因而,考虑FPGA规划的安全性是一件非常重要的事。

FPGA有两种类型 :根据SRAM、需求用外部引导器材装备的易失FPGA,以及将装备保存在内存中因而不需求外部引导器材的非易失FPGA。根据SRAM的FPGA是易失器材。假如堵截电源,装备即被删去,有必要对器材进行从头装备,然后器材才干作业。这类器材能够用处理器或运用SPI或并行闪存经过JTAG端口编程。就安全性而言,它们是很软弱的。一旦体系上电,盗版者就能垂手可得地获取FPGA的位流。Flash和反熔丝FPGA对错易失性的器材,它们上电后即可编程,无需运用任何外部存储器。这些非易失器材具有第一流其他安全性。可是,反熔丝FPGA遭到两个方面的限制: 1 )它们不能再次编程。2 )它们的功用和内存容量有限。而Flash FPGA和SRAM FPGA是能够重复编程的。

盗版行为分为几种类型:“克隆”仿制体系元件的行为,乃至不用知道内部的逻辑。经过阻拦FPGA的位流和仿制装备,能够轻松地克隆一个低本钱SRAMFPGA。“逆向工程”需求了解FPGA的逻辑功用,以便进行修正以满足盗版者的需求。盗版者能够剖析无维护的位流以仿制原先的规划,或解剖器材剖析其内容。还有一个被广泛运用的盗版手法是“出产超越客户订货量的体系”,然后向商场出售剩余的体系,而专利持有者却无法从中取得收益,没有任何办法能够阻挠不择手法的分包商这样做。最终一种盗版办法是“偷盗服务”,盗版者经过破解体系的安全设置来取得特定的服务,如收看卫星电视节目。

冲击盗版能够选用多种安全办法,最简略的办法的是运用一个保密位,避免FPGA的装备数据被截获。有了这个保密位,盗版者假如企图读取装备数据,读出的数据将悉数为零。一切的FPGA都有这种类型的维护。可是,假如引导文件坐落器材的外部,相对就比较简单仿制装备,规范的SRAM FPGA便是这种状况。假如装备数据是在器材内部,如非易失FPGA ,保密位就会有很好的保密作用。

与反熔丝FPGA不同 ,SRAMFPGA和FlashFPGA是可重复编程的,它们答运用户调整规划或赋予FPGA一个全新的功用。此外,现在乃至能够长途修正FPGA装备文件,然后修正体系。尽管重构对某些运用来说是个长处,但它也或许成为一个安全隐患,因为盗版者或许阻拦并获取新的码流。不过这能够经过在传输时维护位流来处理。

尽管Flash FPGA比SRAM FPGA更安全 ,它们也有缺陷。它们的密度和存储容量有限,功用和I/O的速度也有限。

针对这些缺陷,莱迪思半导体公司现已开宣布一种立异的技能,它结合了以下两种技能的长处:

* 功用和存储器容量较大的低本钱SRAM

* 能够内部存储重构数据的Flash

莱迪思共同的flexiFLASH技能,将SRAM和Flash整合在同一个FPGA中,能够一起完结以下几个方面的长处:

* 位流装备

* 以最短的体系中止时刻进行长途从头装备

* 数据维护和器材加锁

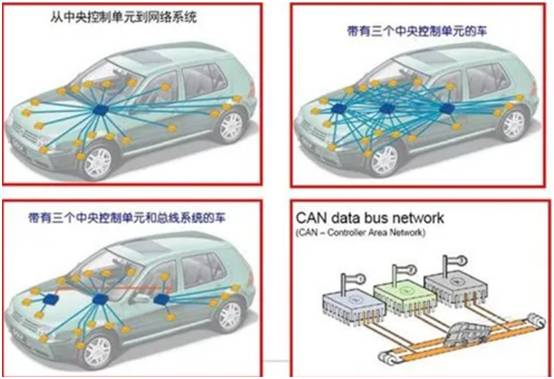

杂乱体系中的规划安全性

工程师正面临着构建日益杂乱的体系的应战。

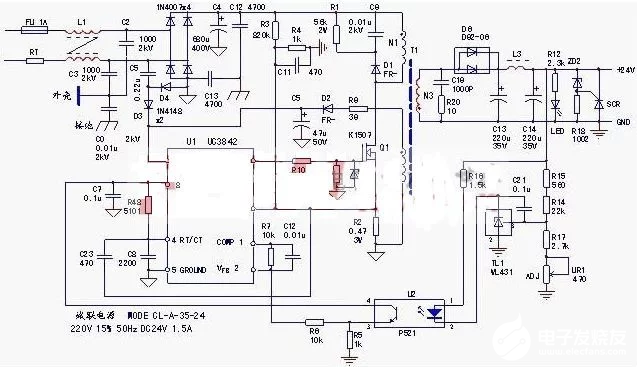

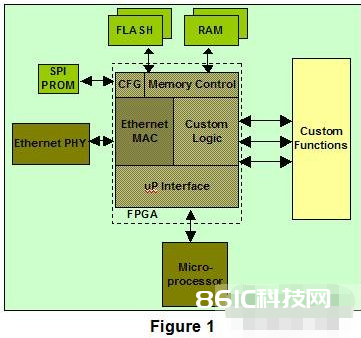

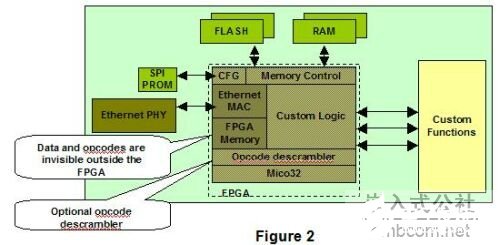

图1 FPGA与微处理器相连的体系

图1展现了一个FPGA与微处理器相连的体系 。微处理器经过一个外部PHY和一个集成在FPGA内的MAC与以太网衔接。与竞赛者的产品不同,这个微处理器中还包含用户逻辑。FPGA经过一个Flash来装备。Flash和RAM中包含有微处理器的程序和体系的数据。假如体系需求更新,就经过以太网来发送数据。为了维护规划,FPGA数据和位流都经过了加密。可是,发送到微处理器的数据和指令未加扰,因而盗版者能够查看此数据并加以仿制。一种或许的处理办法是在FPGA内完结软微处理器,它能够拜访FPGA的内部存储器组,而从外部却无法看到存储器组。这些存储器组能够用来存储重要的算法和数据。

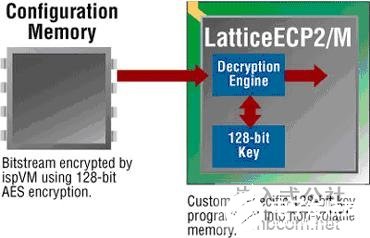

图2 处理器集成在FPGA之中

图2展现了同一个规划,但处理器集成在FPGA之中。图2中选用的软微处理器是LatticeMico32 。规划师构建了解扰器,因而加扰是秘要的。运用解扰器答应加密的指令存储在外部存储器。为了加密位流,莱迪思为几款FPGA供给了128位AES密钥。

图3 用128位AES密钥维护规划

首要,工程师运用莱迪思的软件规划东西套件ispLEVER (7.0或更高版别)开发FPGA代码,完结归纳、映射、布局布线和仿真后,发生位流,经最终验证后再用ispVM体系(莱迪思的编程东西)对电路板编程。当规划师对体系的功用感到满足时,此刻就要来做维护规划的作业。能够用莱迪思的ispLEVER东西或莱迪思的编程东西ispVM System对位流加密,用户可挑选128位密钥。编码的位流能够是十六进制(从0至F,不区别大小写)或一个ASCII密钥(可用一切字母数字字符和空格,大小写灵敏),然后运用任何非加密的文件编码将该位流加载到装备存储器中。

现在密钥应该现已保存在一个可编程存储区。编程是经过器材的JTAG端口进行。应该注意到,用密钥对位流加了密,现在只能经过加密的位流对FPGA进行装备。用sysCONFIG接口或JTAG接口能够对莱迪思的FPGA进行编程。该sysCONFIG接口能够让用户运用会集装备形式,或FlashSPI ,或以并行的方法运用并行装备形式从头输入数据。契合IEEE 1149.1和IEEE1532规范的JTAG端口答应以突发位流(或快速编程)形式、或用1532形式对数据进行编程。JTAG端口用来对器材中的AES128位密钥编程。不需求用特其他形式来保存FPGA中的128位密钥。

在莱迪思的FPGA中运用一个编码位流能够避免器材的装备被从头读取,但需求一些办法来保证装备能够正确地运作。位流未加密时,FPGA履行CRC操作。假如程序不正确,DONE信号坚持在0,INITN变为0 。用户依然能够拜访JTAG Usercode寄存器。对FPGA的位流译码时,它存储位流用户码,用来寄存FPGA运用程序的版别号。

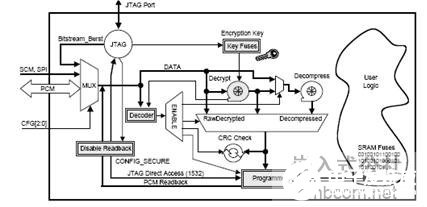

图4 加密位流的数据途径

图4展现了加密位流的数据途径。当数据进入FPGA时,解码器读引导程序,前面一切的数据被疏忽。即便解码器检测到加密的文件,假如FPGA的密钥未被编程,数据则被阻挠,DONE信号坚持在‘0 ’ (表明装备失利)。假如密钥已被编程,FPGA查看引导程序,指出后边一切的数据应经过解码器。然后FPGA查看规范引导程序,得知数据是否已被紧缩。假如数据没有被紧缩,则将它直接发送到解码单元。假如数据已紧缩,就先把它送到解紧缩引擎,然后再送到解码单元。一旦经过CRC校验,即对SRAM进行编程。DONE位被激活时,解紧缩和译码擎不作业,答应其它JTAG链元件接纳装备数据。

莱迪思的经济型ECP2/MFPGA具有位流加密功用,内置闪存的非易失LatticeXP2 FPGA也有此功用。LatTIceXP2FPGA把SRAM映射合并入同一块芯片,规划和含有位流装备的Flash映射都在此芯片上作业。当规划师要点重视电路板的面积和快速发动时刻时,这类器材特别有用。

内置闪存的FPGA

非易失FPGA供给额定的Flash维护安全功用,能够避免内存因意外或未经授权的操作被擦除或从头编程。Flash维护功用选用6?位密钥。

对器材进行删去或从头编程时, ispVM System会核对Flash是否被维护。假如是,就要求用户输入6?位密钥,然后ispVM查看这个密钥是否与存储在器材中的密钥共同,假如共同就履行操作。可是,假如丢掉了密钥,器材就再也不能被擦除了。

这些安全性办法不只维护了用户电路板上的规划,并且也避免了企图修正体系功用的盗版行为。这些功用还有助于长途的体系更新。莱迪思FPGA供给这一功用,运用户能够经过对FPGA重复编程来更新他们的体系,而不会中止它与周围元件的联络。此功用被称为TransFR 。

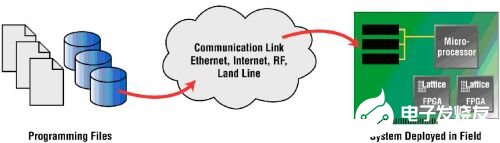

图5 用最短的中止体系时刻进行长途更新

FPGA最值得注意的的特点是规划人员很简单对器材进行重构。可是,重构一般意味着体系要中止很长时刻。可是,莱迪思开发的TransFR技能将重构的影响降至最低。莱迪思的几个FPGA系列都支撑TransFR技能,包含那些含有内置闪存的器材,如MachXO 、LatTIceXP和LatTIceXP2,以及像LatTIceECP2 /M那样的SRAM FPGA。

TransFR是一种一起运用基本任务编程和鸿沟扫描单元的技能。基本任务编程修正非易失存储器的内容(内部的或外部的) ,以便使FPGA的SRAM部分持续作业。莱迪思的FPGA具有能够取样和预加载的鸿沟扫描单元,能够在编程时操控FPGA的I/O。

图6 履行TransFR的4个进程

履行TransFR的4个进程:

1,进行基本任务编程。体系对FPGA的非易失性存储器再编程,但不会中止SRAM的功用。

2,能够确定I/O的状况,用户能够坚持或预先确定I/O的状况。在整个从头装备进程中,I/O的值坚持不变,以避免体系被封闭。

3, 接着用JTAG指令把新的装备传输至非易失存储器。一完结对SRAM就履行大局复位,以便使该器材处于一个已知的状况。然后开释I/O的状况,并再次确定PLL。

4,开释输出,内部逻辑中止对I/O的监测。

要运用TransFR,需求用到ispLEVER开发东西和ispVM。

用户经过运用128位AES密钥加密文件和LatticeTransFR技能完结了更新进程,但仍有或许因为体系自身的缺点或违法行为引发体系故障。尽管FPGA的位流是加密的,可对错法操作或传输中的过错都或许损坏它,然后导致FPGA被堵塞,使体系无法正确地重启。为了处理这个问题,莱迪思推出了“双引导 ”功用。

双引导装备

在装备存储器中存储两个编程文件。

图7 双引导装备

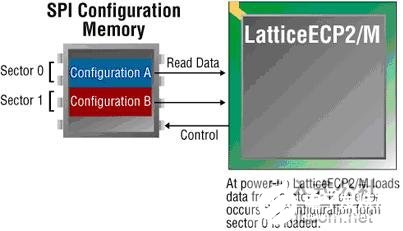

激活PROGRAM引脚或发动JTAG改写指令后,FPGA下载存储在Sector 1的位流 。假如CRC犯错,FPGA自动康复到Sector0装备。Lattice XP2非易失FPGA也有此功用。该Flash元件具有自动装备,还有一个用来寄存安全( “golden” )装备的SPIFlash。

莱迪思具有许多能协助规划人员保证规划安全的产品。Lattice ECP2/MFPGA是一款具有128位AES密钥的高安全性器材。这些经济的器材供给了大存储容量(高达5.3 Mbit)、高速I/O和SERDES。非易失性LatticeXP2FPGA是商场上一款很共同的器材,它有着极高的安全性。因为选用了FlexiFlash技能,位流存储在器材的Flash中,并由128位AES密钥对它进行维护。此外, TransFR更是保证了肯定安全的长途体系更新。

规划的安全性应该是规划进程的一部分,而不是过后再去考虑。不管挑选了哪种技能,最重要的是要避免规划被篡改,不管这个篡改行为是无意的还对错法的。

责任编辑:gt