1.导言

跟着红外焦平面阵列技能的快速开展,红外成像体系完结了高帧频、高分辨率、高牢靠性及微型化,在方针盯梢、智能交通监控中得到了越来越多的运用,并向愈加广泛的军事及民用范畴扩展。实时红外图画处理体系一般会包含非均匀校对、图画增强、图画切割、区域特征提取、方针检测及盯梢等不同层次的实时图画处理算法,因为图画处理的数据量大,数据处理相关性高,因而实时红外图画处理体系有必要具有强壮的运算才能。现在有些红外图画处理体系运用FPGA完结可重构核算体系[1],运算速度快,但关于杂乱算法的完结难度比较高,且灵活性差。大多数红外图画处理体系则选用DSP+FPGA的硬件架构[2],其间DSP担任完结图画处理算法,FPGA担任完结各种接口电路,但比方图画多级滤波等处理算法杂乱度高,只运用DSP处理睬消耗很多时刻,一般选用并行多DSP体系以满意实时性要求[3],但体系比较杂乱,体积和功耗也欠好操控,完结本钱高。因而需求在硬件结构上合理分配处理使命,比方FPGA可以完结输入图画的预处理作业,减轻DSP的担负,本试验室自主研发的ASIC芯片可以对输入红外图画进行多级滤波处理,进一步解放DSP。本文针对红外图画处理体系的实时性要求,提出了依据DSP+FPGA+ASIC的图画处理架构。

2.实时红外图画处理体系

因为实时红外小方针检测算法的前端处理数据量大、实时性强且算法杂乱度高,咱们的体系结构需求确保灵活性,可以习惯各种杂乱的算法,一起又要确保高速处理才能,因而实时红外图画处理体系选用DSP+ FPGA+ASIC的架构来满意规划的要求。其间,DSP具有高度的可编程性,可以完结比较杂乱的使命。FPGA的处理速度稍逊于ASIC,但具有必定的灵活性,它可以实时接纳红外小方针检测算法前端的数据,完结输入图画的一些预处理作业。ASIC芯片处理速度快、功用强且牢靠性好,可以完结图画滤波等特定的使命。

一种实时红外图画处理体系结构框图如图1所示:

FPGA选用ALTERA公司的Stratix系列的EP1S10芯片。该芯片供给多达10,570个逻辑单元(LEs),存储器容量为920,448016 bits,一起供给了高速DSP模块以及乘法器,专用乘法器合适于作协处理器,可以分管DSP杂乱和耗时的算术运算,提高体系的功用。

DSP选用TI公司的TMS320C6414芯片[4]。该芯片主频为600MHz,数据处理才能峰值可达4800MIPS(每秒48亿条指令)。由8个彼此独立的功用单元构成。包含两组通用寄存器组,每组含有32个32位寄存器。片内选用2级存储器结构。

ASIC运用本试验室自主研发的多级滤波芯片[5]。该芯片选用SMIC 0.35mm工艺,芯片内部作业频率可达50MHz。有三个数据通道,别离级连不同数量的1*3根本滤波模板,每路数据通道选用流水线结构。选用定点运算,核算精度为8位二进制小数,可处理位宽为8-16位的数据,吞吐量为5M-10M像素/秒,支撑128*128,256*256,320*240三种帧格局的图画滤波。

3.处理使命的合理分配

红外探测器输出图画数据到信号处理板,先进入FPGA进行预处理,预处理包含非均匀性校对和图画增强等。ASIC对输入图画数据进行多级滤波处理。FPGA在后续算法中也能协同DSP作业,算法中对运转速度要求很高,而算法结构不太杂乱的处理均可在FPGA 中完结,然后使得该FPGA 成为DSP 的协处理器。通过预处理后的红外图画数据输出到DSP中进行后续算法处理,DSP的处理包含红外潜在小方针检测算法。DSP 处理后的潜在小方针和图画数据通过FPGA传输到DPRAM中存储。

该实时红外图画处理体系首要由三部分组成:FPGA模块,DSP模块和ASIC模块。在满意红外图画数据处理的实时性和高速牢靠性要求的前提下,各处理模块所处理的使命要尽量到达平衡。

从资源视点看,算法用硬件处理速度快,占内存空间小,但灵活性差;用软件刚好相反,处理速度慢,但灵活性好。因为规划要满意实时性要求,期望硬件承当的使命越多越好。PGA作为一种可编程的硬件资源,尽管它有适当强的规划灵活性,可是考虑到规划、完结调试的难度,不合适做大局、杂乱的操作。ASIC芯片处理速度快,但灵活性差,只合适处理一些特定的占用很多处理器资源的运算。DSP作为软件资源,特点是灵活性好,合适杂乱的算法,但速度慢。

从算法视点考虑,一个完好的算法在处理上是有层次的,算法对原始数据的操作是简略的、规矩的,对后续数据的处理往往比较杂乱,一起算法在完结前会被预先分红几个彼此独立的功用模块。因而低层的、简略的操作可以由FPGA中的逻辑单元模块或ASIC芯片硬件来完结,高层的、杂乱的操作则由DSP软件来完结。

依据上述剖析,本规划中FPGA首要完结与各个外部设备的接口操控逻辑,一起完结一些数据量大、运算结构简略、速度要求高的算法;DSP完结后续结构杂乱的方针检测算法;ASIC芯片对输入图画进行多级滤波处理。此计划确保了体系有满意的处理速度,可以到达红外图画处理体系的实时性要求。

3.1 FPGA模块

FPGA内部逻辑结构框图如图2所示。

FPGA首要完结以下几方面的作业:图画数据接纳逻辑,图画数据预处理模块,输入缓存FIFO,DSP接口操控逻辑,ASIC接口操控逻辑,DPRAM接口操控逻辑,算法处理模块。

(1) 图画数据接纳逻辑:依据探测器输出的数字视频信号的场同步,行同步以及时钟信号,发送操控信号接纳图画数据。

(2) 图画数据预处理模块:对接纳的图画数据进行非均匀性校对和图画增强等预处理。

(3) 输入缓存FIFO:由FPGA内部装备输入缓冲存储器FIFO。预处理后的图画数据可以接连不间断地写入FIFO中,以供DSP读取进行后续的图画处理。

(4) DSP接口操控逻辑:DSP 接口时序操控逻辑有必要严厉依照TMS320C6414的EMIFA

可编程同步接口的时序来编写,而且满意相应的树立坚持时刻要求。DSP发动EDMA通道

读取红外图画数据,通过FPGA的内部FIFO进行接连的图画传输。

(5) ASIC接口操控逻辑:依照ASIC芯片的时序编写其操控逻辑,将图画数据导入ASIC

芯片进行图画多级滤波处理。

(6) DPRAM接口操控逻辑:编写DPRAM的操控逻辑,将DSP 处理后的数据通过FPGA传输到DPRAM中存储。

(7) 算法处理模块:依据详细算法的需求,协同DSP完结算法中速度要求高,结构不太杂乱的运算。

3.2 DSP模块

DSP首要完结红外小方针的检测和盯梢算法,功用如下:

(1) 发动EDMA通道不断读取FPGA输出的红外图画数据。

(2) 对输入的红外图画数据,运转方针检测和盯梢算法,检测运动方针,并确认其方位。

(3) 与FPGA树立衔接,将算法中比较规矩的运算交给FPGA处理。

(4) DSP将处理后的运算成果通过FPGA传输至DPRAM中存储。

3.3 ASIC模块

ASIC芯片从FPGA中接纳预处理后的图画数据进行处理,处理后的三路数据同步写入内部三个同步FIFO,DSP可以依据需求挑选输出多级滤波处理后的成果,进行后续算法的处理。

4.试验成果与剖析

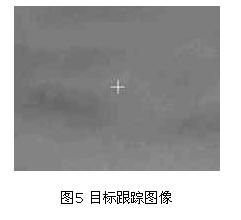

实时红外图画处理板已成功运用于多个红外探测体系中,作用杰出。图3为试验时选用

高德IR108D探测器取得的原始红外图画,图4为通过多级滤波处理后标识的图画,图5为通过方针检测算法处理后输出的盯梢图画。可以看到,该体系可以实时检测并盯梢红外图画中的运动小方针。

5.结语

本文运用高功用的DSP(TMS320C6414),可编程逻辑器件FPGA (Stratix系列的EP1S10)和专用ASIC多级滤波芯片,提出了DSP + FPGA + ASIC的图画处理渠道架构,规划了处理才能强、接口牢靠安稳的红外图画处理体系,并在体系中完结了非均匀性校对、小方针检测等算法。试验测验标明,该实时红外图画处理体系对每场320×240有用像素,每个像素14bit,场频50Hz的输出数字视频信号可以进行实时处理,对视场中的运动小方针完结检测和盯梢功用,满意体系首要功用指标要求,成功运用于红外探测体系中。

本文作者立异点:选用自主研发的ASIC芯片对红外图画进行多级滤波处理,速度快,牢靠性好,为DSP后续的方针检测盯梢算法节省时刻。