移动通讯体系开展数十年,一向为寻求更高的频谱功率而进行技能更新,从2G年代的GMSK,到3G年代的CDMA,到4G年代的OFDM。一起,大规模集成电路的规划技能与生产技能,也有了从几百纳米到几十纳米的年代改动。体系越来越大的带宽需求,意味着对终端芯片渠道越来越高的处理才能要求。体系从2G 到4G的开展,无线网络自身的开展也是需求一个较长的时刻与进程,且对已有的2G和3G网络的筛选也不行能在一夜间完结,所以对终端芯片渠道也提出了自习惯的随网络演然后改动的需求,即多种形式主动切换的作业形式需求。本文将从几种无线通讯体系对终端基带芯片的需求开端评论,介绍一种由精约纳电子公司规划完结的适用于2G/3G/4G的软件无线终端基带芯片渠道。

1. 现有4G终端基带芯片的情况

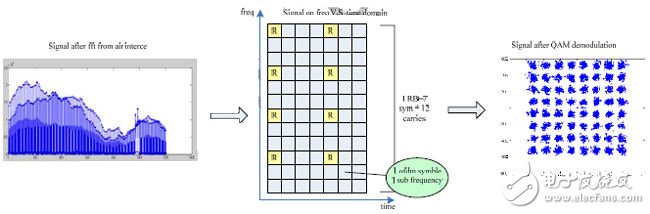

如下图1所示,4G无线通讯体系根底技能是OFDM。OFDM体系信号是时频域都存在的阵列信号。时频域信号间的改换,信道估量与MIMO检测等很多阵列信号的处理,需求很多并行的矢量处理。高度并行的矢量处理器正应OFDM体系阵列信号处理需求而生。 多核多线程内核加上向量处理器是4G基带芯片架构的大势所趋。

图1:OFDM体系阵列信号处理示意图

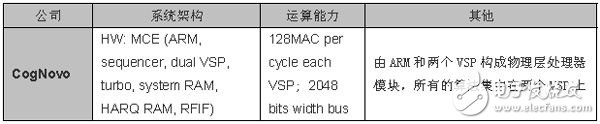

从已宣布的有关无线终端基带处理器的文献和材料来看,业界在可编程和矢量处理运用方面已有许多发展,有如表1所示。

表1:基带处理器中的处理才能

其它的还有IMEC 的ADRES,Michigan University 的ArdBerg等。

2. 2G/3G/4G的终端基带体系需求剖析

终端体系需求分为两个方面,一是功用需求,一是功用需求。本章节通过笼统架构示意图阐明,2G/3G/4G几个体系的功率需求;再逐渐剖析,不同的体系在功用上的需求。功用需求的剖析,本文从体系带宽,采样率,到链路算法处理的杂乱度剖析下手。

2.1 无线通讯终端基带渠道的笼统架构

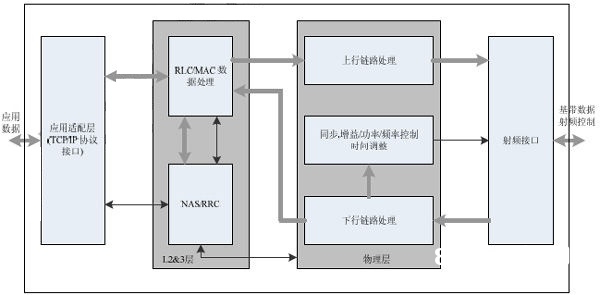

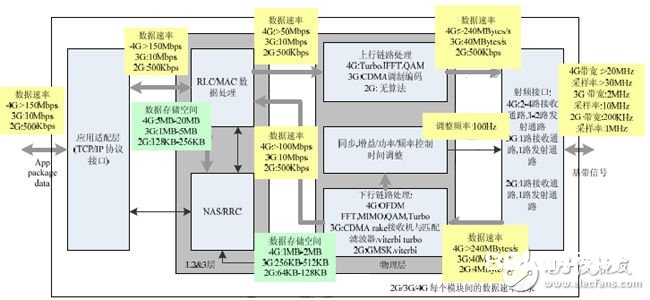

图2:无线通讯终端基带渠道的笼统架构

功用需求如上图2所示,一切的终端基带体系都需求完结:

● 跟射频信号的接口以及对射频电路的频率和增益的操控;

● 对上下行链路信号的处理,调制解调电路(或许算法),接纳均衡与解码电路(或许算法),对增益/频率/功率的环路操控;

● 对通讯链路的树立坚持开释等高层协议功用。

这些功用在不同的芯片上,构建不同的体系架构时,会有不同的软硬件的分工。

2.2 2G/3G/4G体系的功用需求

图3:2G/3G/4G体系功用需求示意图

2G 是以语音通讯为主的体系,3G是统筹语音通讯和数据通讯的体系,4G是以高速数据通讯为主体的体系。2G空中接口的带宽小于200khz,能供给几百 Kbps的数据流量;而3G带宽约2Mhz,供给几MBps数据流量;4G带宽高于20MHz,供给超越100MBps数据流量。2G和3G射频接口简略,1个接纳通道,1个发射通道,基带信号的采样率2G在1MHz左右(以4倍过采样为例),3G约10MHz;4G的射频接口有MIMO的形式,2–4个接纳通道,1–2个发射通道,且基带信号的采样率大于30MHz。体系的根底技能2G是GMSK调制方法和卷积码;链路处理算法简略,处理的数据量低;3G 是CDMA调制方法,卷积码加Turbo码,需求选用匹配滤波器和Turbo 解码等比较杂乱的算法,但处理的数据量还比较低;4G选用OFDM技能,卷积码加Turbo码,链路处理需求选用MIMO检测和Turbo解码等比较杂乱的算法,且处理数据量相关于2G和3G大幅度进步,高层协议栈也需求有较大的数据流量处理的技能。以此为体系功用需求的根底,能够剖析得到物理层的运算量 2G每秒低于50MOPS的需求量,3G约每秒小于500MOPS,4G超越5000MOPS。高层协议栈处理,2G约每秒10MOPS左右,3G每秒小于100MOPS,而4G超越1000MOPS。对缓存的数据区域的需求:2G物理层低于128KBytes,高层协议栈低于256Kbytes;3G物理层小于512KBytes,高层协议栈小于5Mbytes;4G物理层超越2MBytes,高层协议栈超越20Mbytes。

2.3 无线通讯终端基带渠道的需求剖析小结

综上所述,从2G到4G的终端基带渠道有着十分类似的体系功用架构,但因为体系带宽和根底技能的革命性改动,在功用需求上有着从量变到突变的腾跃。但相类似的功用架构,引导着架构规划者寻找一种能够统筹几个年代的终端基带渠道。本文所述的计划则是这样的一个渠道。

3. 依据定制方法的多模架构规划

因为4G的网络建造还需求一段时刻,4G终端芯片在架构规划时,需求考虑以多模的架构兼容2G/3G的需求,以便于终端在网络中移动时能够充沛的享受网络的资源。

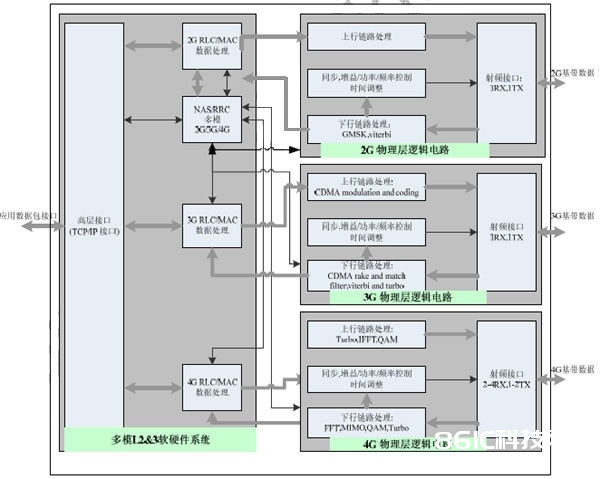

在 2G年代,传统的芯片架构规划计划将其间物理层的部分选用电路逻辑完结,高层协议则由一个可编程的内核电路来运转相应的软件。3G/4G年代,传统的思路是承继前者已有的电路,添加新的电路逻辑来完结物理层的部分,然后添加可编程内核的才能或许多个可编程内核来运转高层协议。所以,构成了如图4所示的传统多模架构。

图4:传统多模基带芯片架构

这种的架构的优点是,开发周期相对短,2G和3G的物理层现已安稳作业,但首要缺点是逻辑电路的面积也较大,然后导致芯片本钱较高。

4. SL3000体系架构介绍

SL3000芯片是精约纳依据对2G/3G/4G终端基带体系的了解,规划完结完结的一颗多模芯片。不同于定制电路(ASIC)的规划思路,SL3000的物理层选用散布式的多个向量处理器的架构,适用于2G/3G/4G多个不同的物理层算法运转;别的一个子体系也是由多个可编程的内核构成,以便于高层多模协议栈软件运转。这两个子体系独立运转在不同的时钟域,依据体系负载能够选用各自最合适的作业频率。

4.1 SL3000的体系框图

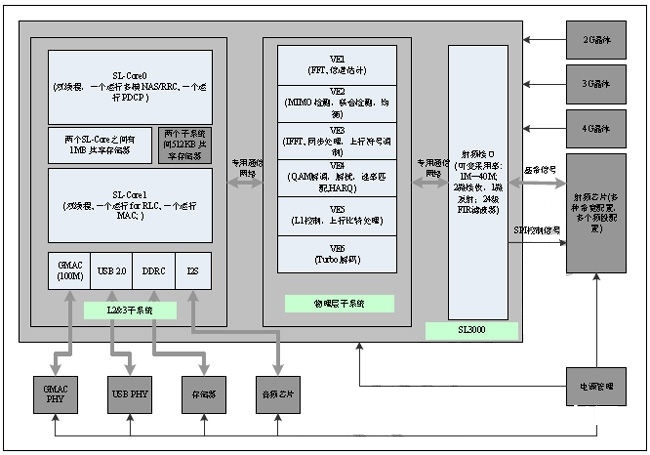

图5:SL3000的体系架构

4.2 SL3000子体系功用简介

如图5所示,SL3000内部分为两个大的子体系:L23子体系和PHY子体系。L23子体系由两个SL-Core构成,每个SL-Core子体系中有单独的Cache和RAM,以及DMA操控器和加解密模块。两个SL-Core之间有1Mbytes的同享内存。L23子体系还包含100M的GMAC操控器,USB2.0操控器,DDR 操控器等外设接口,为高速的数据通路供给接口。内核子体系与外设之间通过专有的网络互联互通。

图6:不同信号处理要求不同的矢量处理器结构

PHY子体系由6个VE(Vector Engine)构成。如图6所示,因为在不同的信号处理阶段,信号自身具有不同的特征,需求矢量处理器也具有不同的特征。

其间三个VE是并行处理16位位宽的数据处理器,适用于通讯链路中的I/Q数据处理的算法(例如均衡,匹配滤波,MIMO检测,FFT等等);一个VE是并行处理8位位宽的数据处理器,适用于通讯链路中的软符号的处理(例如QAM解映射,HARQ软兼并等算法);一个VE是并行处理1位位宽的数据处理器,适用于比特编解码算法(例如CRC核算,加解扰等);一个是Turbo解码器,适用于3G/4G中的Turbo码的处理。依照链路处理的需求,比特处理的 VE也承当整个物理层调度的功用,它能够通过特定接口拜访其他几个VE的内存空间,便利进行整个流程与时序的操控调度。其他几个VE两两之间有特定的通路进行通讯互联,以便于数据在多个VE之间依照流水线处理的环节天然流畅地传输。

RFIF接口模块能够习惯采样率从1MHz到 40MHz的规模,有两个接纳通路和一个发射通路,可灵敏处理有无MIMO的射频前端接口。一起RFIF模块内有可编程的基准时钟模块,能够通过改动外部输入PLL的基准时钟和时钟倍频参数,供给不同的2G或3G或4G的体系时钟。RFIF模块中有专门的DMA引擎,能够主动完结对外接口与内部存储器之间的数据传输。这儿的内部存储器包含了其间两个VE的内存空间和VE之间同享的一块专门的数据存储空间。这个专门的数据通路的规划,为基带数据的输入和输出供给了满意的带宽资源。

L23子体系与PHY子体系之间也通过专有的网络互联。且有一块特定的同享内存挂在这个网络上,L23 子体系的内核与DMA、PHY子体系的VE和DMA也都能够对此同享内存进行拜访。这个特定的网络通路和同享内存区域为L23子体系与PHY子体系之间进行很多数据传输供给了满意的带宽资源。

图7:依据SL3000构建多模终端参阅计划

图7表达了依据SL3000的架构,可构成多模终端的计划。RFIF接口可衔接一颗多频段多带宽可装备的射频芯片。语音能够走I2S接口与外部的语音处理芯片构成的通路,数据既能够走USB 接口也能够走GMAC接口。L23子体系有满意的才能运转多模的协议栈,PHY 子体系也有满意的才能运转多模的物理层软件。除了在上行和下行链路的部分直连总线外,没有杂乱的多核互连网络。这样建立的是一个简练的,低本钱低功耗的多模终端计划。

5. 多模运转功用陈述

这儿给出TD-SCDMA和TD-LTE两个体系在SL3000上运转的功用计算陈述作为参阅。因为整个链路处理的多个模块散布在不同的VE 上,在此对详细模块的散布计划不做详细的介绍,只给出整个链路运算的实践测验得到的功用数据自身。

5.1 TD-LTE的功用数据

5.1.1 物理层链路处理的功率

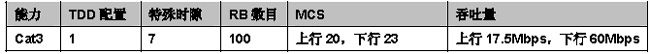

以上行峰值速率50Mbps,下行峰值速率100Mbps的处理为例,详细测验用例的参数如表2所示:

表2:测验用例参数

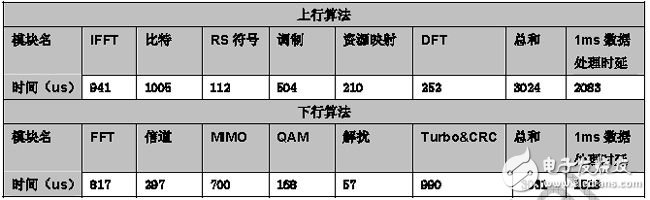

主频330MHz时,各个算法模块的每子帧数据处理所需的均匀时刻如表3所示:

表3:算法功率实测数据

TD- LTE整个上行1ms子帧的数据处理,需求92892cycles,即3024us@330MHz,整个下行链路处理花费1878110cycles,即 3031us@330MHz。因为一切的算法是散布在多个VE 上完结的,几个算法是能够并行处理的,全体1ms处理时延上行是2.083ms@330MHz,下行只要1.52ms@330MHz。在上下行装备为 SA17条件下,每5ms有两个上行子帧,三个下行子帧,上行吞吐量到达17.5Mbps,

下行吞吐量到达60Mbps,到达TD-LTE Cat3的上行峰值速率要求。

5.2 TD-SCDMA 的功用数据

关于TD-SCDMA体系的物理层,以上下行吞吐量别离为384kbps的处理为例,对其功用进行测验。详细测验用例的参数如表4所示:

表4:测验用例参数

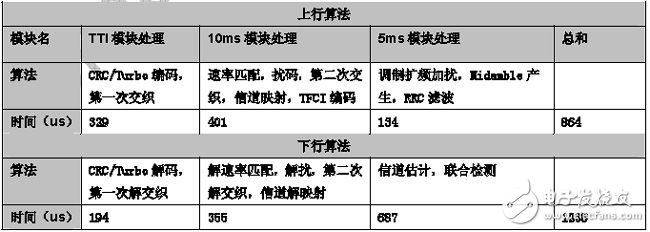

主频245MHz时,各个算法模块的每子帧数据处理所需的均匀时刻如表5所示:

表5:算法功率实测数据

TD- SCDMA整个10ms帧的时刻内,在上下行别离到达384kbps流量的条件下,整个上行链路处理花费207053cycles,即 864μs@245MHz,整个下行链路处理花费460376cycles,即1236us@245MHz。因为其间不同部分的算法散布在不同的VE上,实践上各个部分是能够并行运转的,真实一帧数据的时延上行小于864μs,下行小于1236μs的,用1/5的运算量就彻底满意实时性要求。

5.3 功耗与面积

现在的MPW样片选用65nm工艺,未运用功耗操控。在主频245MHz下,一切的内核与外设都全速运转,整颗芯片在峰值功耗在1.09W左右。 SL3000在65nm工艺流片,制品芯片的面积是79mm2。依据经历,如选用40nm或以下的工艺和低功耗规划,物理层规划进一步优化,无论是功耗仍是面积都会有较大的优化空间。估计面积在30mm2,功耗估计0.5W。

6. 小结

本文依据对 2G/3G/4G的需求剖析,介绍了一颗终端基带芯片SL3000的架构,以及依据SL3000 构建的多模终端参阅计划,并供给了在此芯片上完结的多模体系的运转功用。从各项测验数据和验证成果来看,SL3000是一颗具有多模功用,且满意 2G/3G/4G功用需求的基带渠道,能够比较灵敏地通过软件编程而完结多种无线通讯体系包含一些自定义的体系的终端。通过进一步的优化规划,其功耗和面积能够和同类多模AS%&&&&&%芯片适当,但SL3000具有更大的编程灵敏性,以习惯其它信号处理、如雷达、测验外表的需求。