前语: 高速数字体系规划成功的要害在于坚持信号的无缺,而影响信号无缺性(即信号质量)的要素主要有传输线的长度、电阻匹配及电磁搅扰、串扰等。

高速数字体系规划成功的要害在于坚持信号的无缺,而影响信号无缺性(即信号质量)的要素主要有传输线的长度、电阻匹配及电磁搅扰、串扰等。

高速数字体系规划成功的要害在于坚持信号的无缺,而影响信号无缺性(即信号质量)的要素主要有传输线的长度、电阻匹配及电磁搅扰、串扰等。

规划过程中要坚持信号的无缺性有必要凭借一些仿真东西,仿真成果对PCB布线发生指导性定见,布线完成后再提取网络,对信号进行布线后仿真,仿真没有问题后才干送出加工。现在这样的仿真东西主要有cadence、%&&&&&%X、Hyperlynx等。Hyperlynx是个简略好用的东西,软件中包括两个东西LineSim和BoardSim。LineSim用在布线规划前束缚布线和各层的参数、设置时钟的布线拓扑结构、挑选元器材的速率、确诊信号无缺性,并尽量防止电磁辐射及串扰等问题。BoardSim用于布线今后快速地剖析规划中的信号无缺性、电磁兼容性和串扰问题,生成串扰强度陈述,区别并处理串扰问题。作者运用LineSim东西,对信号的阻抗匹配、传输线的长度、串扰进行了仿真剖析,并给出了指导性定论。

阻抗匹配

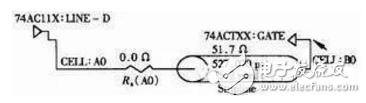

高速数字信号的阻抗匹配十分要害,假如匹配欠好,信号会发生较大的上冲和下冲现象,假如起伏超过了数字信号的阈值,就会发生误码。阻抗匹配有串行端接和并行端接两种,因为串行端接功耗低而且端接便利,实践工作中一般选用串行端接。以下运用Hyperlynx仿真东西对端接电阻的影响进行了剖析。以74系列树立仿真IBIS模型如图1所示。仿真时挑选一个发送端一个接纳端,传输线为带状线,设置线宽0.2mm和介电常数为4.5(常用的FR4资料),使传输线的阻抗为51.7Ω。设置信号频率为50MHz的方波,串行端接电阻Rs别离取0Ω、33Ω和100Ω的状况,进行仿真剖析,仿真成果如图2所示。

图中别离标出了匹配电阻是0Ω、33Ω、100Ω时接纳端的信号波形。从波形看出,0Ω时波形有很大的上冲和下冲现象,信号最差;100Ω时信号衰减较大,方波简直变成了正弦波;而匹配电阻是33Ω时波形较好。抱负的匹配电阻值,能够运用软件的terminatorWizard东西,主动依据器材的参数模型算出最佳匹配电阻为33.6Ω,实践运用中能够选用33Ω。运用仿真和器材的IBIS模型,能够很精确地知道匹配电阻值的巨细,然后使信号无缺性具有可控性。

图1 74系列仿真模型

图2 不同串行端接电阻的仿真成果

传输线长度的影响

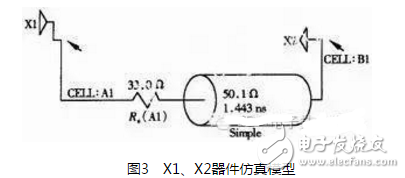

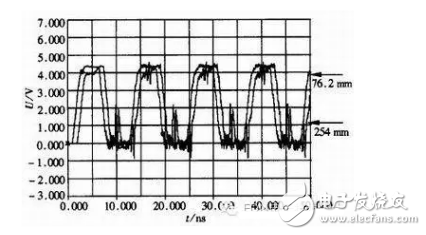

在高速数字电路的规划中,除了阻抗匹配外,部分器材对传输线的长度有着严厉的要求,信号频率越高,要求传输线的长度越短。以X1器材和X2器材为例树立仿真模型如图3所示。在仿真模型中加了33Ω的匹配电阻,挑选仿真信号频率为66MHz方波,改动传输线长度别离为76.2mm和254mm时进行仿真。仿真成果如图4所示。

图4 不同长度传输线仿真成果

从图中看出,信号线加长后,因为传输线的等效电阻、电感和%&&&&&%增大,传输线效应显着加强,波形呈现振动现象。因此在高频PCB布线时除了要接匹配电阻外,还应尽量缩短传输线的长度,坚持信号无缺性。

在实践的PCB布线时,假如因为产品结构的需求,不能缩短信号线长度时,应选用差分信号传输。差分信号有很强的抗共模搅扰才能,能大大延伸传输间隔。差分信号有很多种,如ECL、PECL、LVDS等,表1列出LVDS相关于ECL、PECL体系的主要特点。LVDS的恒流源形式低摆幅输出使得LVDS能高速驱动,关于点到的衔接,传输速率可达800Mbps,一起LVDS低噪声、低功耗,衔接便利,实践中运用较多。LVDS的驱动器由一个一般为3.5mA的恒流源驱动对差分信号线组成。接纳端有一个高的直流输入阻抗,几科悉数的驱动电流流经10Ω的终端电阻,在接纳器输入端发生约350mV电压。当驱动状况回转时,流经电阻的电流方向改动,此刻在接纳端发生有用的逻辑状况。图5是运用LVDS芯片DS90LV031、DS90LV032把信号转换成差分信号,进行长间隔传输的波形图。在仿真时设置仿真频率为66MHz抱负方波,传输间隔为508mm,差分对终端接100Ω负载匹配传输线的差分阻抗。从仿真成果看,LVDS接纳端的波形除了有推迟外,波形坚持无缺。

表1 LVDS、ECL、PECL逻辑规范对照表

图5 LVDS电路仿真成果

串扰剖析

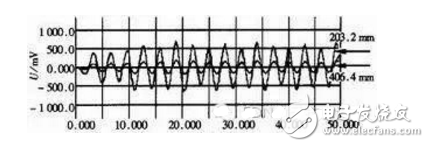

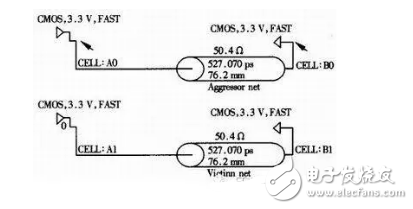

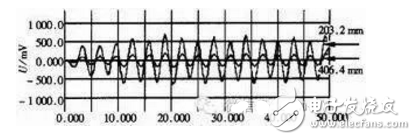

因为频率的进步,传输线之间的串扰显着增大,对信号无缺性也有很大的影响,能够经过仿真来猜测、模仿,并采纳办法加以改进。以CMOS信号为例树立仿真模型,如图6所示。在仿真时设置搅扰信号的频率为66MHz的方波,被搅扰者设置为零电平输入,经过调整两根线的距离和两线之间平行走线的长度来调查被搅扰者接纳端的波形。仿真成果如图7,别离为距离是203.2mm、406。4mm时的波形。

图6 串扰模型

图7 不同距离的串扰仿真成果

从仿真成果看出,两线距离为406.4mm时,串扰电平为200mV左右,203.2mm时为500mV左右。可见两线之间的距离越小串扰越大,所以在实践高速PCB布线时应尽量拉大传输线距离或在两线之间加地线来阻隔。

在高速数字电路规划中,不必仿真而只凭传统的规划办法或经历很难猜测和确保信号无缺性,仿真已成为高速信号规划的必要手法,运用仿真能够猜测信号的传输状况,然后进步体系的可靠性。