大容量数据收集与存储体系在工业主动化出产、国防和军事监控及环境监测等方面被广泛使用。为了可以完好、精确地捕获到各种信号或许毛病发生时的特征信号,需求对其进行状况监测,而且要求监测体系具有长期接连收集和存储的功用。可是为了支持体系中很多高速数据的暂时存储,这就需求很大的中心缓存,而专用的高速FIFO芯片价格昂贵且容量受限,大大增加了商业本钱,因而在实践使用中寻觅牢靠的、低本钱的收集存储体系是很有必要的。为此本文提出使用FPGA作为桥梁,完结对SDRAM的操控,然后对收集的数据进行缓冲,然后存储到大容量的CF卡中,满意体系所要求的速度快、实时性高、本钱低和简单扩展等要求;接着详细论说了体系各个功用电路的规划思路和详细完结进程。

1体系方案规划

数据收集和存储体系首要由三部分组成:A/D转化器、FPGA的数据双缓冲器和CF卡的存储。

1)A/D转化器的效果是将所要收集的模仿量转化成数字量,经过光耦阻隔后,由FPGA接纳、缓冲、存储至CF卡。高速A/D转化器选用的是采样率为250kS/s的16位A/D转化芯片ADS8515,它归于逐次迫临寄存器型(简称SAR型)A/D转化器,其内部一般具有采样坚持器,转化速率快。

2)FPGA选用ALTERA公司CycloneⅡ系列的EP2C35F672I8N,静态功耗小于0.25W。选用+3.3V、+2.5V、+1.2V分别给不同区进行供电。灵敏的I/O操控使得编程简化,电路规划便利。选用AS和JTAG装备形式,装备芯片是EPCS16SI8N,器材的时钟装备为50MHz。

FPGA首要使用片外的SDRAM供给数据输出/输入的双缓冲效果,之所以选取SDRAM,首要是因为在各种随机存取器材中,SDRAM的容量较大,价格较低,且其数据突发传输形式能大大提高存取速度,可以满意使用的要求。

3)CF卡效果是将A/D收集到的数据进行存储,当数据容量存储满时,发送满信息,FPGA得到满信息后,中止对数据的收集并提示用户替换CF卡。

体系作业进程为:体系加电后,FPGA向A/D转化器宣布相应操控信号,因为ADC采样率为250kS/s,为和CF卡存储速度相匹配,需求一个FIFO缓存体系。A/D转化器在FPGA的ADC接口操控电路操控下,把模仿信号转化成数字信号,并将采样数据存入FIFO缓存体系。一起FPGA查询CF卡是否有容量,假如CF卡未满,那么由FPGA的CF卡接口操控逻辑将采样成果从FIFO缓存送入CF卡中;当CF卡的容量到达必定程度后,FPGA宣布满信息,向A/D状况机发送中止收集的指令,并提示用户已满,替换CF卡。

因为把FPGA设置为特定的主动形式,因而FPGA操控A/D收集以及把数据送往CF卡的一切操作不需求外部干涉,然后确保满足的数据传输速率。采样进程中FPGA的CF卡接口操控逻辑顺次取走FIFO中的批量数据,在进行CF卡的数据存储时A/D依然持续转化,FIFO也被持续写入转化成果,防止两者的抵触。

2硬件规划

体系的硬件由模数转化电路、数据收集存储与传输操控电路、接口电路构成。

2.1模数转化电路规划

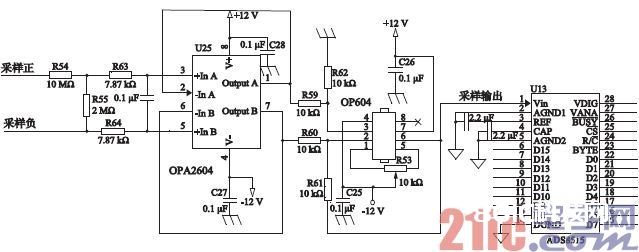

模数转化电路是整个体系的重要组成部分,它由差分扩大适配电路、A/D转化器构成,如图1所示,其间心器材是A/D转化芯片ADS8515。

图1 信号适配和模数转化电路原理图

模仿输入信号经过由OPA2604和OP604构成的差分扩大适配电路将信号适配到ADS8515的收集规模。ADS8515将模仿信号转化为数字信号。ADS8515的操控信号由FPGA供给,ADS8515在操控信号的效果下,以恰当的时序完结转化作业。

2.2数据收集存储与传输操控电路规划

数据收集存储与传输操控电路的开发作业首要会集在FPGA上。FPGA担任在CF卡与A/D芯片之间的缓冲与操控,一边与A/D接口,另一边与CF卡接口,发生数据收集、A/D转化、FIFO所需的悉数操控信号,完结对传输数据的缓存、读/写操控、时钟、输出使能以及对A/D的操控等功用。

2.2.1FPGA内部总体规划

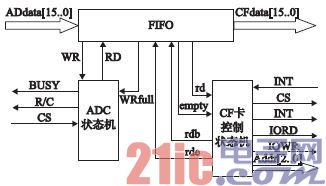

FPGA规划内部结构简图如图2所示,由FIFO、CF卡操控状况机、ADC接口操控状况机三部分构成。

图中由左向右的宽箭头表明数据流,ADdata[15..0]是与A/D转化衔接的数据总线,CFdata[15:0]是与CF卡衔接的数据总线。单线箭头表明输入输出及FPGA内部各个模块间的操控信号线。从数据流向看,数据在ADC接口操控状况机的协调下经过ADC接口送入FIFO中,经过FIFO的缓冲后,在CF卡操控状况机的协调下,数据传输存储到CF卡;当CF卡存储满时,FPGA经过ADC状况机中止A/D的收集,并提示用户替换CF卡。

2.2.2数据双缓存器FIFO

因为与CF卡接口的数据传输办法是突发的数据块传送,每个数据块是用很高的速率传送到CF卡,这样就必须有缓存把A/D收集来的数据先缓存,然后发送到CF卡进行存储。但是FPGA内部的FIFO不足以支持体系中很多数据的暂时存储,这就要求很大的中心缓存。在本体系中使用FPGA对外部SDRAM的操控,以到达很多高速存取数据的功用。SDRAM选用M%&&&&&%RON公司的MT48LC4M32B2,存储容量为128MB,数据带宽为32位,内部由4个BANK组成,每个BANK有4096行和256列。

图2 数据收集与传输操控结构示意图

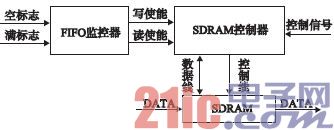

本文规划的FIFO体系由FPGA和SDRAM两部分组成。其间FPGA内部包括FIFO监控器、缓冲器、SDRAM操控器三个模块。FIFO监控器的效果是将SDRAM的状况转变成SDRAM操控器的读、写信号。若操作为向SDRAM写数据,则在SDRAM满时,FIFO监控器送出一个信号,以阻挠写操作持续向SDRAM中写数据而形成溢出;若操作为向SDRAM读数据,则在缓冲器已空时,FIFO监控器送出一个信号,以阻挠读操作持续从SDRAM中读数据而形成无效数据的读出。FIFO体系的模块结构如图3所示。

图3 FIFO模块结构示意图

2.3接口电路规划

2.3.1FPGA内ADC接口模块的规划

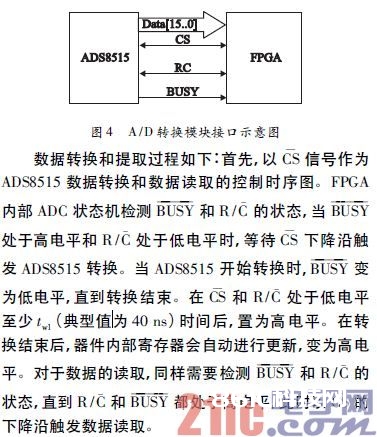

对A/D转化器的编程,首要是FPGA对ADS8515的操控信号进行写逻辑,其接口示意图如图4所示。

图4 A/D转化模块接口示意图

2.3.2FPGA内CF卡接口操控状况机的规划

CF卡有三种拜访办法,分别为I/O形式、Memory形式和TrueIDE形式。本体系选用TrueIDE形式拜访CF卡。需求在电源加电启动时将OE接地,见图5,让CF卡作业在TrueIDE形式。当CSEL输入信号接地时,CF卡作业办法为主形式;CSEL输入信号接高电平时,CF卡作业办法为从形式。本体系中将CF卡装备成从形式作业办法。当选用TrueIDE拜访形式作业时,第3位到第10位地址线接地,WE信号接高电平。

图5 FPGA与CF卡接口示意图

3软件规划

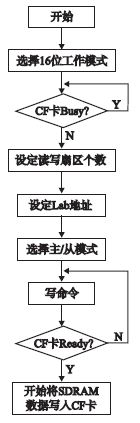

CF卡的数据存储以扇区为基本单位。体系向CF卡写入一个扇区的数据,如图6所示。首要依据操控指令设定16位作业形式,设置将写入的扇区数目、相应地址和拜访形式,然后发送写指令,等候CF卡准备就绪后,从数据缓冲区SDRAM写入CF卡中。

图6 向CF卡写数据流程图

4结束语

根据FPGA的高速大容量低本钱数据收集体系以FPGA作为桥梁,操控片外高速SDRAM缓冲器,以CF卡作为大容量存储介质,既使用了FPGA的内部资源丰富和规划便利的长处,一起使用了CF卡容量大、体积小和价格低廉等长处,给出了高速大容量数据收集的办法,该办法已成功使用于实践体系中。