规划CPU需求许多技巧和尽力。拿到一个CPU规划并下降其50%的动态功耗需求一系列特别的技巧,这也是CPU规划人员绵长职业生涯的要取得的技能之一。

在成功推出第一款PowerVR Rouge GPU的DOK后,Imagination和Synopsys打开第二个项目协作,旨在不献身任何功能抢先数字的前提下明显下降MIPS处理器的功耗。

动态功耗是SoC规划人员中一个抢手的(请原谅这个双关语)论题

下降动态功耗是许多体系芯片规划人员现在面对的一大应战。对可归纳IP来说现在有各种不同的挑选和考虑要素。同一IP能够运用在不同商场中的林林总总运用中。最重要的是,工艺、东西和流程是额定需求考虑的应战。

功能、功耗和面积(PPA)的权衡取舍不同,依赖于不同的工艺,也依赖于客户的完结要求。

Synopsys公司最近安排的一期研讨会一文总结了来自于Imagination公司的Maya Mohan和NageshSakhamuru提出的一些选项,可用于Synopsys东西与流程运用28nm技能的情形下。

其首要方针是运用特定的工艺和各子库计划与Synopsys东西和流程结合的时分,介绍给SoC规划人员能够节约动态功耗的各个方面。作者把许多要点放动态功耗相关于走漏功耗上,并给出了特定技能库IP挑选时每一过程和流程阶段相应的功耗下降状况。

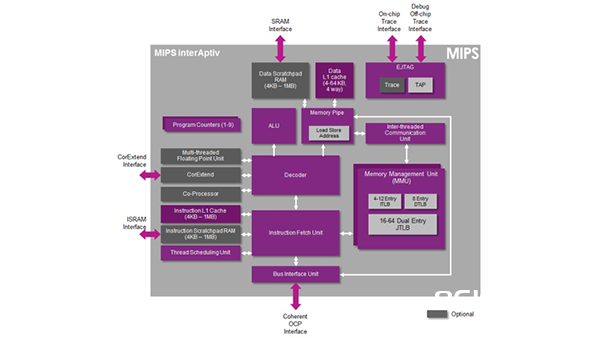

这个项目中CPU挑选的是MIPS interAptiv,它归于Aptiv宗族,是一个超高效的多线程处理器。在一般状况下,CPU希望以最高功能运转,一起坚持动态功耗尽可能地低。但是,以峰值功能运转也可能会添加动态功耗;这就引发了需求寻觅办法在持续功能与下降功耗之间取得平衡。

动态功耗有多个部件

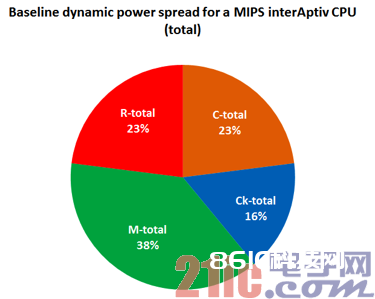

您能够在一个CPU中心找到各种动态功耗部件,符号如下:存储器(M-Power),指令和数据高速缓存,寄存器(R-power),叶级的时钟门控和非门控的寄存器,时钟网络单元(Ck-power),时钟门控和缓冲区以及组合单元(C-power)。

功耗部件符号: Ck:时钟, R: 寄存器, M: 存储器, C: 组合电路

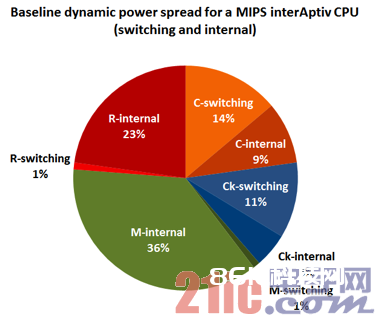

关于每个以上四个分类,又细分为两个子部件:内部功耗和开关功耗。每一部分都被独自剖析,并且在每次动态功耗优化时各种选项也都会被考虑。

基线版别动态功耗的内部和开关子部件散布状况

归纳在DCT/ DCG中进行,而布局布线则在ICC中履行。两个阶段都丈量了功耗:DCT后期以及ICC后期。根据一致性考虑,研讨会一切陈述的功耗数据都取自ICC后期数据库,通过门级仿真的开关行为取得。参数提取由StarRC完结,Dhrystone确诊在门仿真时被运用,PT-PX用于功耗丈量。

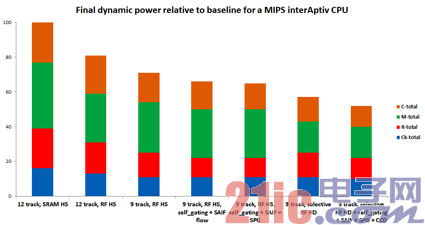

上图显现了MIPS interAptiv CPU的总动态功耗的各个子部件。这个基线版别被用于其它办法和试验进行比较的目标。

一般动态功耗运用mW/ MHz丈量,但关于本项目,基线版别运转的总功耗被归一化为100,其它版别的运转功耗根据这一数字得出。

正如从上图中所看到的,时钟功耗只点总功耗的约16%。从这儿的图表中,咱们不难看出,功耗的最大顾客是内部存储器和寄存器,以及组合逻辑的开关功耗:

•开关功耗正比于开关%&&&&&%巨细和切换次数。为了进步寄存器和组合逻辑的功耗水平,在DCT中大部分优化运用了根据RTL的SAIF与自我门控技能。在ICC中各种动态功耗下降特性也在网络研讨会中进行了讨论,以及运转终究阶段的新CCD(并行时钟和数据)特性。

•内部功耗正比于单元的数目、单元巨细和切换次数。下降寄存器的内部功耗可通过替换为较小尺度的单元以及下降切换次数。也能够运用更低轨迹的工艺库(例如,从12轨迹转化至9轨迹)供给了相关于功能和面积下降功耗的另一种折衷。内部存储器的功耗首要归因于所挑选的巨细或存储器类型。Synopsys的存储器编译器有多种内存可供挑选。笔者挑选了一个根据RF的组合,结合了高功能以及高密度的单端口存储器,这种组合一般用于平衡(高效的)功耗/功能需求。

十分令人激动的成果!

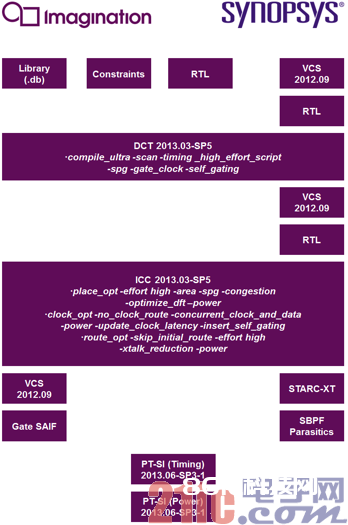

一切上述特性和技能的结合在一起明显下降了功耗。下面的流程图描绘了Synopsys的归纳东西和%&&&&&%C中所运用的终究东西选项:

终究流程图

在项目结束时,总功耗下降了约48%,面积削减了46%,而价值为只下降了CPU15%的功能体现。

相关于12轨迹、SRAM的基线版别一切运转版别优化动态功耗后的体现

上表显现了一切上述试验和相应功耗;要检查完好成果,请下载彻底白皮书,下载后您会看到这个过程中每一过程对应功耗和面积的削减。