HMC6832相关信息来自ADI官网,详细参数以官网发布为准,HMC6832供给信息可在查IC网查找相关供给商。

产品概况

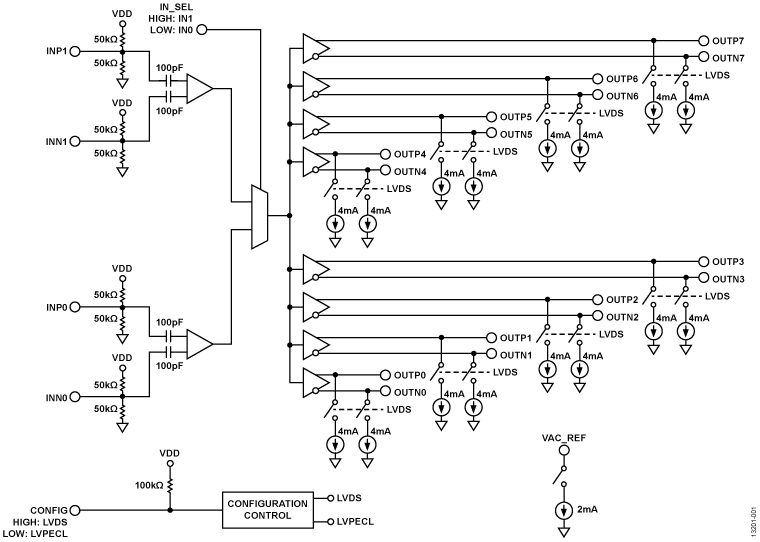

HMC6832是一款可选输入、2:8差分扇出缓冲器,针对低噪声时钟分发而规划。HMC6832使用低颤动输出完成下流电路的低噪声同步切换,如混频器、模数转化器(ADC)/数模转化器(DAC)、或串行器/解串器(SERDES)器材。该器材可以完成低压正发射极耦合逻辑(LVPECL)或低压差分信号(LVDS)装备,办法是针对LVPECL拉低CONFIG引脚,或许针对伪LVDS拉高或翻开(内部拉高)该引脚。

产品聚集

- 多种输出装备。CONFIG引脚答使用户挑选LVPECL或LVDS输出端接

- 多个电源电压供电。HMC6832 LVPECL端接时选用2.5 V或3.3 V作业(LVDS时仅为2.5 V)。

- 低噪声。HMC6832具有−168 dBc/Hz至−162 dBc/Hz的低噪声(典型值,最高3000 MHz)。

- 低传达推迟。HMC6832显现了小于207 ps(典型值)的低推迟。它还具有±5 ps(典型值)的低通道偏斜。

- 低内核电流。HMC6832具有56 mA(典型值)的低内核电流。

使用

- SONET、光纤通道、GigE时钟分发

- ADC/DAC时钟分发

- 低偏斜和颤动时钟

- 无线/有线通讯

- 电平转化

- 高性能仪器仪表

- 医疗成像

- 单端至差分转化

优势和特色

- 超低噪底:−165.9 dBc/Hz或−165.2 dBc/Hz(LVPECL或LVDS,2000 MHz)

- 可装备为LVPECL或伪LVDS输出

- 2.5 V或3.3 V LVPECL作业电压(LVDS仅为2.5 V)

- 宽带:作业频率规模:10 MHz至3500 MHz

- 灵敏的输入接口

- LVPECL、LVDS、CML和CMOS兼容

- 沟通或直流耦合

- 片上端接高阻抗50 kΩ分流电阻至VDD和GND

- 多个输出驱动器

- 多达8个差分或16个单端LVPECL或LVDS输出

- 经过IN_SEL和CONFIG引脚完成低速数字控制

- 28引脚、5 mm × 5 mm、LFCSP封装、25 mm2

HMC6832电路图

HMC6832中文PDF下载地址

HMC6832下载链接地址:https://www.analog.com/media/en/technical-documentation/data-sheets/hmc6832.pdf