nightvista 视频编码器 混合逻辑 cycloneintevac是商用和军用商场光学产品的前沿开发商。本文介绍该公司nightvista嵌入式电子体系的开发,该产品是高功用超低亮度紧凑型摄像机。该摄像机开端选用了盛行的数字信号处理器、几个assp和外部存储器材。体系对功用的需求越来越高,工程师团队决议实验一种代替计划——在可编程逻辑中完结可装备软核处理器。这一决议带来了以下优点:

- 到达了方针所要求的功用

- 在单个fpga中集成了分立的元件和数字信号处理(dsp)功用

- 功耗降低了近80%

- 将五块元件板缩减到一块,显着降低了本钱

- 缩短了开发时刻

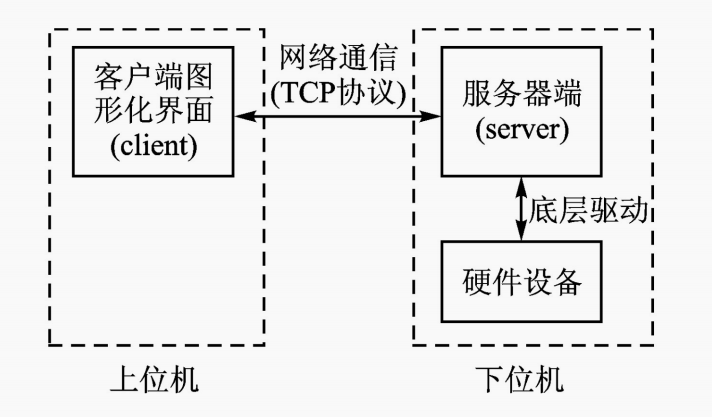

图1 intevac nightvista摄像机中cyclone系列fpga功用框图

dsp根据处理器的完结办法

nightvista电子体系的部分功用包含:

- 摄像机上电测验和初始化

- 视频传感校准和表征

- 图画增强办理的自动增益操控

- 图形、文本和水印屏显现功用

- 实时自适应对比度调整

- gamma校对、视频停帧捕获,并存储至闪存

- 实时时钟

- 用户界说的可编程预置装备

- 经过rs-232与主机pc进行通讯

- 摄像机功用和参数长途更新,摄像机至主机pc视频数据传送

intevac开发nightvista电子产品的开端办法是选用数字信号处理器。除了处理器之外,还需求其他几个首要部件,包含ntsc视频编码器、一个rs-232接口、多个锁相环(pll)、完结各种逻辑功用的cpld,以及几个存储器(fifo、sdram和闪存)。此外,这些部件需求四个不同的作业电压(需求四个电源稳压器和不同的pcb板层),四个独立的时钟体系,以及各自的振荡器和电源去耦电路。总体上,这些部件占用了五块pcb,每一块电路板大约两平方英寸,堆叠在该摄像机两英寸见方的外壳中。

硬件开发了几个月之后,我们清楚的认识到该处理计划难以到达intevac为nightvista设定的功用方针,分量和功耗令人难以承受。并且,因为高密度堆叠的pcb功耗很大,带来了显着的热办理问题。intevac决议中止根据数字信号处理器的规划,转而选用根据fpga的混合逻辑和软核微处理器计划。intevac并没有运用集成微处理器可编程逻辑的经历,可是一个运用altera演示板的评价计划很有吸引力,其最新的低本钱fpga可以将一个完好的32位risc处理器和存储器模块、pll以及很多的逻辑资源集成到一同,完结专用视频信号处理功用。在fpga中集成pll可以处理与电路板级多时钟体系相关的很多问题。

工程师团队考虑了多种要素,包含:

- 多种fpga系列的功用和特性

- 供给知识产权(ip)内核

- 多个供货商的器材集成技能和事务才能

- 供给老练的硬件和软件开发工具

- 供货商支撑资源的可靠性

剖析了以上要素后,公司决议购买在altera cyclone fpga中完结altera nios处理器的处理计划。fpga的功用如图1所示。

规划转化

决议运用altera的处理计划后,intevac有必要确认现有的dsp软件在多大程度上可以导入到nios处理器中。公司现已投入了18个月的人工支付进行前面的数字信号处理器软件开发,团队现在面对的问题是将图画数据经过处理器传送至输出,并没有进行视频处理。fpga摄像机中的nios处理器具有不同的特性,只能经过rs-232串行通讯协议与主机pc和视频传感器进行通讯。走运的是,nios处理器的软件开发直观明晰,经过运用nios开发板,intevac在几个小时之内便建立了处理器和主机pc之间的通讯。

新的fpga电路板在一个月内完结,在这段时期内,intevac持续选用nios处理器开发板编写、调试软件代码。intevac开端计划选用数字信号处理器的实时操作体系(rtos)来办理杂乱的视频处理算法时序。因为nios处理器并不包含现成的rtos,软件小组并不能确认是否可以到达一切的时序要求。与硬件小组讨论后,软件小组很快发现nios处理器的装备功用可以很好的操控信号时序,一般只需求对fpga规划稍做改动便可以到达方针时序要求。同一fpga环境下硬件和固件处理具有高度集成特性,可以敏捷简略的完结最佳操控和视频处理使命。

fpga计划完结了定制化,提升了功用

进一步的深入研讨后,intevac开端开发定制功用和外设,以靠近自己的需求。一旦在软件中碰到瓶颈,硬件小组便开发一个处理器来进步功用,一般在一个小时内就可以做到这一点。硬件小组规划了一个定制视频编码器、用于缓冲视频数据的fifo模块,以及专用dma操控器为编码器供给安稳的视频数据流,避免了运用外部编码器和fifo缓冲。此外,构建了一个定制sdram操控器,使一切的视频、特点、nios处理器指令读取和数据存储都可以运用同一存储器,然后进步了功用。某些功用需求自己的时钟,因而,选用了fpga的板上pll,从一个主时钟中发生三个不同的时钟:第一个用于视频编码器,第二个用于sdram时序,第三个用于外部象素传感器。

经过集成进步了功用

在完结了曾经所用外部器材的功用往后,intevac还增加了开端dsp处理器无法完结的功用。参加了视频测验形式生成器来仿真摄像机的作业,使软件小组可以完结各种视频处理算法,使体系可以和谐作业。参加的另一功用是计算生成器,用于剖析视频数据的特性,以便进行图画增强和亮度处理。图画计算生成器需求的数学运算如果在软件中完结,那么速度很慢。intevac运用了fpga中的逻辑资源来完结该功用,设置完结后,将成果传送给处理器。

电路板制好后,在几个小时内便完结了开发板软件代码传送、代码设置,并在新板上运转。后边的几个月中,intevac在进行硬件和软件开发的一起,进一步调试、优化了规划。尽管对处理器和fpga规划的其他部分进行了屡次修正,可是,并没有影响电路板布板。最终,运用cyclone器材和nios软核处理器,将五块电路板缩减为一块。这种集成方法减轻了摄像机分量,所需支撑电压由四个削减到两个,功耗降低了近80%。运用相同的pcb设置,intevac还可以高效的出产多种产品。

选用altera无铅产品轻松到达rohs

altera在业界供给的无铅产品规模最广,1200多个产品具有无铅封装。altera作为环境无污染可编程逻辑处理计划的优异供货商,2002年以来现已出售了2千5百万片无铅产品。altera的无铅器材契合eu directive在有害物质运用约束(“rohs directive”)no.2002/95中所规则的最大浓度值,包含铅(pb)、汞、镉、六价铬、多溴化联苯(pbb)以及多溴化联二苯(pbde)等。选用altera的pld集成非兼容的assp功用,可以轻松完结您的rohs转化。

结语

规划简化后,intevac到达了自己的功用方针,极大的降低了元件和出产本钱,进步了nightvista的质量和可靠性。在开端的产品标准基础上,该处理计划还增加了更多的功用。intevac在fpga中留出了逻辑资源,这样,现场应用时,可以进一步对摄像机进行更新。这一处理计划协助intevac研讨并完善了速度更快、功率更高的规划开发流程,为往后的产品开发节省了很多的时刻和资源。