体系时钟操控逻辑,在S3C6410 中生成所需的体系时钟信号,用于CPU 的ARMCLK, 用于AXI/AHB 总线外设的HCLK 和APB 总线外设的PCLK。在S3C6410 中有三个PLL。一个仅用于ARMCLK,一个用于HCLK 和 PCLK,最终一个用于外设,特别用于音频相关的时钟。The third thingis for peripheral, especially for audio related clocks.经过外部供给的时钟源,时钟操控逻辑发生慢速时钟信号ARMCLK,HCLK 和 PCLK。该每个外设块的时钟信号或许被启用或禁用,由软件操控以削减电源耗费。

在电源操控逻辑中,S3C6410 有多种电源办理计划,以坚持电力体系的最佳耗费。In the power control logic, S3C6410X has various power managementschemes to keep optimal power consumption for a given task.

1、在S3C6410中,通用时钟门控形式用来操控内部外设时钟的开/关。能够经过用于外设所要求的特定运用供给时钟,运用通用时钟门控形式来优化S3C6410的电源耗费。例如:假如定时器没有要求,则能够中止时钟定时器,以降低功耗。General Clock Gating mode is used to control the ON/OFF of clocksfor internal peripherals in S3C6410X. You can optimize the power consumption ofS3C6410X using this General Clock Gating mode by supplying clocks for peripheralsthat are required for a certain application. For example, if a timer is notrequired, then you can disconnect the clock to the timer to reduce power.

2、搁置形式仅中止ARMCLK到CPU 内核,它供给时钟给一切外设。经过运用搁置形式,电力耗费经过CPU

内核而削减。

3、中止形式经过禁用PLL冻住一切时钟到CPU 以及外设。在S3C6410 中,电力耗费仅由于漏电流。

4、睡觉形式断开内部电源。因而,除了唤醒逻辑单元耗费的电量,CPU和内部逻辑耗费电量将为零。为了运用睡觉形式,两个独立的电源是必需的。其间一个电源为唤醒逻辑供给电力,另一个供给其他内部逻辑,包括CPU。SLEEP mode disconnects the internal power.Therefore, the power consumption due to CPU and the internal logic except thewakeup logic will be zero. In order to use the SLEEP mode two independent powersources are required. One of the two power sources supplies the power for thewake-up logic. The other one supplies the other internal logic including CPU,and must be controlled in order to be turned ON/OFF. In SLEEP mode, the secondpower supply source for the CPU and internal logic will be turned off.

3.1 体系操控器的特性

The System Controller includes the following features:

• Three PLLs: ARM PLL, main PLL, extra PLL (for the modules those usespecial frequency)

• Five power-saving mode: NORMAL, IDLE, STOP, DEEP-STOP, and SLEEP

• Six controllable power domain: domain-G, domain-V, domain-I,domain-P, domain-F, domain-S

• Control operating clocks of internal sub-blocks

• Control bus priority

3.2 功用描绘

这部分首要介绍S3C6410 体系操控器的功用。包括时钟的体系结构,复位规划和电源办理形式。

1、硬件结构

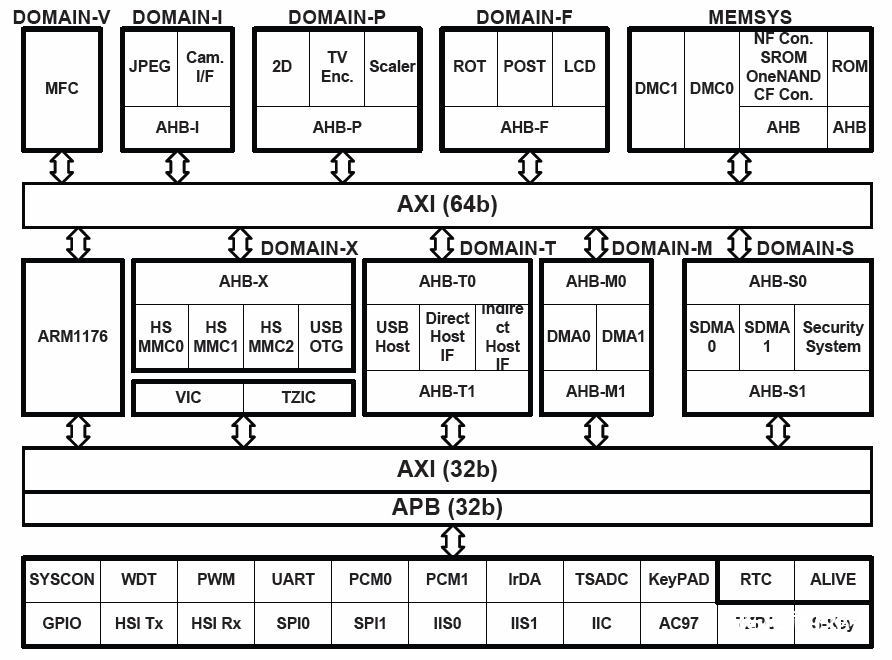

S3C6410是由ARM1176核、一些多媒体协处理器(co-processors)、多种外设IPs组成。ARM1176核是经过64位AXI总线与存储操控器相连的,这样做是为了满意带宽的需求。多媒体协处理(MFC多格局编码器、JPEG、camera接口、TV译码器、3D加速器等)器被分为五个电源域,这五个电源域可被独自操控以下降功耗。S3C6410X consists of ARM1176 processor, several media and graphicco-processors and various peripheral IPs. ARM1176 processor is connected toseveral memory controllers through 64-bit AXI-bus. This is done to meetbandwidth requirements. Media and graphic coprocessors, which include MFC(Multi-Format Codec), JPEG, Camera interface, TV encoder, 3D accelerator and etc,are divided into six power domains. The six power domain can be controlledindependently to reduce unwanted power consumption when the IPs is not requiredfor an application program.

2、时钟结构

时钟源在外部晶振和外部时钟二者之间进行挑选。时钟发生器由三个PLL组成,最高可发生1.6GHz的信号。

3.时钟源的挑选

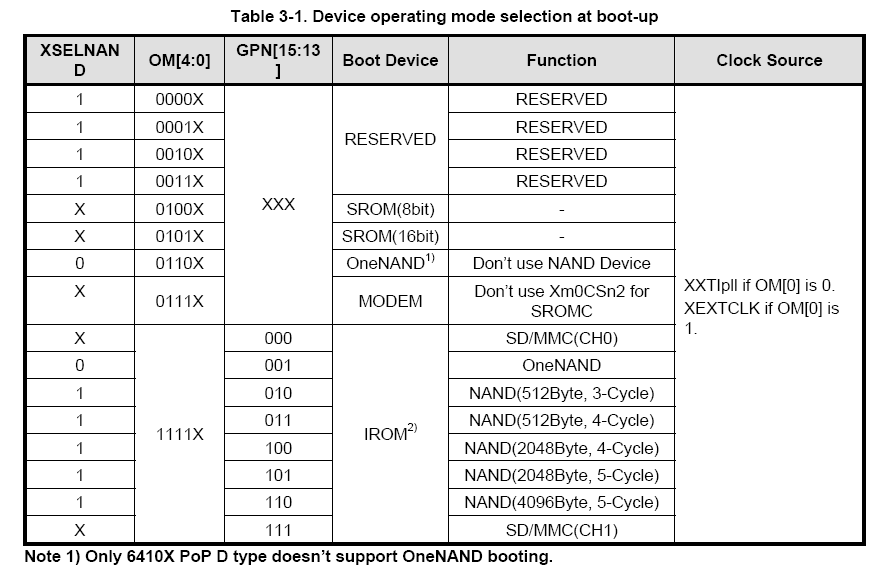

The OM[4:0] pins determines theoperating mode of S3C6410X when the external reset signal is asserted. Asdescribed in the table, the OM[0] selects the external clock source, i.e., ifthe OM[0] is 0, the XXTIpll (external crystal) is selected.

Otherwise, XEXTCLK is selected.

The operating mode is mainlyclassified into six categories according to the boot device. The boot devicecan be among SROM, NOR, OneNAND, MODEM and Internal ROM. When NAND Flash deviceis used, XSELNAND pin must be 1, even if it is used as boot device or storagedevice. When OneNAND Flash device is used, XSELNAND must be 0, even if it isused as boot device or storage device. When NAND/OneNAND device is not used,

XSELNAND can be 0 or 1.

4、锁相环

Clock selection betweenPLLs and input reference clock

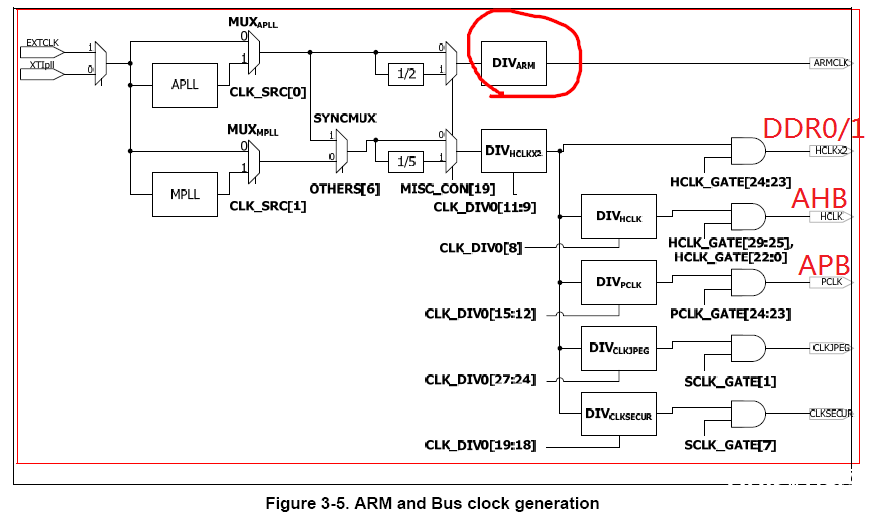

Figure 3-4illustrates the clock generation logic. S3C6410X has three PLLs which are APLLfor ARM operating clock, MPLL for main operating clock, and EPLL for specialpurpose. The operating clocks are divided into three groups. The first thing isARM clock, which is generated from APLL. MPLL generates the main system clocks,which are used for operating AXI, AHB, and APB bus operation. The last group isgenerated from EPLL. Mainly, the generated clocks are used for peripheral IPs,i.e., UART, IIS, I%&&&&&%, and etc. The lowest three bits of CLK_SRC registercontrol the source clocks of three groups. When the bit has 0, then the inputclock is bypassed to the group. Otherwise, the PLL output will be applied tothe group.

1)ARM和AXI/AHB/APB时钟

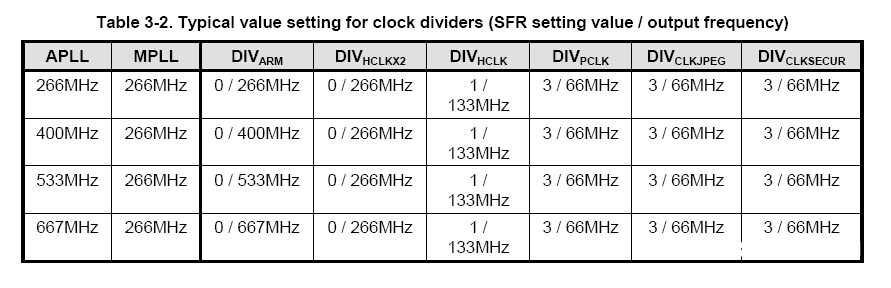

ARM1176最大支撑667MHZ,在不改动PLL的情况下,能够经过DIVarm来操控该频率。

S3C6410由AXI、AHB、APB总线组成。IPs能够衔接相应总线来满意I/O带宽和操作功能。衔接在AXI/AHB的总线上的设备,最高能够到达133MHz的速度。当衔接在APB总线上时,最高能够到达66MHz的速度。总线速度很高程度上依赖于AHB和APB总线之间的同步数据传输。

ARM and AXI/AHB/APB bus clock generation

ARM1176 processor of S3C6410X runs up to maximum 667MHz. Theoperating frequency can be controlled by the internal clock divider, DIVARM,without changing PLL frequency. The divider ratio varies from 1 to 16. ARM processordecreases the operating speed to reduce power dissipation.S3C6410X consists ofAXI bus, AHB bus, and APB bus to optimize the performance requirements.Internal IPs are connected to appropriate bus systems to meet their I/Obandwidth and operating performance. When they are attached to AXI bus or AHBbus, the operating speed can be up to maximum 133MHz. While they are attachedto APB bus, the maximum operating speed can be up to 66MHz. Moreover, the busspeed between AHB and APB has high dependency to synchronize data transmission.Figure 3-5 illustrates the part of bus clock generation to meet therequirements of bus system clocks.

HCLKx2用于两个DDR操控器,DDR0、DDR1,最高可到达266MHZ,每个DDR操控器能够独自操控,以用来下降功耗。一切的AHB总线上的时钟是由DIVhclk分频得来的,相同,也能够独自操控来下降功耗。HCLK_GATE寄存器来装备HCLKx2和HCLK。

APB总线与AHB总线相似,可是留意:在AHB和APB总线之间的频率比有必要隔着一个偶数值,例如:假如DIVhclk是1,那么DIVpclk有必要是1、3…..,不然,则不能传输数据。

Low-speed interconnection IPs transfer data through APB bus system.APB clocks of them are running at up to 66MHz as described in the above sectionand generated from DIVPCLK clock divider. They are also masked using PCLK_GATEregister. As described, the frequency ratio between AHB clock and APB clockmust be an even integer value. For example, if DIVHCLK has 1 of CLK_DIV0[8],then DIVPCLK must be 1, 3, … of CLK_DIV0[15:12].Otherwise, the IPs on APB bussystem cannot transfer data correctly.

在AHB总线上的JPEG和安全子体系不能运行在133MHz。AHB总线用DIVjpeg和DIVsecur为它们独自发生时钟信号,因而它们与APB之间的频率也要隔着一个偶数。

APLL独自用于ARM核,其值不作束缚。

其他时钟,用的时分检查手册即可。

2)MFC时钟

3)camera I/F(接口)时钟

4)显现时钟(POST、LCD和scaler

5)音频时钟(IIS和PCM)

6)UART、SPI、MMC时钟

7)IrDA 和USBHOST时钟

8)时钟的开关操控

能够经过操控HCLK_GATE、PCLK_GATE、SCLK_GATE。

9)时钟的输出

有一个时钟输出端口,发生内部时钟,用于中止或调试。