引 言

跟着计算机技能的开展和广泛运用,尤其是在工业操控范畴的运用越来越广泛,计算机通讯显的尤为重要。串行通讯尽管使设备之间的连线大为削减,但随之带来串/并转化和位计数等问题,这使串行通讯技能比并行通讯技能更为杂乱。串/并转化可用软件完结,也可用硬件完结。用软件完结串行传送大多选用循环移位指令将一个字节由高位到低位(或低位到高位)一位一位顺次传送,这种办法尽管简略但速度慢,并且很多占用CPU的时刻,影响体系的功用。更为便利的完结办法是用硬件,现在微处理器串行接口常用的LSI 芯片是UART(通用异步收发器)、USART(通用同步异步收发器)和ACIA(异步通讯接口适配器)等。不论是哪一种芯片,它们的一种基本功用是完结串/并转化。正是这些串行接口芯片弥补了串行通讯较为杂乱这一缺点。本文运用EDA(电子规划主动化)技能,依据FPGA(现场可编程门阵列)/CPLD(杂乱可编程逻辑器材)规划与完结UART。

1、 总体规划

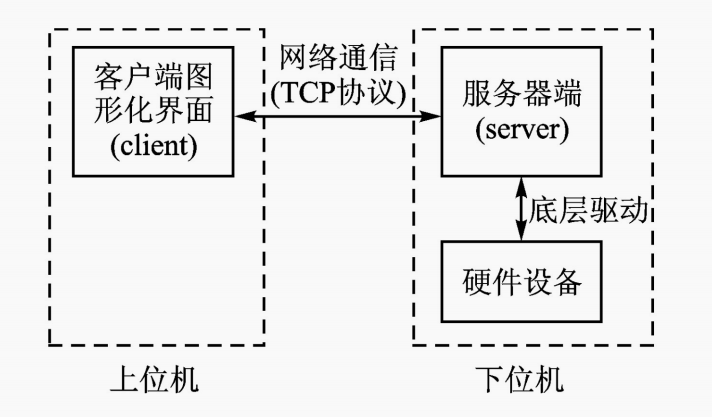

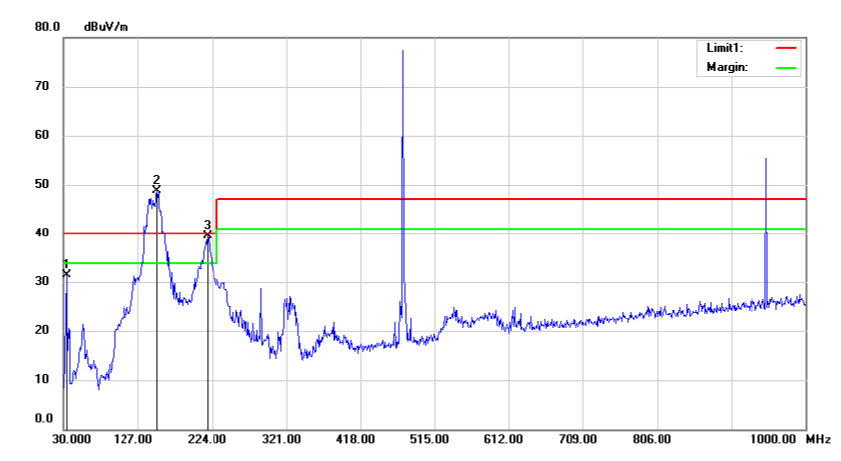

整个规划包括两部分:依据FPGA的UART的规划和依据VB6.0的上位机程序规划。UART的规划选用模块化的规划思维,可分为3个模块:FPGA数据发送模块、FPGA波特率发生器操控模块及数据接纳模块。上位机程序选用VB 6.0的Mscomm控件,可分为画面规划和功用规划两部分。串口选用规范的RS-232协议,首要参数挑选为:波特率9 600 bit/s,8位有用位,无奇偶校验位,1位中止位。

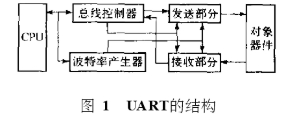

2、 UART的结构和帧格局

UART首要包括接纳器和发送器。从异步接纳输入信号SIN接纳到的异步信号经过接纳器完结串行/并行的转化,构成异步数据帧;发送器将CPU宣布的8位数据进行并行/串行转化,从SOUT发送出去。功用包括微处理器接口、TBR(发送缓冲器)、TSR(发送移位存放器)、帧发生、并转串、RBR(接纳缓冲器)、RSR(接纳移位存放器)、帧发生、串转并。UART的结构如图1所示。

UART的帧格局包括线路闲暇状况(idle,高电平)、开端位(start bit,低电平)、5位~8位数据位(da-ta bits)、校验位(parity bit,可选)和中止位(stop bit,位数可为1、1.5、2位)。这种格局是由开端位和中止位来完结字符的同步。UART内部一般有装备存放器,能够装备数据位数(5位~8位)、是否有校验位和校验的类型、中止位的位数(1,1.5,2位)等设置。

3、 UART的规划与完结

UART是广泛运用的串行数据传输协议。UART答应在串行链路进步行全双工的通讯。串行外设运用RS-232-C异步串行接口,一般选用专用集成电路即UART完结。如8250、8251、NS16450等芯片都是常见的UART器材,这类芯片现已适当杂乱,有的含有许多辅佐的模块(如FIFO),有时不需求运用完好的UART的功用和这些辅佐功用,或许运用了FPGA/CPLD,那么就能够将所需求的UART功用集成到FPGA内部。运用VHDL将UART的中心功用集成,然后使整个规划愈加紧凑、安稳且牢靠。

下面别离规划UART的3个模块(发送器、接纳器和波特率发生器),并给出其仿真成果。

3.1 发送器规划

UART串行发送器模块框图如图2所示。DIN为8位数据,其他为1位。

从图2的框图能够看出,串行发送器中包括有一个8位THR(发送坚持存放器)和TSR(发送移位存放)。复位时,引脚TRE为高电平。当数据载入到TSR之后,引脚TRE变为低电平。发送结束,TRE变为高电平。当侦测到输入WRN变为低电平时,主动使能串行数据发送进程。首要传送1位的开端位(逻辑电平0),一起THR中的数据主动地并行载入到TSR中。然后,定长的数据位从TSR中移出,接着是校验位。最终,发生中止位(逻辑电平1),标志着一帧的结束。串行数据帧将以内部时钟频率的1/16传送。假如THR中内容不空,当一个串行数据帧传送结束后,紧接着发送下一个数据帧。这种主动的流程使得数据帧以背靠背的办法发送,提高了数据传输的带宽。当没有数据发送时,SDO引脚坚持高电平。

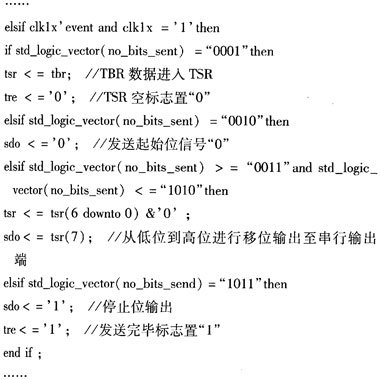

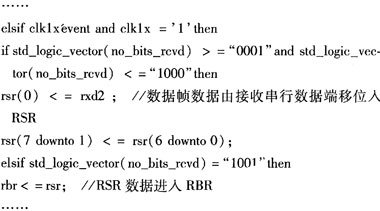

发送器每隔16个时钟周期输出1位,次第遵从1位开端位、8位数据位(假定数据位为8位)、1位校验位(可选)、1位中止位。引进发送字符长度和发送次第计数器no_bits_sent,完结的部分VHDL程序如下:

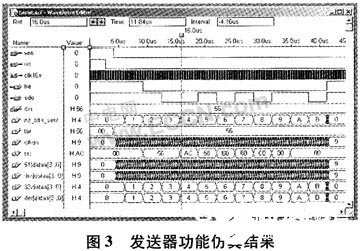

发送器功用仿真成果如图3所示。并行输入DIN十六进制数56,WRN输入由1变为0,肩动发送程序,计数器开端计数,串行输出SDO为0010101101,发送结束,TRE变为高电平。开端位0,8位数据位,1位中止位,证明了发送模块的正确性。

3.2 接纳器规划

UART串行接纳器模块框图如图4所示。DOUT为8位数据,其他为1位。接纳器包括一个8位RBR和RSR。RBR的状况能够经过引脚DATA_READY米标明。当RBR中的数据有用时,DATA_READY变为高电平,向CPU标明能够取同数据。

本规划只需求完结简略的收发功用,故未规划检错程序,程序在侦测到开端位后,计16个时钟周期,便开端接纳数据,移位输入RSR,最终输出数据DOUT。还要输出一个数据接纳标志信号标志数据接纳完。完结的部分VHDL程序如下:

接受器功用仿真成果图略。串行输入RXD为0010101101,每一位占16个时钟周期,一旦检测到输入RXD为0,计数器开端计数,开端接纳数据,接纳结束,标志位变为高电平。仿真成果证明了接纳模块的正确性。

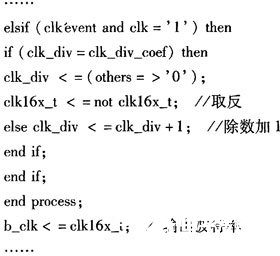

3.3 波特率发生器的规划

UART的接纳和发送是依照相同的波特率进行收发的。波特率发生器发生的时钟频率不是波特率时钟频率,而是波特率时钟频率的16倍,意图是为在接纳时进行精确地采样,以提出异步的串行数据。依据给定的晶振时钟和要求的波特率算出波特率分频数。完结的部分VHDL程序如下:

波特率功用仿真成果图略。输入频率为20 MHz,波形周期为50 ns,20 MHz/(9 600 bit/s×16 bit)=130,由仿真成果可知输出波形的半个周期为65倍的输入时钟周期,然后证明了波特率发生器模块的正确性。

4、 上位机程序规划

本文运用VB 6.0进行上位机程序的规划,完结PC与FPGA的串行通讯。下面是1个上位机收发测验通讯程序的规划进程,经过该程序能够与FPGA进行串行通讯。波特率默认值是“9600,N,8,1”,其意为所运用的通讯端口是以9 600 bit/s的速度传输,不作字符校验,每次的数据是8位,而中止位是1位。波特率(单位为bit/s)可为110、300、600、1200、2400、9 600、14 400、19 200、28 800。校验位为:E偶校验,N无校验,O奇校验,S空白。正确的数据位值有:4、5、6、7、8(默认值)。正确的中止位值有:1(默认值)、1.5、2。

将UART的程序编译、仿真后,下载到FPGA的EPlK30TC144-3芯片上。引进20 MHz的晶振频率;发送使能端和复位端别离接一个开关;状况输出标志TRE和DATA-READTY别离接一个二极管,指示状况;设置波特率为“9 800,N,8,1”。串行数据帧的格局为:开端位0,8位数据位,无校验位,1位中止位。将UART的串行发送、接纳端口别离与计算机的RS-232的串行接纳、发送端口衔接,以便与PC机进行串行通讯;并行输入DIN接入并行输出DOUT;连好线后,履行发送测验程序。

5、 结束语

在完结FPGA与PC的串行通讯中,将程序下载到芯片中验证规划的正确性,现在还没有更好的东西能够在下载后实时地对FPGA的作业情况和数据进行剖析。经过串行通讯,能够向FPGA发操控指令让其履行相应的操作,一起把需求的数据经过串口发到PC进步行相应的数据处理和剖析,以此来判别FPGA是否按规划要求作业。本文以UART为要点评论了FP-GA与上位机串行通讯的完结办法。选用高档言语VB完结了上位机与FPGA的通讯。

责任编辑:gt